,1

Изобретение относится к области вычислительной техники и может быть использовало при проектировании арифметических устройств дифровых вычислительных машин, использующих систему счислен1ия в остаточных классах.

Известно арифметическое устройство в системе остаточных кл1ассов, содержащее приемный регистр, соединенный ,с первым дешифратором, регистр результата, соеднненн1ЫЙ через второй дешифратор с матрицей для запоминания результатов операций.

Предлагаемое устройство отличается тем, что оно содержит схему преобразования в дополнительный код, входами подключенную к первому дешифратору, а выходами - к матрице запоминания результатов операций, и схему выдачи результатов операций, подключенную к выходам матрицы запоминания результатов операций.

Известные решения для каждой операции, выполняемые данным арифметическим устройством, требуют наличия отдельной запоминающей матрицы результатов данной операции, а предлагаемое - только одной запоминающей матрицы. Прн этом указанное операции в отличие от противопоставляемых решений выполняются над алгебраическим диапазоном исходных величин.

Это обеспечивает упрощение схемы и повышение быстродействия работы арцфметического устройства в системе счисления в остаточных классах.

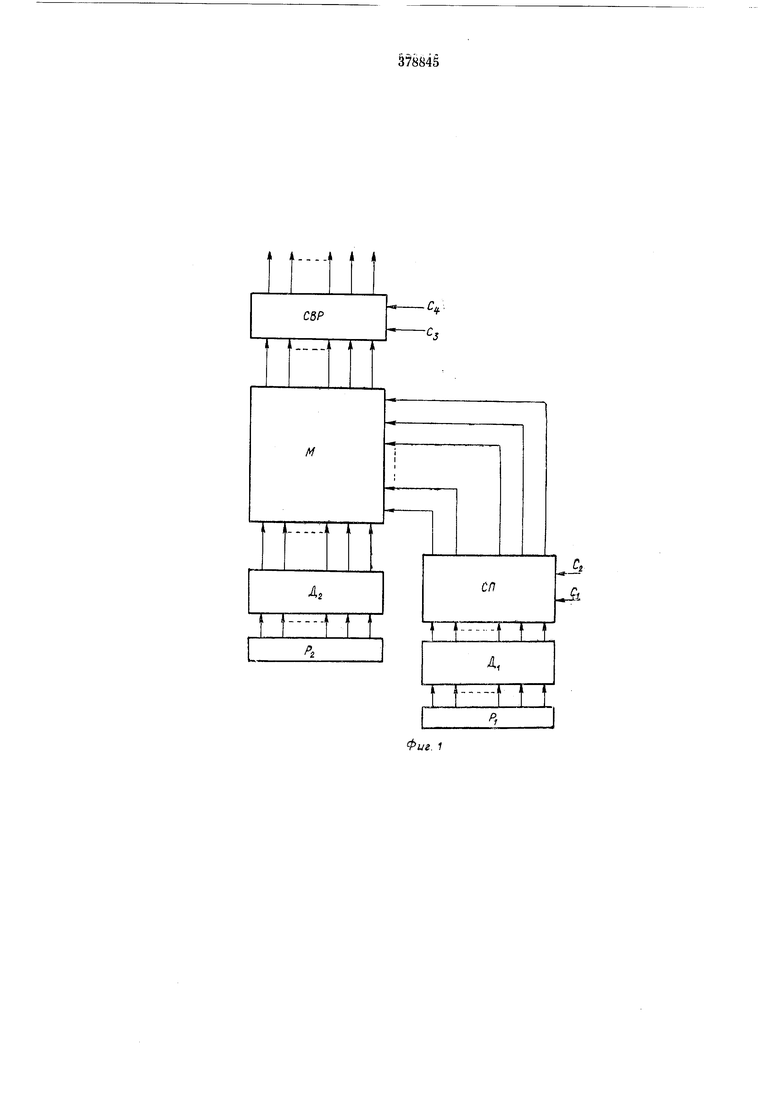

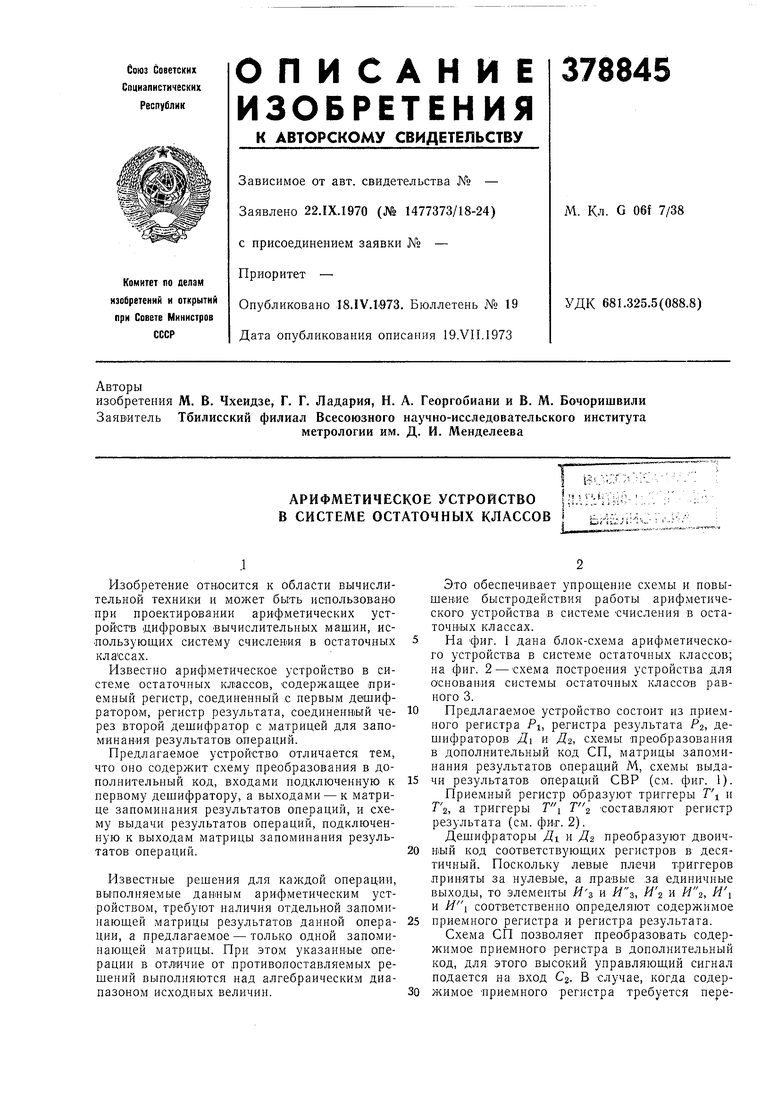

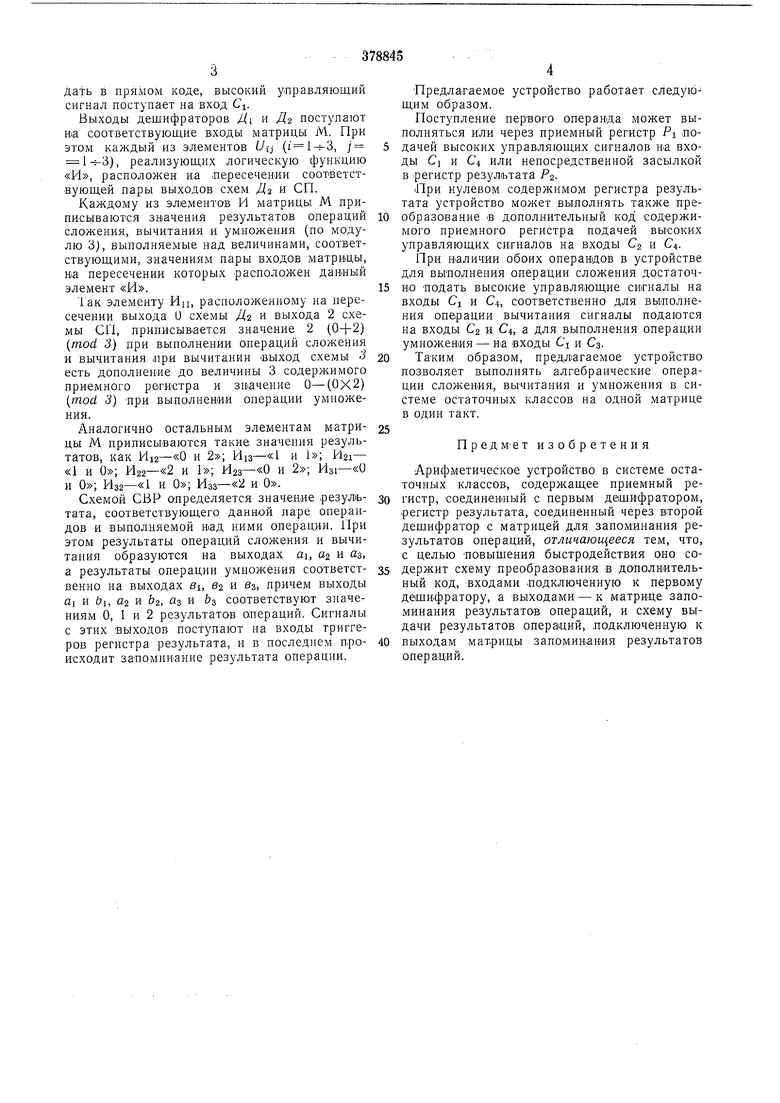

Па фиг. 1 дана блок-схема арифметического устройства в системе остаточных классов; на фиг. 2 - схема построения устройства для основания системы остаточных классов равного 3.

Предлагаемое устройство состоит из приемного регистра PI, регистра результата PZ, дешифраторов Ml и Д2, схемы преобразования в дополнительный код СП, матрицы запоминания результатов операций М, схемы выдачи результатов операций СВР (см. фиг. 1).

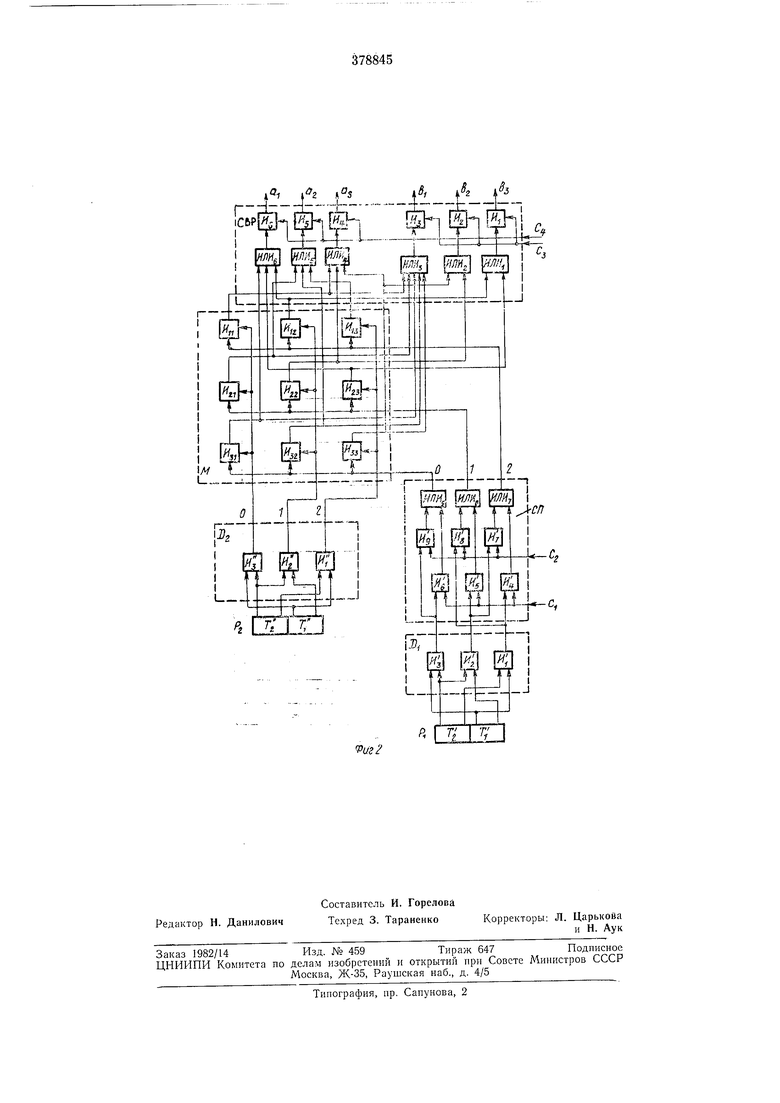

Приемный регистр образуют триггеры Т и

Tz, а триггеры Т составляют регистр

результата (см. фиг. 2).

Дещифраторы Дх и Да преобразуют двоичный код соответствующих регистров в десятичный. Поскольку левые плечи триггеров приняты за нулевые, а правые за единичные выходы, то элементы Яз и , И и И, Ml и соответственно определяют содержимое

приемного регистра и регистра результата.

Схема СП позволяет преобразовать содержимое приемного регистра в дополнительный код, для этого высокий управляющий сигнал подается на вход Cz. В случае, когда содержимое приемного регистра требуется передать в прямом коде, высокий управляющий сигнал поступает на вход С. Выходы дешифраторов //i и Да поступают Hia соответствующие В|Ходы матрицы М. При этом каждый из элементов Uij (, j 1-7-3), реализующих логическую функцию «И, расположен на (Пересечении соответствующей пары выходов схем Дз и СП. Каждому из элементов И матриды М приписываются зн ачения результатов операций ел ожения, вычитания и умножения (по модулю 3), выполняемые над величинами, соответствующими, значениям пары входов матрицы, Hia пересечении которых -расположен данный элемент «И. 1ак элементу Иц, расположенному на пересечении выхода О схемы Да и выхода 2 схемы СП, приписывается значение 2 (O-f-2) (mod 3) при выполнении операций сложения и вычитания атри вычитании выход схемы 3 есть дополнение до величины 3 содержимого приемного регистра и зн1ачение О-(0X2) (mod 3) При выполнении операции умножения. Аналогично остальным элементам матрицы М приписываются такие значения результатов, как И12-«О и MIS-«1 и Mai- «1 и Ига-«2 и Иаз-«О и Из1-«О и Иза-«1 и Изз-«2 и О. Схемой СВР определяется значение результата, соответствующего данной паре операндов и выполняемой над ними операции. При этом результаты операции сложения и вычитания образуются на выходах ai, а и аз, а результаты операции умножения соответственно на выходах ej, 02 и вз, причем выходы ui и &1, аа и &2, «3 и Ьз соответствуют значениям О, 1 и 2 результатов операций. Сигналы с этих ВЫХОДОВ поступают на входы триггеров регистра результата, и в последнем происходит запоминание результата операции. Предлагаемое устройство работает следующим образом. Поступление первого операнда может выполняться или через приемный регистр PI лодачей высоких управляющих сигналов на входы Ci и С4 или непосредственной засылкой в регистр результата PZ. Лри нулевом содержимом регистра результата устройство может выполнять также преобразование в дополнительный код содержимого приемного регистра подачей высоких управляющих си-гналов на входы Сг и Ct. При н аличии обоих операндов в устройстве для выполнения операции сложения достаточно Подать высокие управляющие сигналы на входы GI и С4, соответственно для выполнения операции вычитания сигналы подаются на входы Са и Ct, а для выполнения операции умножен1ия - на входы Cl и Сз. Таким образом, предл агаемое устройство позволяет выполнять алгебраические операции сложения, вычитания и умножения в системе остаточных классов на одной матрице в один такт. Предм-ет изобретения Арифметическое устройство в системе остаточных классов, содержащее приемный регистр, соединенный с первым дешифратором, .регистр результата, соединенный через второй дешифратор с матрицей для запоминания результатов операций, отличающееся тем, что, с целью -повышения быстродействия оно содержит схему преобразования в дополнительный код, входами подключенную к первому дешифратору, а выходами-к матрице запоминания результатов операций, и схему выдачи результатов операций, .подключенную к выходам матрицы запоминания результатов операций.

Л,

СП

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРОННАЯ КЛАВИШНАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1973 |

|

SU395837A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 1972 |

|

SU419891A1 |

| Арифметическое устройство | 1976 |

|

SU664171A1 |

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| Сумматор по модулю | 1982 |

|

SU1134939A1 |

л,

4--- --4-i..-..

ЙЬ ih Й-П № Й

P

I . /y I

Авторы

Даты

1973-01-01—Публикация