to

О5

4

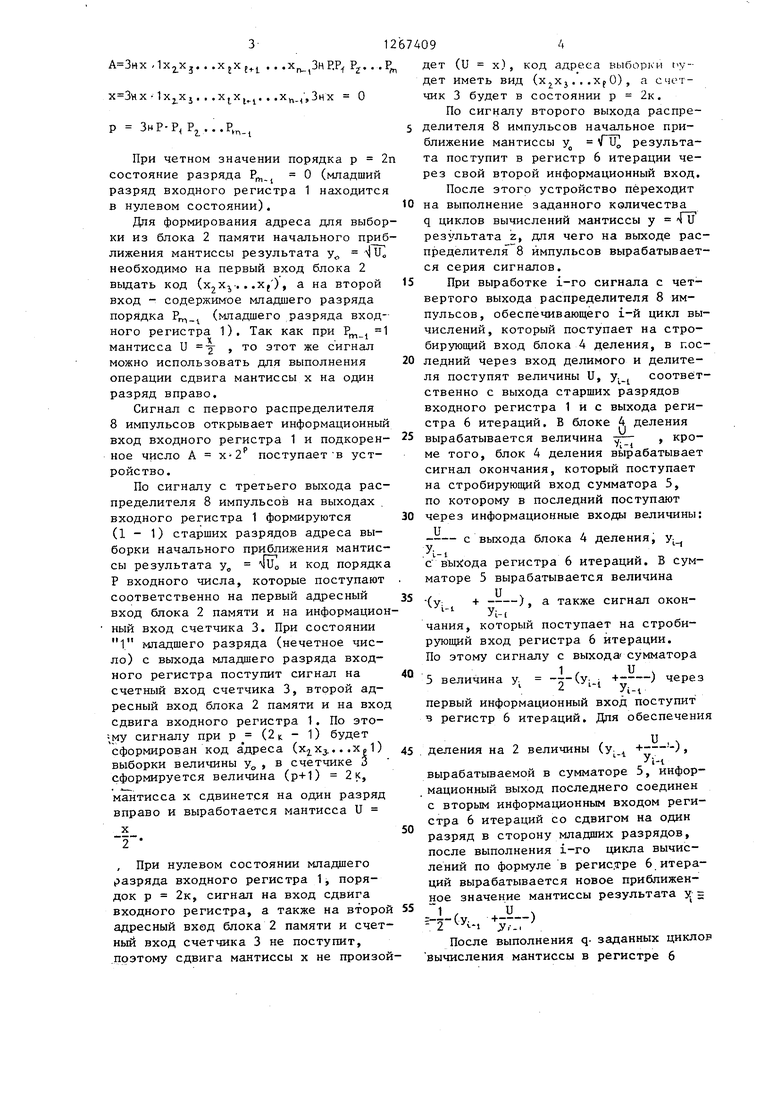

О СО 1 Изобретение относится к зычислительной технике и может быть использовано в специализированных функциональных преобразователях, Цель изобретения - повышение быст родействия вычисления числами с плавающей запятой за счет сокращения числа итерации. На чертеже представлена функциональная схема устройства. Устройство для вычисления квадратного корня содержит входной регистр 1, блок 2 памяти опорных значений мантисс, счетчик 3,, блок 4 деления, сумматор 5, регистр 6 итерации, выходной регистр 7, распределитель 8 импульсов. Устройство работает следующим образом.

Пусть и - мантисса входного числа А с четным порядком, равным р 2к, тогда

А х-2

(де и X при порядке подкоренного числа А;

V

при порядке р - (2к - 1).

В этом случае подкоренное число А в формате с плавающей запятой примет вид

гх

А и-2 Тогда представим алгоритм вычислений следующим образом 2 0 2 у;2 2,: у где А - число, из которого извлекается квадратный корень, точное значение результата очередной номер цикла вычислений - приближенное значение резул тата перед выполнением i-r цикла вычислений Z. - приближенное значение резу тата после выполнения i-ro цикла вычислений. Для обеспечения высокого быстродействия в устройстве используется блок 2 памяти, в котором хранятся .значения мантисс результата щгя опо ных значений U мантиссы U. Подкоренное (входное) число А х-2 , в формате с плавающей

0,,5/L i ,0, ,00/L

2

Калодый интервал изменения величины и имеет нижнюю и верхнюю границу соответственно Иц , Uj, ., дпя которых квадратные корни соответственно равны у xfu,; у Ub.

Опорное значение у и„ для каждого интервала выбираем на основе принципа равенства относительных ошибок для граничных значений у, ; у , т.е. выбираем из соотношения:

Z&..

-LZilZu-- 2iy« У« У 9 запятой имеет мантиссу к, область изменения которой 0,5 х 1,0,а мантисса U изменяется в пределах 0,25 и 1,00. Для простоты формирования адреса выборки квадратного корня у U из опорного значения мантиссы U, область изменения величины U разобьем на L 2 (L - объем памяти) интервалов, при зтом для поддиапазонов 0,25 «и 0,50- 0,50 U 1 ,00 размеры этих интервалов одинаковы и равны соответственно: Максимальное значение относительной ошибки &« начального приближения у при хранении в блоке 2 памяти L 2 чисел не поевосходит величины Ч 2- Так KciK после каждого цикла вычислений по и терационной формуле количество верных разрядов увеличивается не менее., чем в два раза, то послевыполнения q циклов относительная ошибка результата z. -(fvO-2 r(...2 я Данную формулу удобно использовать для ориентировочного определения количества циклов вычислений q и емкости блока 2 пгьмяти L 2 , необходимых для обеспечения заданной точности нахож,цения результата Представим код входного числа А х-2 в формате с плавающей запятой , x ЗнРР P.,. .X jX . .х.;,3нх 0 p ЗнР-Р, P, При четном значении порядка p состояние разряда Р О (младший разряд входного регистра 1 находитс в нулевом состоянии). Для формирования адреса для выбо ки из блока 2 памяти начального при лижения мантиссы результата у -{v необходимо на первый вход блока 2 выдать код (. . .Xf), а на второй вход - содержимое младшего разряда порядка РГ (младшего разряда вход ного регистра 1). Так как при Р,„ мантисса U у , то этот же сигнал можно использовать для выполнения операции сдвига мантиссы х на один разряд вправо. Сигнал с первого распределителя 8 импульсов открывает информационны вход входного регистра 1 и подкорен ное число А х-2 поступаетВ устройство. По сигналу с третьего выхода рас пределителя 8 импульсов на выходах входного регистра 1 формируются (1-1) старших разрядов адреса выборки начального приближения мантис сы результата у Шo и код порядк Р входного числа, которые поступают соответственно на первый адресный вход блока 2 памяти и на информацио ный вход счетчика 3. При состоянии 1 младшего разряда (нечетное число) с выхода младшего разряда входного регистра поступит сигнал на счетный вход счетчика 3, второй адресный вход блока 2 памяти и на вхо сдвига входного регистра 1. По этому сигналу при р (2 к - 1) будет сформирован код адреса (... .х 1) выборки величины у , в счетчике 3 сформируется величина (р+1) 2 к, мантисса х сдвинется на один разряд вправо и выработается мантисса U При нулевом состоянии младшего разряда входного регистра 1, порядок р 2к, сигнал на вход сдвига входного регистра, а также на второ адресный вход блока 2 памяти и счет ный вход счетчика 3 не поступит. ,поэтому сдвига мантиссы х не произо . 09А дет (и х) , код адрееа выборки tiyдет иметь вид (.. .Хр 0) , а счетчик 3 будет в состоянии р 2к. По сигналу второго выхода распределителя 8 импульсов начальное приближение мантиссы у V Uo результата поступит в регистр 6 итерации через свой второй информационный вход. После этого устройство переходит на выполнение заданного количества q циклов вычислений мантиссы у TiJ результата z, для чего на выходе распределителя 8 импульсов вырабатывается серия сигналов. При выработке i-ro сигнала с четвертого выхода распределителя 8 импульсов, обеспечивающего i-й цикл вычислений, который поступает на стробирующий вход блока 4 деления, в последний через вход делимого и делителя поступят величины U, у. соответственно с выхода старших разрядов входного регистра 1 и с выхода региВ блоке 4 деления стра 6 итераций, вырабатывается величина j,- , кроме того, блок 4 деления вырабатывает сигнал окончания, который поступает на стробирующий вход сумматора 5, по которому в последний поступают через информационные входы величины: с выхода блока 4 деления i У; с вых:ода регистра 6 итераций. В сумматоре 5 вырабатывается величина / и . (У: +) , а также сигнал окончания, который поступает на стробируюш 1й вход регистра 6 итерации. По этому сигналу с выхода сумматора 5 величина у -г-(У;.; +) через iпервый информационный вход поступит в регистр 6 итераций. Для обеспечения деления на 2 величины (У;. +) вырабатываемой в сумматоре 5, информационный выход последнего соединен с вторым информационным входом регистра 6 итераций со сдвигом на один разряд в сторону младших разрядов, после выполнения i-ro цикла вычислений по формуле в регис.тре 6 итераций вырабатывается новое приближенное значение мантиссы результата у U ч 7 После выполнения q- заданных циклов вычисления мантиссы в регистре 6

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой логарифмический преобразователь | 1987 |

|

SU1425665A1 |

| Устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1336029A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Устройство для вычисления квадратного корня | 1984 |

|

SU1191908A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для извлечения квадратного корня | 1988 |

|

SU1522198A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

Изобретение может быть применено в специализированных автономных вычислителях или в качестве функционального расширителя в составе с большими ЭВМ. Целью изобретения является ускорение вычисления квадратного корня при оперировании числами с плавающей запятой. Цель изобретения достигается за счет выбора начальных приближений значений мантисс, обеспечивающих повышенную скорость сходимости итерационного процесса. Устройство содержит входной регистр 1, блок 2 памяти опорных значений мантисс, счетчик 3, блок деления 4, сумматор 5, регистр итерации 6, выходной регистр 7, распределитель импульсов 8. Устройство под действием импульсов от распределителя импульсов i 8 обеспечивает с помощью блока деле(Л С ния 4, сумматора 5 и регистра итераций вычисление квадратного корня по методу Герона. 1 ил.

| Самофалов К.Г | |||

| и др | |||

| Цифровые электронные вычислительные машины, Киев; Вища школа, 1983, с | |||

| ПАРОПЕРЕГРЕВАТЕЛЬ ДЛЯ ТРУБЧАТЫХ ПАРОВЫХ КОТЛОВ С ЭЛЕМЕНТАМИ, СОСТОЯЩИМИ ИЗ ДВУХ ПЕТЕЛЬ, ВВОДИМЫХ В ПРОГАРНЫЕ ТРУБЫ КОТЛА | 1916 |

|

SU281A1 |

| Устройство для вычисления квадратного корня | 1975 |

|

SU611208A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления квадратного корня | 1973 |

|

SU560224A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-30—Публикация

1985-06-26—Подача