К

Изобретение относится к выч :сли- тельной технике и может быть использовано в системах обмена данными в качестве устройства сопряжения различных по скоростям характерис- тикам источников и прием1даков информации.

Целью изобретения является сок-ращение аппаратурных затрат устройства.

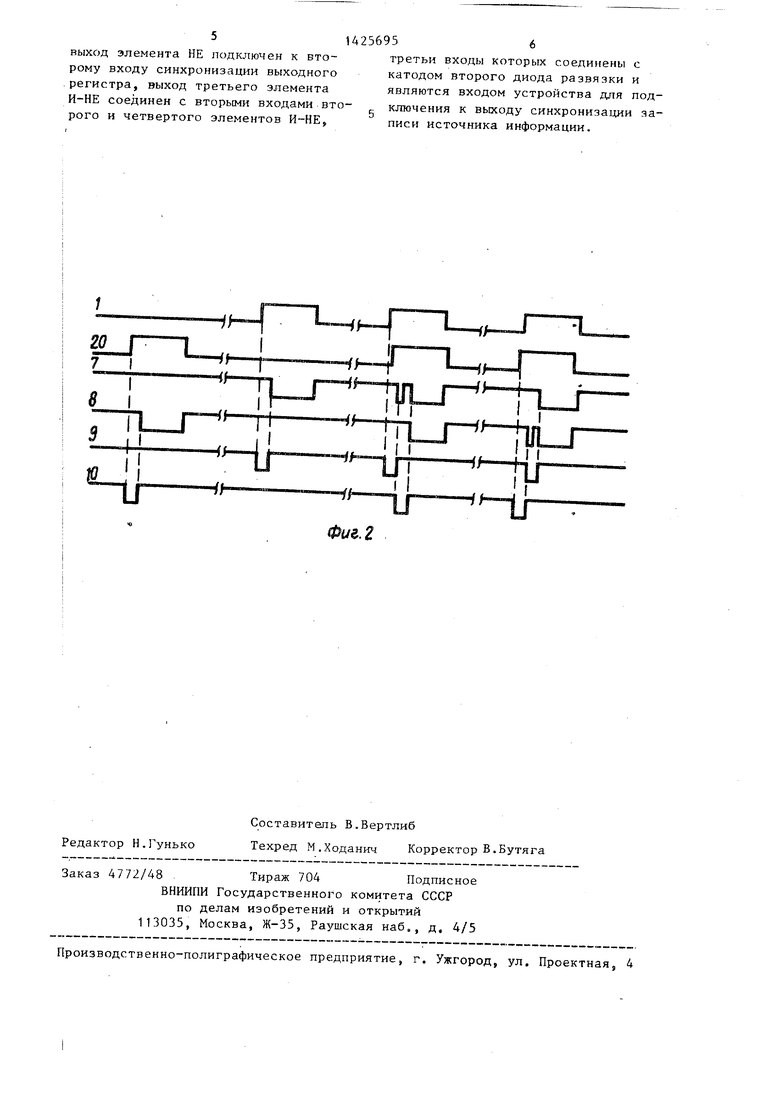

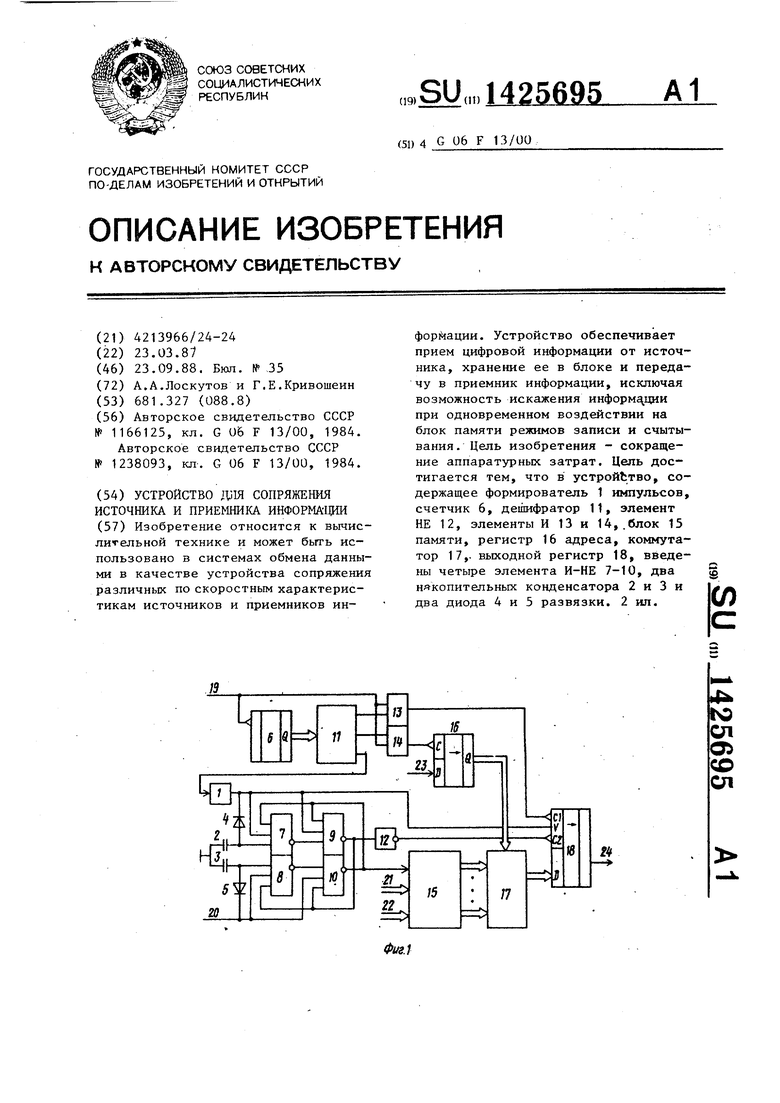

На фиг.1 изображена функционалв- ная схема предлагаемого устройства; на фиг,2 временная диаграмма формирования синхроимпульсов для записи информации в блок памяти и в выходной регистр.

Устройство содержит (фиг.1) формирователь 1 импульсов, накопительные конденсаторы 2 и 3s диоды 4 и 5 развязки,счетчик 6, элементы И- НЕ. 7 - 10, дешифратор 11, элемент НЕ 12, элементы-И 13 и 14, блок 15 памяти, регистр 16 адреса, коммутатор 17, выходной регистр 18, выходы 19 и 20 синхронизации соответственно приемника и источника информации информационный выход 21 источника информации, адресные выходы 22 и 23 соответственно источника и приемник информации, информационный вход 24

приемника информации. I

Устройство работает следующим

образом.

При включении питания устанавливаются в исходное состояние блок 15 памяти, построенный на основе регистров, и счетчик 6, На выходе формирователя 1 я на выходе 20 от источника информации присутствуют сигналы низкого уровня, в результате чего конденсаторы 2 к 3 разряжены через диоды 4 и 5 Информация, принимаемая в виде параллельного кода с выхода 21 источни:ка5, записывается в ячейку блока 15 памяти, определяемую адресным кодом за,- писи, который принимается с.выхода 22. Запись осуществляется по заднему фронту импульса, который вьфаба- тывается на выходе элемента И-НЕ 10 В момент поступления синхроимпульса с быхода 20 источника информации начинается заряд конденсатора 3 входным вытекаю цим током логического нуля элемента И-НЕ 8, в результате чего на его выходе остается сигнал высокого уровня (фиг о 2).. При отсутствии сигнала на выходе формирова

,, - а

10

15

20

25

256952

теля 1 И-НЕ 9 вырабатывает сигнал высокого уровня, а на выходе элемента И-НЕ 10 вырабатывается импульс низкого уровня, который заканчивается в том момент, когда ток заряда конденсатора 3 уменьшится до порогового значения и на выходе элемента И-НК 8 появится сигнал низкого уровня. После окончания синхроимпульса с выхода 20 источника информаьщи конденсатор 3 разряжается через диод 5.

В рассматриваемом приамере считывание инфopмa ии приемником осуществляется шестнадцатира зрядным последовательным кодом по восьмиразрядному последовательному адресному коду, принимаемому с выхода 23 приемника информации, с выхода 19 которого поступают пачки из двадцати четырех синхроимпульсов. Адресный код считьшания записывается в регистр 16 по синхроимпульсам, поступающим на вход сдв ига регистра 16 через элемент И 14, которьш открывается сигналом с выхода дешифратора 11 на время прохождения первых восьми синхроимпульсов. С выхода регистра 16 принятый код поступает на адресный вход ко1-Ф1утатора 17, который подключает к информационному входу выходного регистра 18 выход соответствующей ячейки блока 15 памяти. По переднему фронту .сигнала, поступающего на восьмом такте счетчика 6 с выхода дешифратора 11 , формирователь 1 импульсов выра- батывает сигнал разрешения параллельной записи информации в выходной регистр ТВ. Во время действия этого сигнала на выходе элемента И-НЕ 9 вырабатывается импульс (аналогично импульсу, вьграбатываемому на выходе элемента И-НЕ 10). По заднему фронту этого импульса, поступающего на регистр 18 через элемент НЕ 12, осущестапяется параллельная запись информации и на выходе регистра 18 устанавливается информация шестнадцатого разряда. Последовательная вьщача информации из выходного регистра 18 оотцествляется по заднему фронту синхроимпульсов, поступающих на вход сдвига через элемент И 13, который открывается сигналом с выхода дешифратора 11 на время прохождения последних шестнадцати импульсов пачки. На входе

30

35

40

45

50

55

1

выбора режима в это время присутствует сигнал низкого фовня, соответствующий режиму сдвига. После окончания двадцать четвертого импульса пачки счетчик 6 устанавливается в исходное состояние.

Если сигнал записи с выхода 20 источника информации приходит во время действия сигнала считывания, вырабатываемого формирователем 1 импульсов, то на время действия имЛульса низкого уровня с выхода элемента И-НЕ 9 на выходах элементов И-НЕ 8 и 10 остаются сигналы высокого уровня. Конденсатор 3 в это время остается разряженным, так как на соединенном с ним входе элемента И-НЕ 8 присутствует низкий потенциал} благодаря тому, что напряжение источника питания падает на резисторе в цепи базы многоэмит- терного транзистора элемента И-НЕ 8 за счет тока логического нуля, вытекающего с входа элемента И-НЕ 8, подключенного к выходу элемента И-НЕ 9. Во время заряда конденсатора 3, который начинается после окончания, импульса на выходе элемента И-НЕ 9, на выходе элемента И-НЕ 8 Остается сигнал высокого уровня, а на выходе элемента И-НЕ 1 вьфабатывается импульс низкого уровня, оканчивающийся в момент появления на выходе элемента И-НЕ 8 сигнала низкого уровня, когда ток заряда конденсатора 3 уменьшится до порогового значения.

На фиг.2 приведен также случай, когда сигнал считывания вьфабатывается во время действия сигнала записи. В этом случае -синхроимпульс считывания информации вьфабатьшает- ся после окончания синхроимпульса записи. Таким образом, исключается возможность искажения информации при одновременном воздействии на одну и ту же ячейку блока 15 памяти режимов записи и считывания.

Формула изобретени

Устройство для сопряжения источника и приемника информации, содержащее формирователь импульсов, счетчик, дешифратор, два элемента И, элемент НЕ, регистр адреса, выходно регистр, коммутатор, блок памяти.

5695

информационный и адресный входы которого являются соответственно входами устройства для подключения к- информационному и адресному выходам источника информации, а группа информационных выходов подключена к группе информационных входов коммутатора, соединенного адресным вхоQ дом с выходом регистра адреса, а выходом - с информационным входом выходного регистра, выход которого является выходом устройства для подключения к информационному.входу с приемника информации, вход выбора режима вьпсодного регистра подключен к выходу формирователя импульсов, а первый вход синхронизации - к выходу первого элемента И, соединенно0

0

0

го первым входом с первым входом

второго элемента И, входом счетчика и являющегося входом устройства для подключения к выходу синхронизации приемника информации,выход

5 счетчика подключен к входу дешифратора, соединенного первым, вторым и третьим выходами соответственно с входом формирователя импульсов, с вторым входом первого эл емента И и вторым входом второго элемента И, выход которого подключен к входу синхронизации регистра адреса, ин- формационньй вход которого является входом устройства для соединения с адресным выходом приемника инфор5 нации, отличакгщееся тем, что, с целью сокращения аппаратурных затрат устройства, в него введены четыре элемента И-НЕ, два накопительных конденсатора и два диода развязки, причем выходы первого и второго элементов И-НЕ подключены соответственно к первым входам третьего и четвертого элементов И-НЕ, выходы которых соединены соответ- ственно с входом элемента НЕ и входом синхронизации записи блока памяти, первые входы первого и второго элементов И-НЕ соединены соответственно с анодами первого и второго

0 диодов развязки и через первый и второй накопительные конденсаторы с шиной нулевого потенциала устройства, выход формирователя импульсов соединен с катодом первого дио5 да развязки и вторыми входами первого и третьего элементов И-НЕ, третьи входы которьк подключены к выходу четвертого элемента И-НЕ,

выход элемента НЕ подключен к второму входу синхронизации выходного регистра, выход третьего элемента И-НЕ соединен с вторыми входами второго и четвертого элементов И-НЕ,

третьи входы которых соединены с катодом второго диода развязки и являются входом устройства для подключения к выходу синхронизации записи источника информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1238093A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1166125A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1275454A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1580383A1 |

| Устройство для ввода информации | 1987 |

|

SU1529231A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1096692A1 |

| Устройство для сопряжения | 1983 |

|

SU1104498A1 |

| Устройство для сопряжения источников и приемников с магистралью | 1986 |

|

SU1363227A2 |

Изобретение относится к вычислительной технике и может быть использовано в системах обмена данными в качестве устройства сопряжения различных по скоростным характеристикам источников и приемников инфор1(Чации. Устройство обеспечивает прием цифровой информации от источника, хранение ее в блоке и передачу в приемник информации, исключая возможность искажения информации при одновременном воздействии на блок памяти режимов записи и счыты- вания. Цель изобретения - сокращение аппаратурных затрат. Цель достигается тем, что в устройЬтво, содержащее формирователь 1 импульсов, счетчик 6, дешифратор 11, элемент НЕ 12, элементы И 13 и 14,.блок 15 памяти, регистр 16 адреса, коммутатор 17,- выходной регистр 18, введены четыре элемента И-НЕ 7-10, два накопительных конденсатора 2 и 3 и два диода 4 и 5 развязки. 2 шт. Ш (Л

Ч

Фи&.2

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1166125A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1238093A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-23—Подача