Изобретение относится к вычислительной технике и может быть использовано в аппаратуре передачи и обработки информации.

Цель изобретения - повышение гибкости протокола обмена по магистрали, повышение скорости обмена за счет обеспечения идентификации своего пакета информации и возможности работы в дуплексном режиме сеанса обмена путем введения блока памяти, хранящего команды управления и коды обращения к данному интерфейсному

блоку для всех возможных но данному протоколу обмена алгоритмов, зависящих от длины и структуры пакета информации, обработки служебной и полезной частей пакета информации на потоке, разделением устройства на функционально зависимые приемный и передающий уялы, объединенные обцей адресной шиной блока памяпг команд управления, введением системной шины (обмена с перифериен ) с .iou ной инициалнзацпеи от IK гочпп ка.

оо

05

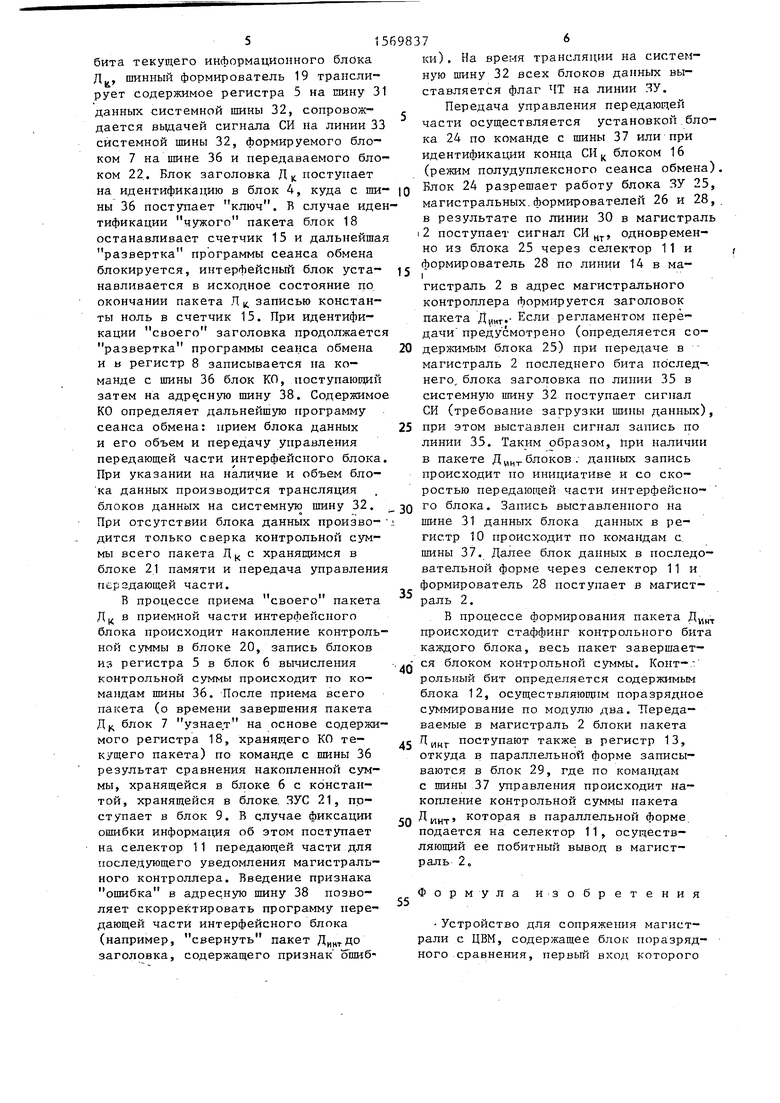

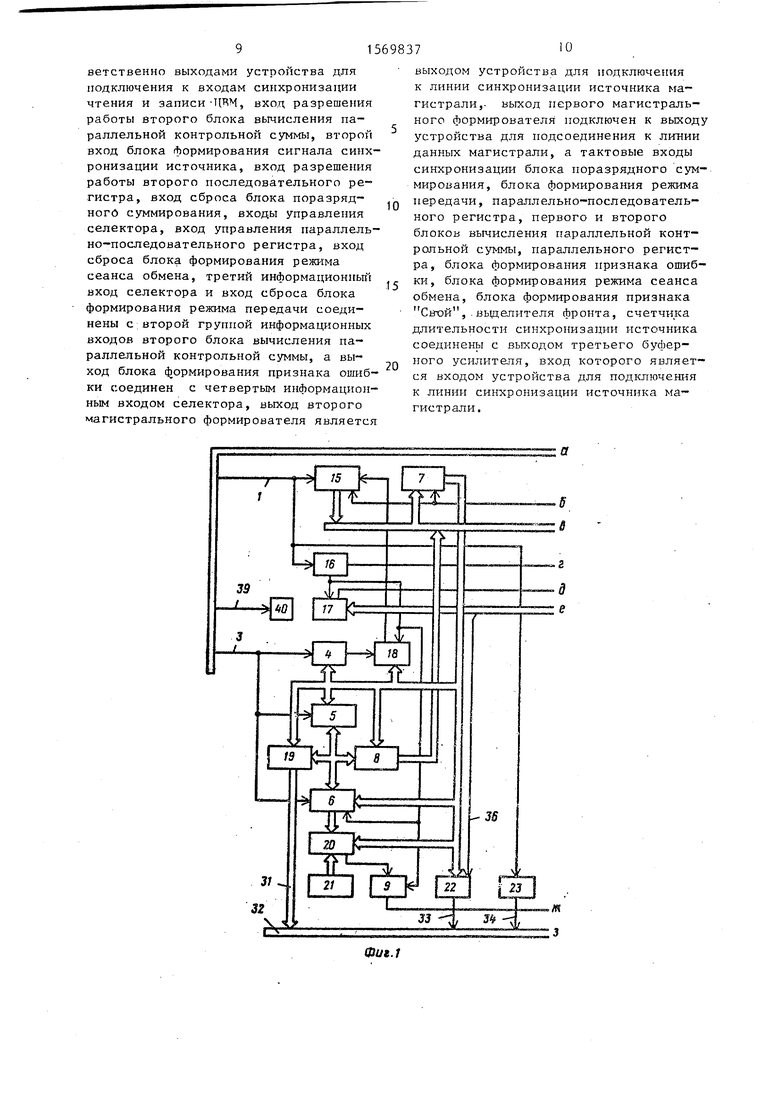

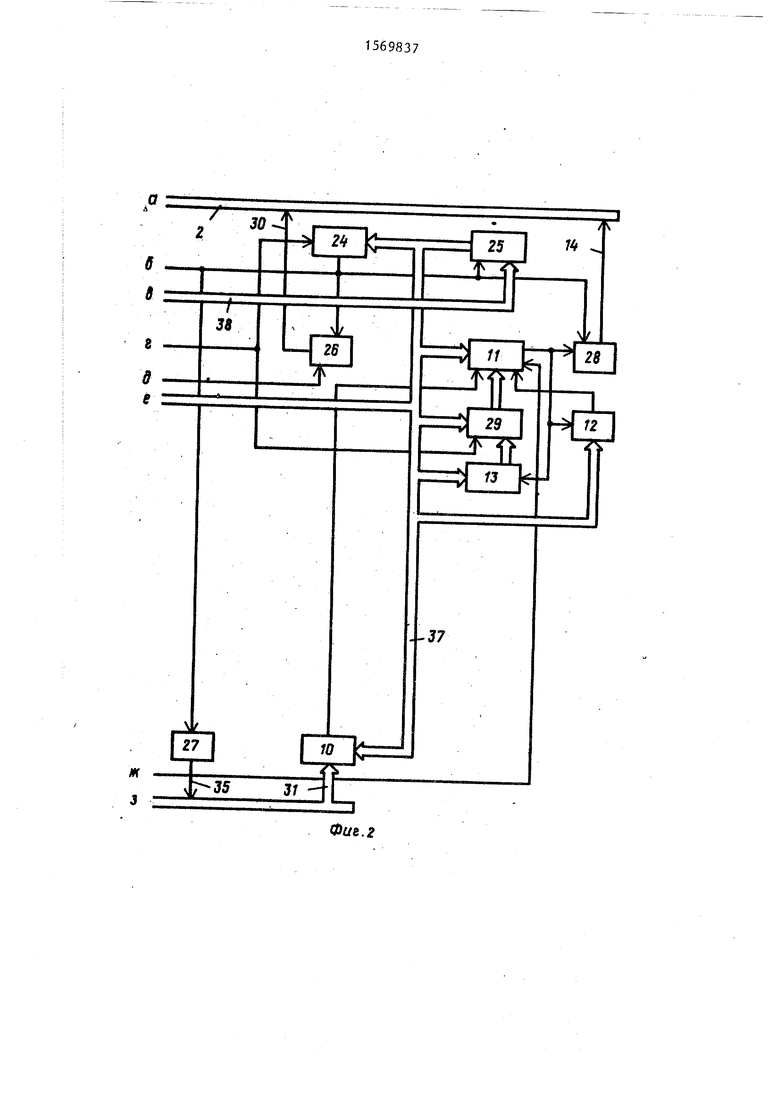

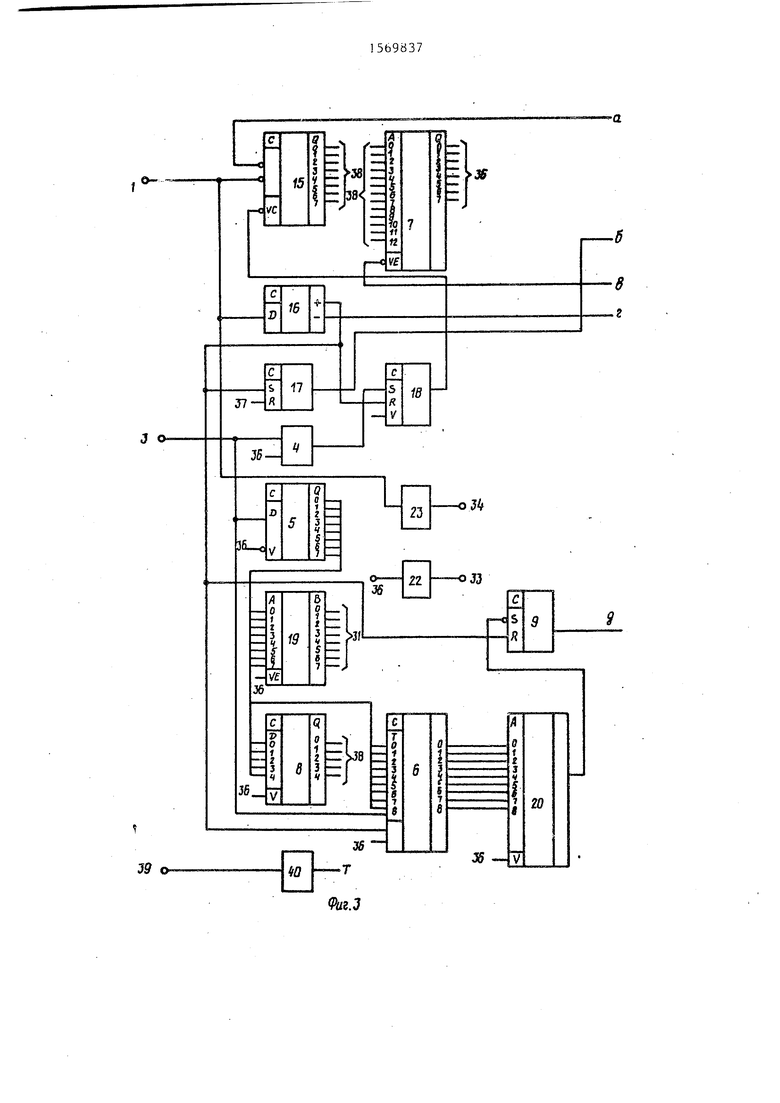

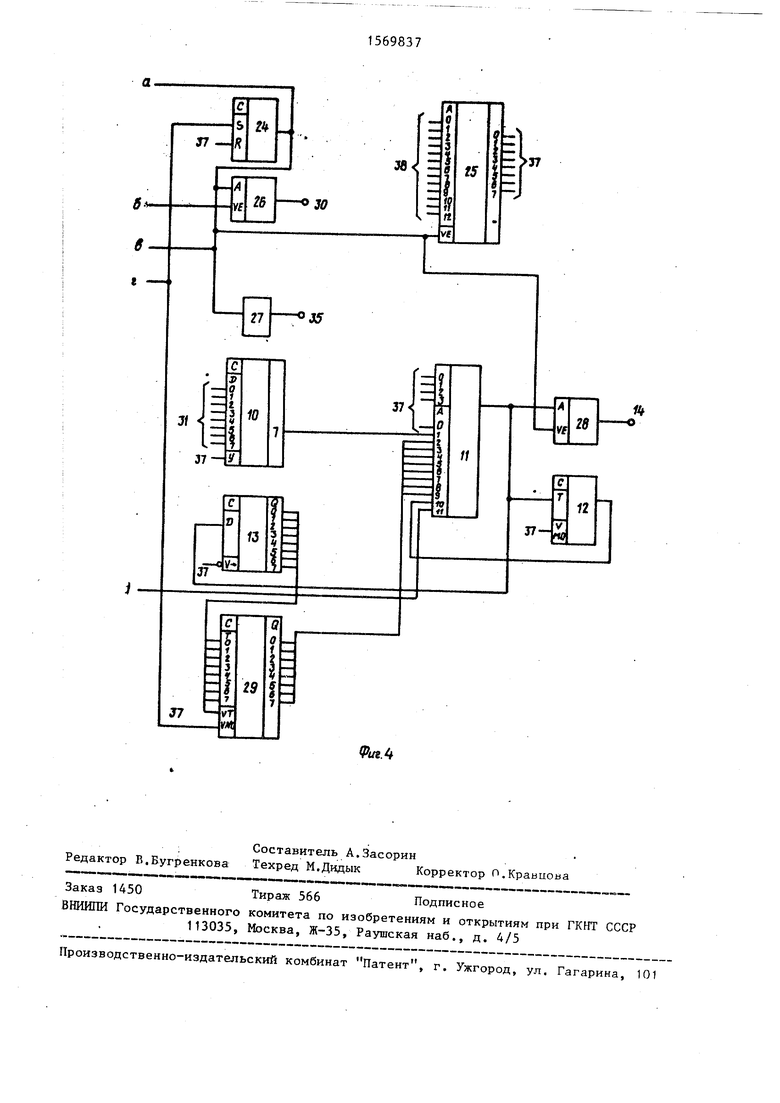

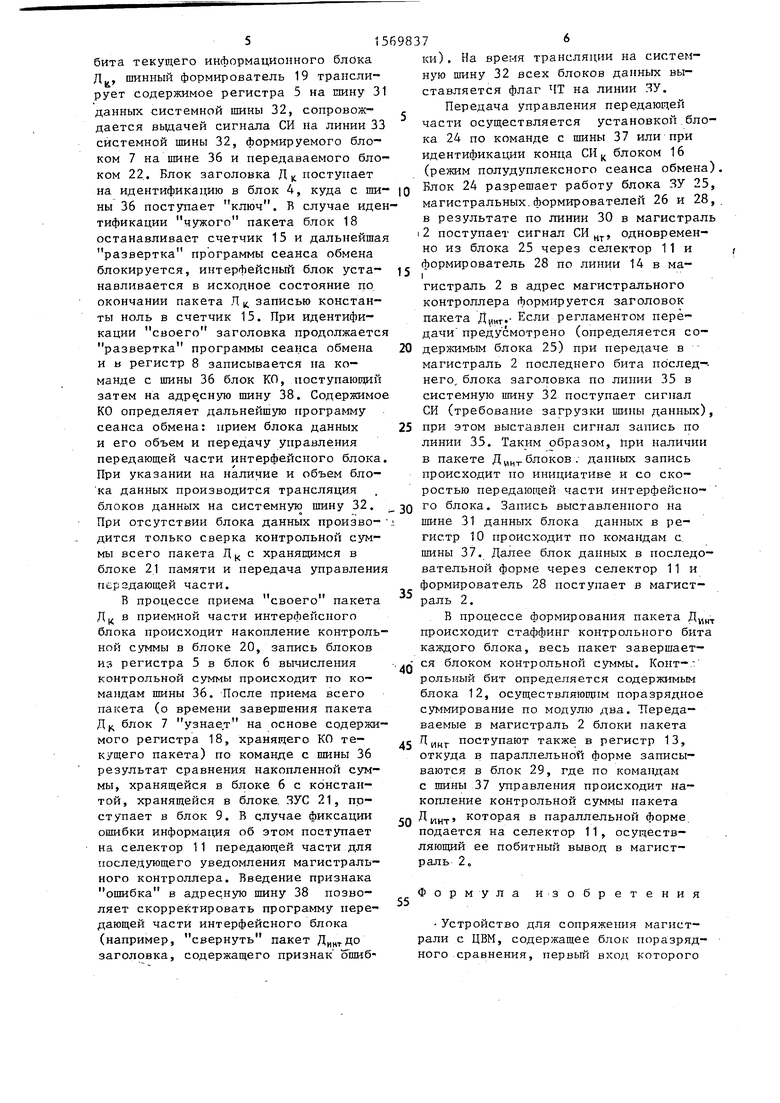

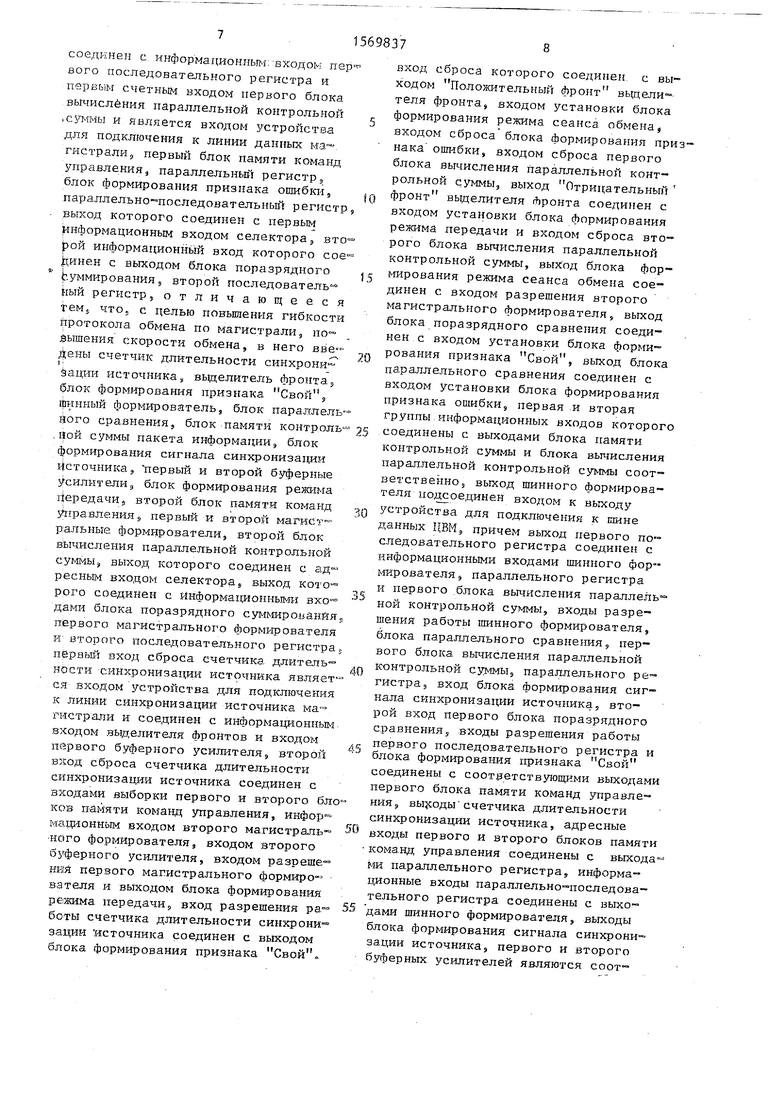

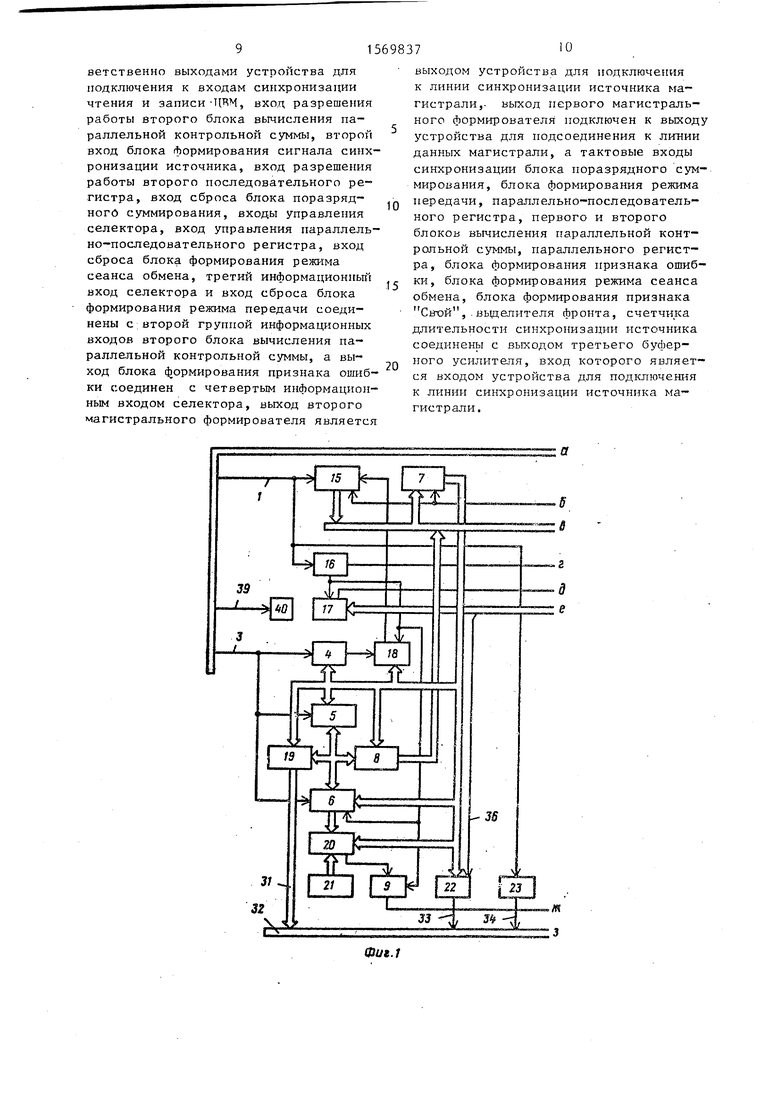

На фиг. I и 2 представлена структурная схема предлагаемого интерфейс™ кого блока; на фиг. 3 и 4 - функциональная схема возможного варианта i

реализации интерфейсного блока.

Устройство содержит линию 1 синхро™ нчзации источника магистрали 2Э линию J данных источника магистрали 2, пер- йый блок 4 поразрядного сравнения, первый последоватедьный регистр 5, первый блок 6 вычисления параллель- Ной контрольной суммы., первый блок 7 цамяти команд управления, первый па- р аллельный регистр 8, блок 9 формиро- вания признака ошибки,, параллельно Последовательный регистр 10, селектор 1t1 s блок 12 поразрядного суммирования второй последовательный регистр 13, , линию 14 данных интерфейса магистра- ли, счетчик длительности синхронизаци источника 15, выделитель 16 Фронта, блок 17 формирования режима сеанса обмена} блок 18 Формирования признака Свой, шинный Формирователь 19, блок 20 параллельного сравнения, блок 21 памяти контрольной суммы пакета, блок 22 формирования сигнала синхронизации источника, первый буферный усилитель 23s блок 24 формирования режима передачи, второй блок 25 памяти команд управления, первый магистральный Формирователь 26, второй буферный усилитель 27, второй магистральный формирователь 28, второй блок 29 вычисления параллельной контрольной суммы, линию 30 синхронизации интерфейса Магистрали 29 двунаправленную шину 31 данных системной шины 32, линию 33 синхронизации источника системной шины 32, линию 34 чтение системной шины 32s линию-запись 35 системной шины 32, шину 36 управления приемника, шину 37 управления передатчика, адресную шину 38 блоков памяти ко- манд управления, линию 39 синхрони™ здции, третий буферный усилитель 40. Устройство работает следующим образом.

По магистрали 2 от магистрального контроллера на линию 39 поступает сиг нал синхронизации Тс длительностью периода, равного длительности передачи/приема бита данных по линиям 3 и 14 магистрали 2, сигнал синхронизации может формироваться только в течение сеанса обмена. На линию 3 и 9 магистрального контроллера поступает пакет данных Дк в последо нательной форме, параллельно на ли°

нию 1 поступает сигнал синхронизации источника СИК, длительность которого равна длительности передачи пакета Д, С линии 14 в магистральный контроллер поступает пакет данных Линт, параллельно с линии 30 в магистральный контроллер поступает сигнал синхронизации интерфейса СИ нтс длительностью, равной длительности передачи пакета ЛИиг . Сигналы СИ Ит и Линт формируются синхронно сигналу Тс. Сгрук тура пакета последовательно формируемые блоки заголовка (содержит адрес интерфейсного блока), кода операции (КО) ( содержит указания на алгоритм сеанса обмена данных) и бло (или блоки) контрольной суммы (по модулю два одноименных разрядов бит) предыдущей части пакета. Структура пакета Лмнг: последовательно Нормируемые блоки заголовка (содержит адрес интерфейсного блока - корреспондента), слова состояния (содержит указание на алгоритм сеанса обмена и признак ошибки предыдущего приема Л (/ в текущем сеансе обмена данных) и блок (или блоки) контрольной суммы (по модулю два одноименных разрядов бит) предыдущей части пакета. Структура блока пакета Д к и : 8 (или кратное 8-ми)-разрядный байт полезной информации плюс бит контрольной суммы содержимого данного блока по модулю два. Результирующая сумма по модулю два одноименных разрядов всех блоков равна константе независимо от длины пакета и его содержимого.

Сеанс обмена инициирует магистральный контроллер, посылая Лк по

По началу СИК выделитель 16

СИ,

фронта устанавливает блок 17 в режим Сеанс обмена, включая таким образом формирование СИНТ в магистраль. Сигнал СИК разрешает работу счетчика 15, управляющего по адресной шине 38 блоком 7 в режиме приема (ПРИ) и блоком 25 в режиме передачи (ПРЛ). Использование раздельных блоков памяти для режимов ПРИ и ПРЛ позволяет реал .зовать дуплексный режим сеанса обмена Время начала режима ПРЛ в этом случа определяется содержимым блока КО и (или содержимым блока ПРИ) блока 25. По сигналу СИК в регистр 5 записываются последовательно блоки Дк, в параллельной форме поступающие затем в шинный формирователь 19, регистр 8 и блок 6, По командам, поступающим с шины 36 управления в течение 9-го

бита текущего информационного блока Д , шинный формирователь 19 трансли- рует содержимое регистра 5 на шину 31 данных системной шины 32, сопровож- дается выдачей сигнала СИ на линии 33 системной шины 32, формируемого блоком 7 на шине 36 и передаваемого блоком 22. Блок заголовка Д поступает на идентификацию в блок 4, куда с ши- ны 36 поступает ключ. В случае идентификации чужого пакета бпок 18 останавливает счетчик 15 и дальнейшая развертка программы сеанса обмена блокируется, интерфейсный блок уста- навливается в исходное состояние по окончании пакета Л ц записью константы ноль в счетчик 15. При идентификации своего заголовка продолжается развертка программы сеанса обмена и в регистр 8 записывается на команде с шины 36 блок КО, поступающий затем на адресную шину 38. Содержимое КО определяет дальнейшую программу сеанса обмена: прием блока данных и его объем и передачу управления передающей части интерфейсного блока. При указании на наличие и объем блока данных производится трансляция

ки). На время трансляции на системную шину 32 всех блоков данных выставляется флаг ЧТ на линии ЗУ.

Передача управления передающей части осуществляется установкой блока 24 по команде с шины 37 или при идентификации конца СИ к блоком 16 (режим полудуплексного сеанса обмена) Блок 24 разрешает работу блока ЗУ 25, магистральных формирователей 26 и 28, в результате по линии 30 в магистраль i2 поступает сигнал СИ нт, одновременно из блока 25 через селектор 11 и

формирователь 28 по линии 14 в маi

гистраль 2 в адрес магистрального

контроллера Формируется заголовок пакета Динт,- Если регламентом передачи предусмотрено (определяется содержимым блока 25) при передаче в магистраль 2 последнего бита послед-, него, блока заголовка по линии 35 в системную шину 32 поступает сигнал СИ (требование загрузки шины данных), при этом выставлен сигнал запись по линии 35. Таким образом, при наличии в пакете Динт блоков, данных запись происходит по инициативе и со скоростью передающей части интерфейсно

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приемопередачи информации с контролем ошибок | 1987 |

|

SU1425757A1 |

| Устройство для приемопередачи информации с контролем ошибок | 1985 |

|

SU1277166A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для контроля канала связи | 1987 |

|

SU1478351A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА СБОРА СЕЙСМИЧЕСКИХ ДАННЫХ | 2003 |

|

RU2244945C1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1725223A1 |

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре передачи и обработки информации. Целью изобретения является повышение гибкости протокола обмена по магистрали и повышение скорости обмена. Цель достигается за счет обеспечения идентификации "своего" пакета информации, возможности работы в дуплексном режиме, обработки служебной и полезной частей информации на "потоке". Устройство содержит блок поразрядного сравнения, два последовательных регистра, два блока вычисления параллельной контрольной суммы, два блока памяти команд управления, параллельный регистр, блок формирования признака ошибки, параллельно-последовательный регистр, селектор, блок поразрядного суммирования, счетчик длительности синхронизации источника, выделитель фронта, блок формирования режима сеанса обмена, блок формирования признака "свой", блок параллельного сравнения, блок памяти контрольной суммы пакета информации, блок формирования сигнала синхронизации источника, два буферных усилителя, блок формирования режима передачи, два магистральных формирователя. 4 ил.

блоков данных на системную шину 32. JQ го блока. Запись выставленного на

При отсутствии блока данных производится только сверка контрольной сумшине 31 данных блока данных в регистр 10 происходит по командам с шины 37. Далее блок данных в после вательной форме через селектор 11 формирователь 28 поступает в магис раль 2.

д,

хранящимся в

управлени

мы всего пакета

блоке 21 памяти и передача

пьрсдающей части.

В процессе приема своего пакета Д к в приемной части интерЛейсного блока происходит накопление контрольной суммы в блоке 20, запись блоков из регистра 5 в блок 6 вычисления контрольной суммы происходит по командам шины 36. После приема всего пакета (о времени завершения пакета Дк блок 7 узнает на основе содержимого регистра 18, хранящего КО текущего пакета) по команде с шины 36 результат сравнения накопленной суммы, хранящейся в блоке 6 с константой, хранящейся в блоке ЗУС 21, поступает в блок 9. В случае фиксации ошибки информация об этом поступает на селектор 11 передающей части для последующего уведомления магистрального контроллера. Введение признака ошибка в адресную шину 38 позволяет скорректировать программу передающей части интерфейсного блока (например, свернуть пакет Динтдо заголовка, содержащего признак сшиб5

0

5

0

5

шине 31 данных блока данных в регистр 10 происходит по командам с шины 37. Далее блок данных в последовательной форме через селектор 11 и формирователь 28 поступает в магистраль 2.

В процессе формирования пакета Динт происходит стаффинг контрольного бита каждого блока, весь пакет завершается блоком контрольной суммы. Конт-- рольный бит определяется содержимым блока 12, осуществляющим поразрядное суммирование по модулю два. Передаваемые в магистраль 2 блоки пакета П икг поступают также в регистр 13, откуда в параллельной форме записываются в блок 29, где по командам с шины 37 управления происходит накопление контрольной суммы пакета Динт, которая в параллельной форме подается на селектор 11, осуществляющий ее побитный вывод в магистраль 2„

Формула изобретения

Устройство для сопряжения магистрали с ЦВМ, содержащее блок поразрядного сравнения, первый вход которого

соединен с информационным входов лер- вого последовательного регистра и первым счетным входом первого блока вычисления параллельной контрольной .суммы и является входом устройства для подключения к линии данных из-- гистрали, первый блок памяти команд управления, параллельный регистр, блок формирования признака ошибки, параллельно-последовательный регистр, выход которого соединен с первым Информационным входом селектораэ вто рой информационный вход которого сов динен с выходом блока поразрядного суммирования5 второй последователь иый регистр, отличающееся тем5 чтоэ с целью повышения гибкости протокола обмена по магистрали, по™ вышения скорости обмена, в него вве Дены счетчик длительности синхрони зации источника,, выделитель фронта, блок формирования признака Свон шинный формирователь, блок параллель ного сравнения, блок памяти контрольНой суммы пакета информации, блок формирования сигнала синхронизации Источникаэ первый и второй буферные усилителиэ блок формирования режима передачиs второй блок памяти команд управления, первый и второй магистральные формирователи, второй блок вычисления параллельной контрольной суммы, выход которого соединен с адресным входом селектора выход кою рого соединен с Информационными вхо дами блока поразрядного суммирования первого магистрального формирователя и второго последовательного регистра первый вход сброса счетчика длитель™ ности синхронизации источника является входом устройства для подключения к линии синхронизации источника магистрали и соединен с информационным входом выделителя фронтов и входом первого буферного усилителя, второй вход сброса счетчика длительности синхронизации источника соединен с входами выборки первого и второго бл ков памяти команд управления, инфор°

мационным входом второго магистраль- ного формирователя, входом второго буферного усилителя, входом разрешения первого магистрального формиро- вателя и выходом блока формирования режима передачи, вход разрешения ра боты счетчика длительности синхрони™ зации источника соединен с выходом блока формирования признака Свой

0

- 5 «

fifi

U 5

5

0

5

вход сброса которого соединен с выходом Положительный фронт выделителя фронта, входом установки блока формирования режима сеанса обмена, входом сброса блока формирования признака ошибки, входом сброса первого блока вычисления параллельной контрольной суммы, выход Отрицательный фронт выделителя Фронта соединен с входом установки блока формирования режима передачи и входом сброса второго блока вычисления параллельной контрольной суммы, выход блока формирования режима сеанса обмена соединен с входом разрешения второго магистрального формирователя, выход блока поразрядного сравнения соединен с входом установки блока формирования признака Свой, выход блока параллельного сравнения соединен с входом установки блока формирования признака ошибки, первая и вторая группы информационных входов которого соединены с выходами блока памяти контрольной суммы и блока вычисления параллельной контрольной суммы соответственно; выход шинного формирователя подсоединен входом к выходу устройства для подключения к шине данных ЦВМ, причем выход первого последовательного регистра соединен с информационными входами шинного формирователя, параллельного регистра и первого блока вычисления параллель ной контрольной суммы, входы разрешения работы шинного формирователя, блока параллельного сравнения, первого блока вычисления параллельной контрольной суммы, параллельного регистра, вход блока формирования сигнала синхронизации источника; второй вход первого блока поразрядного сравнения, входы разрешения работы первого последовательного регистра и блока формирования признака Свой соединены с соответствующими выходами первого блока памяти команд управления, выходы счетчика длительности синхронизации источника, адресные входы первого и второго блоков памяти команд управления соединены с выхода - ми параллельного регистра, информационные входы параллельно-последовательного регистра соединены с выходами шинного формирователя, выходы блока формирования сигнала синхронизации источника, первого и второго буферных усилителей являются соответственно выходами устройства для подключения к входам синхронизации чтения и записи-ЦВМ, вход разрешения работы второго блока вычисления параллельной контрольной суммы, второй вход блока формирования сигнала синхронизации источника, вход разрешения работы второго последовательного регистра, вход сброса блока поразрядного суммирования, входы управления селектора, вход управления параллельно-последовательного регистра, вход сброса блока формирования режима сеанса обмена, третий информационный вход селектора и вход сброса блока формирования режима передачи соединены с второй группой информационных входов второго блока вычисления параллельной контрольной суммы, а выход блока формирования признака ошибки соединен с четвертым информационным входом селектора, выход второго магистрального формирователя является

0

5

0

выходом устройства для подключения к линии синхронизации источника магистрали,- выход первого магистрального формирователя подключен к выходу устройства для подсоединения к линии данных магистрали, а тактовые входы синхронизации блока поразрядного суммирования, блока формирования режима передачи, параллельно-последовательного регистра, первого и второго блоков вычисления параллельной контрольной суммы, параллельного регистра, блока формирования признака ошибки, блока формирования режима сеанса обмена, блока формирования признака Свтэй, выделителя фронта, счетчика длительности синхронизации источника соединены с выходом третьего буферного усилителя, вход которого является входом устройства для подключения к линии синхронизации источника магистрали.

д

е

#г

Фиг. г

| Бауманы П., Куртц П | |||

| и Науманн Г | |||

| Стандартные интерфейсы для цифровых измерительных систем | |||

| -М.: Мир, 1977, с.69, 72, 75, рис | |||

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

| Устройство для приемопередачи информации с контролем ошибок | 1985 |

|

SU1277166A1 |

Авторы

Даты

1990-06-07—Публикация

1988-04-07—Подача