второй блок 7 поразрядного суммирования, где завершается байт контрольной суммы контрольным битом, после чвго командный блок выдает сигнал, аннулируюпщй режим передачи, и уст1

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре передачи, приема и обработки информации.

Целью изобретения является упрощение , повышение быстродействия и информационной гибкости устройства путем обеспечения параллельной и последовательной записи и считывания информации и последовательной обработки информации с контролем ошибок.

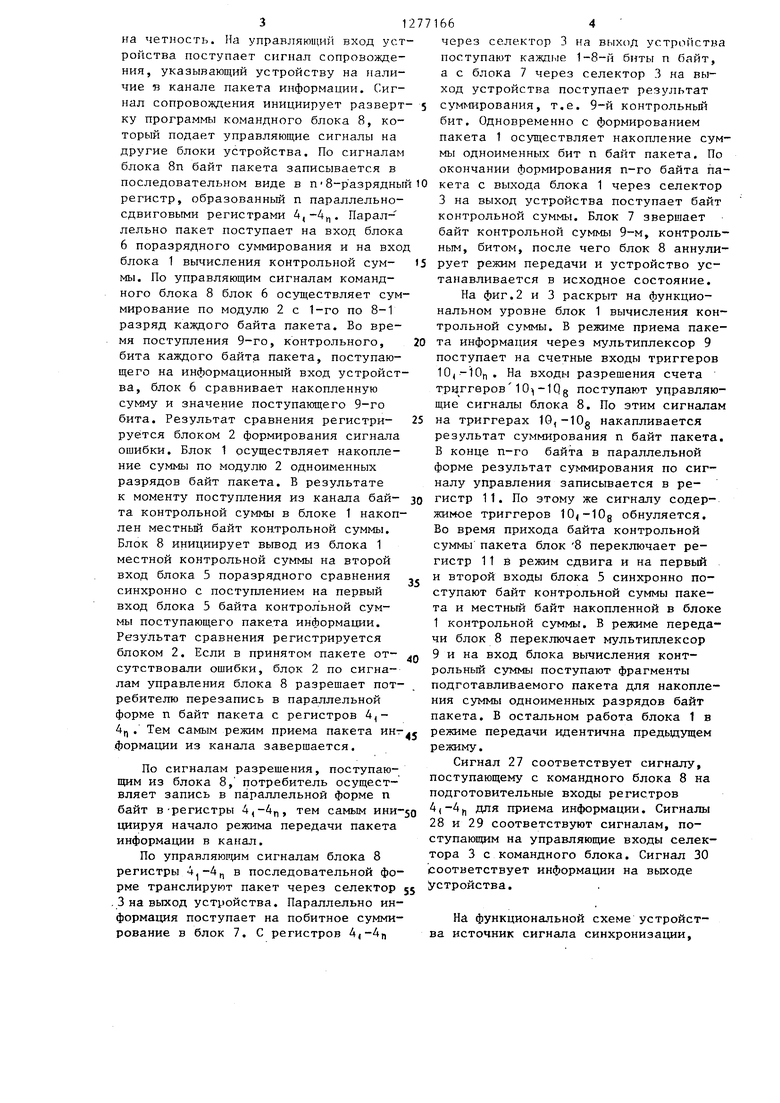

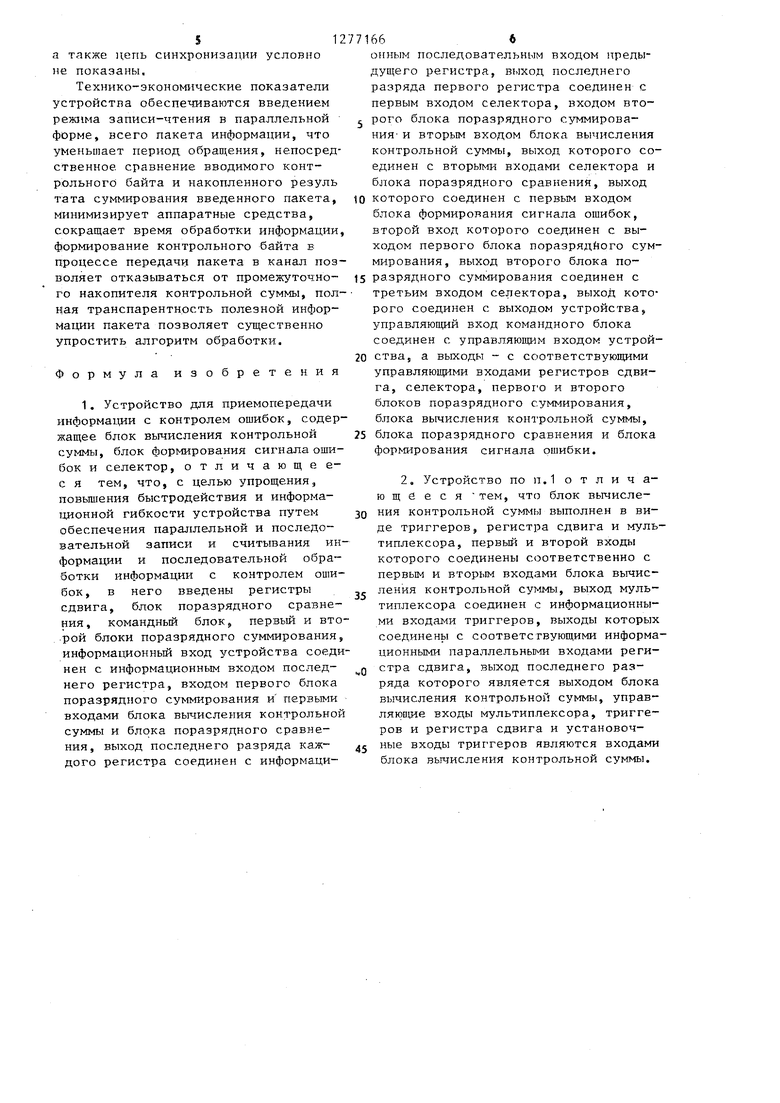

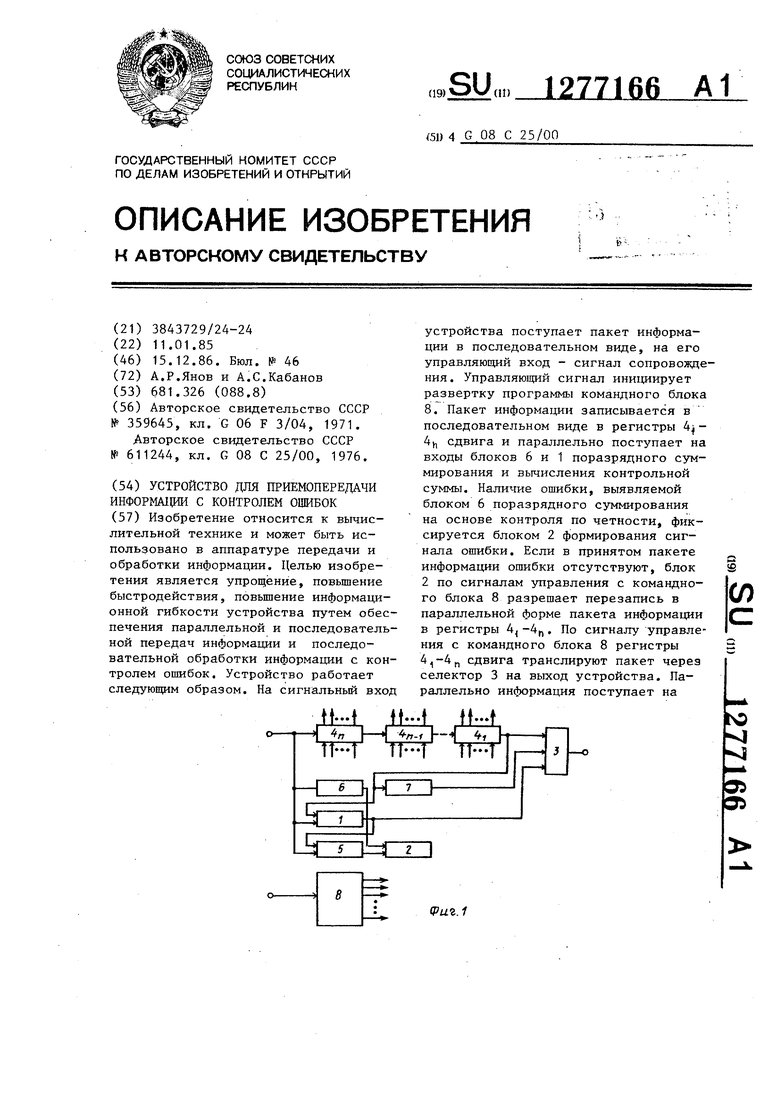

На фиг.1 изображена структурная схема устройства; на фиг.2 и 3 - его функциональная схема.

Устройство содержит блок 1 вычисления контрольной суммы, блок 2 формирования сигнала ошибки, селектор 3 регистры 4|-4у, сдвига, блок 5 поразрядного сравнения, блоки 6 и 7 поразрядного суммирования, командный блок 8, в блоке 1 вычисления контрольной суммы - мультиплексор 9,, триггеры , регистр 11 сдззига, в блоке 6 побитного суммирования - триггер 12, сумматор 13 по модулю 2, элемен И 14, в блоке 5 побитного сравнения - сумматор 15 по модулю 2, элемент И 16, в командном блоке 8 - счетчик 17, блок 18 памяти. Блок 2 формирования сигнала ошибки выполнен на триггере 19, блок 7 побитного суммирования на триггере 20.

Информационный вход устройства соединен с информационным входом пос леднего регистра 4„, входом первого блока 6 поразрядного суммирования и первыми входами блока 1 вычисления контрольной суммы и блока 5 поразрядного сравнения. Выход последнего разряда каждого регистра 4,-44 соединен с информаи 1онным последовательным входом предыдущего. Выход последнего разряда первого регистра 4, соединен с первым входом селектора 3, входом второго блока 7 поразрядного

ройство устанавливается в исходное состояние. Блок 1 вьиисления контрольной суммы содержит мультиплексор триггеры и регистр сдвига. ,1 з.п. ф-лы. 5 ил.

I

суммирования и вторым входом блока 1 вычисления контрольной суммы, .выход которого соединен с вторыми входами селектора 3 и блока 5 поразрядного .

сравнения, выход которого соединен с первым входом блока 2 формирования сигнала ошибок, второй вход которого соединен с выходом первого блока 6 поразрядного суммирования, выход второго блока 7 поразрядного суммирования соединен с третьим входом селектора 3, выход которого соединен с вы ходом устройства, управляющий вход командного блока 8 соединен с управляюпщм входом устройства, а выходы - с соответствующими управляющими входами регистров 4,-4, селектора 3. В блоке 1 вычисления контрольной суммы первый и второй входы мультиплексора 9 соединены соответственно с первым и вторым входами блока 1 вычисления контрольной суммы, выход - с информационными входами триггеров , выходы которьгх соединены с

соответствующими информационными параллельными входами регистра 11, выход последнего разряда которого соединен с выходом блока 1 вычисления контрольной суммы, управляющие входы мультиплексора 9, триггеров 10,-10g и регистра 11, а также установочные R-входы триггеров lOf-lOg соединены с соответствующими выходами командного блока 8.

Устройство для приемопередачи информации с контролем ошибок работает следующим образом.

В режиме приема пакета информации на информационный вход устройства поступает в последовательном виде п байт полезной информации, транспарентной для устройства; пакет завершает байт контрольной суммы. Каждый байт пакета и байт контрольной суммы завершает

контрольный, девятый бит дополнения

31

на четность. На управляющий вход устройства поступает сигнал сопровозкде- ния, указывающий устройству на наличие в канале пакета информации. Сигнал сопровождения инициирует разверт ку программы командного блока 8, который подает управляющие сигналы на другие блоки устройства. По сигналам блока 8п байт пакета записывается в последовательном виде в п 8-р азрядньг регистр, образованный п параллельно- сдвиговыми регистрами 4,-4„ . Парал- лельно пакет поступает на вход блока 6 поразрядного суммирования и на вхо блока 1 вычисления контрольной сум- мы. По управляющим сигналам командного блока 8 блок 6 осуществляет суммирование по модулю 2 с 1-го по 8-1 разряд каждого байта пакета. Во время поступления 9-го, контрольного, бита каждого байта пакета, поступающего на информационный вход устройства, блок 6 сравнивает накопленную сумму и значение поступающего 9-го бита. Результат сравнения регистри- руётся блоком 2 формирования сигнала ошибки. Блок 1 осуществляет накопление суммы по модулю 2 одноименных разрядов байт пакета. В результате к моменту поступления из канала бай- та контрольной суммы в блоке 1 накоплен местньй байт контрольной суммы. Блок 8 инициирует вывод из блока 1 местной контрольной суммы на второй вход блока 5 поразрядного сравнения синхронно с поступлением на первый вход блока 5 байта контрольной суммы поступающего пакета информации. Ре зультат сравнения регистрируется блоком 2. Если в принятом пакете от- сутствовали ошибки, блок 2 по сигналам управления блока 8 разрешает потребителю перезапись в параллельной форме п байт пакета с регистров 4,- 4. Тем самым режим приема пакета информации из канала завершается.

По сигналам разрешения, поступающим из блока 8, потребитель осуществляет запись в параллельной форме п байт в-регистры 4,-4f|, тем самым инициируя начало режима передачи пакета информации в канал.

По управляющим сигналам блока 8 регистры , в последовательной форме транслируют пакет через селектор ,3 на выход устройства. Параллельно ин- формах ия поступает на побитное суммирование в блок 7. С регистров 44-4п

510 15 20 25 зо р j

0

5

5

1664

через селектор 3 на выход устройства поступают кажд1.е 1-8-й биты п байт, а с блока 7 через селектор 3 на выход устройства поступает результат суммирования, т.е. 9-й контрольньй бит. Одновременно с формированием пакета 1 осуществляет накопление суммы одноименных бит п байт пакета. По окончании формирования п-го байта пакета с выхода блока 1 через селектор 3 на выход устройства поступает байт контрольной суммы. Блок 7 звершает байт контрольной суммы 9-м, контрольным, битом, после чего блок 8 аннулирует режим передачи и устройство устанавливается в исходное состояние. На фиг.2 и 3 раскрыт на функциональном уровне блок 1 вычисления контрольной суммы. В режиме приема пакета информация через мультиплексор 9 поступает на счетные входы триггеров . На входы разрешения счета триггеров 10 -1Qg поступают управляющие сигналы блока 8. По этим сигналам на триггерах 10,-IOg накапливается результат суммирования п байт пакета.

8конце п-го байта в параллельной форме результат суммирования по сигналу управления записывается в регистр 11. По этому же сигналу содержимое триггеров обнуляется. Во время прихода байта контрольной суммы пакета блок 8 переключает регистр 11 в режим сдвига и на первый и второй входы блока 5 синхронно поступают байт контрольной суммы пакета и местный байт накопленной в блоке 1 контрольной суммы. В режиме передачи блок 8 переключает мультиплексор

9и на вход блока вычисления контрольный суммы поступают фрагменты подготавливаемого пакета для накопления суммы одноименных разрядов байт пакета. В остальном работа блока 1 в режиме передачи идентична предыдущем режиму.

Сигнал 27 соответствует сигналу, поступающему с командного блока 8 на подготовительные входы регистров 4, -4 f, для приема информации. Сигналы 28 и 29 соответствуют сигналам, поступающим на управляющие входы селектора 3 с командного блока. Сигнал 30 соответствует информации на вькоде устройства.

На функциональной схеме устройства источник сигнала синхронизации.

а также цепь синхронизации условно не показаны.

Технико-экономические показатели устройства обеспечиваются введением режима записи-чтения в параллельной форме, всего пакета информации, что уменьшает период, обращения, непосредственное сравнение вводимого контрольного байта и накопленного резуль тата суммирования введенного пакета, минимизирует аппаратные средства, сокращает время обработки информации, формирование контрольного байта в процессе передачи пакета в канал позволяет отказываться от промежуточного накопителя контрольной суммы, полная транспарентность полезной информации пакета позволяет существенно упростить алгоритм обработки.

Формула изобретения

1. Устройство для приемопередачи информагщи с контролем ошибок, содержащее блок вычисления контрольной суммы, блок формирования сигнала ошибок и селектор, отличающее- с я тем, что, с целью упрощения, повьшения быстродействия и информационной гибкости устройства путем обеспечения параллельной и последовательной записи и считывания информации и последовательной обработки информации с контролем ошибок, в него введены регистры сдвига, блок поразрядного сравнения, командный блок, первый и вто- -рой блоки поразрядного суммирования, информационный вход устройства соединен с информационным входом последнего регистра, входом первого блока поразрядного суммирования и первыми входами блока вычисления контрольной суммы и блока поразрядного сравнения, выход последнего разряда каждого регистра соединен с информаци2771666

онным последовательным входом предыдущего регистра, выход последнего разряда первого регистра соединен с первым входом селектора, входом втоJ рого блока поразрядного суммирования- и вторым входом блока вычисления контрольной суммы, выход которого соединен с вторыми входами селектора и блока поразрядного сравнения, выход

10 которого соединен с первым входом блока формирования сигнала ошибок, второй вход которого соединен с выходом первого блока поразрядйого суммирования, выход второго блока по15 разрядного суммирования соединен с третьим входом селектора, выход которого соединен с выходом устройства, управляюш 1Й вход командного блока соединен с управляющим входом устрой20 ства, а выходы - с соответствующими управляющими входами регистров сдвига, селектора, первог о и второго блоков поразрядного суммирования, блока вычисления контрольной суммы,

25 блока поразрядного сравнения и блока формирования сигнала ошибки.

2, Устройство по П.1 отличающееся тем, что блок вьгчисле30 ния контрольной cyMMFJ выполнен в виде триггеров, регистра сдвига и мультиплексора, первый и второй входы которого соединены соответственно с первым и вторым входами блока вьгчис,, ления контрольной суммы, выход мультиплексора соединен с информационными входами триггеров, выходы которых соединены с соответствующими информационными параллельными входами реги Q стра сдвига, выход последнего разряда которого является выходом блока вычисления контрольной суммы, управ- ляюпще входы мультиплексора, триггеров и регистра сдвига и установоч45 ные входы триггеров являются входами блока вычисления контрольной суммы.

2, Устройство по П.1 отличающееся тем, что блок вьгчисления контрольной cyMMFJ выполнен в виде триггеров, регистра сдвига и мультиплексора, первый и второй входы которого соединены соответственно с первым и вторым входами блока вьгчисления контрольной суммы, выход мультиплексора соединен с информационными входами триггеров, выходы которых соединены с соответствующими информационными параллельными входами регистра сдвига, выход последнего разряда которого является выходом блока вычисления контрольной суммы, управ- ляюпще входы мультиплексора, триггеров и регистра сдвига и установочные входы триггеров являются входами блока вычисления контрольной суммы.

Редактор А.Гулько

Составитель В.Бутин Техред М.Ходанич

Заказ 6670/45 Тираж 515Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород,.ул. Проектная, 4

Корректор М.Максимишинец

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приемопередачи информации с контролем ошибок | 1987 |

|

SU1425757A1 |

| Устройство для сопряжения магистрали с ЦВМ | 1988 |

|

SU1569837A1 |

| Устройство ввода-вывода с контролем ошибок и индикацией | 1989 |

|

SU1728866A1 |

| Устройство для контроля переписи информации перезагружаемой управляющей памяти процессора | 1981 |

|

SU1008746A1 |

| Запоминающее устройство | 1990 |

|

SU1805496A1 |

| УСТРОЙСТВО ДЕТЕКТИРОВАНИЯ КАНАЛОВ ВИДЕОКОНФЕРЕНЦСВЯЗИ В СИСТЕМАХ ПЕРЕДАЧИ С ВРЕМЕННЫМ УПЛОТНЕНИЕМ | 2013 |

|

RU2539967C1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Запоминающее устройство | 1987 |

|

SU1510010A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре передачи и обработки информации. Целью изобретения является упрощение, повышение быстродействия, повышение информационной гибкости устройства путем обеспечения параллельной и последовательной передач информации и последовательной обработки информации с контролем ошибок. Устройство работает следующим образом. На сигнальный вход устройства поступает пакет информации в последовательном виде, на его управляющий вход - сигнал сопровождения. Управляющий сигнал инициирует развертку программы командного блока 8. Пакет информации записывается в последовательном виде в регистры 4 - 4j, сдвига и параллельно поступает на входы блоков 6 и 1 поразрядного суммирования и вычисления контрольной суммы. Наличие ошибки, выявляемой блоком 6 поразрядного суммирования на основе контроля по четности, фиксируется блоком 2 формирования сигнала ошибки. Если в принятом пакете информации ошибки отсутствуют, блок 2 по сигналам управления с командного блока 8 разрешает перезапись в параллельной форме пакета информации в регистры 4 -4f,. По сигналу управления с командного блока 8 регистры 4,-4f, сдвига транслируют пакет через селектор 3 на выход устройства. Параллельно информация поступает на (С (Л vj Риг.1

| СЕСОЮЗНАЯ IрйТЕг?ГНО-Т?Агы':г-Н/Ш^! | 0 |

|

SU359645A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для приема и выдачи информации с контролем ошибок | 1976 |

|

SU611244A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1986-12-15—Публикация

1985-01-11—Подача