Изобретение относится к устройствам электросвязи.

Цель изобретения - обеспечеш1е возможности формирования сигналов изменяемой амплитуды и частоты меньшей частоты дискретизации.

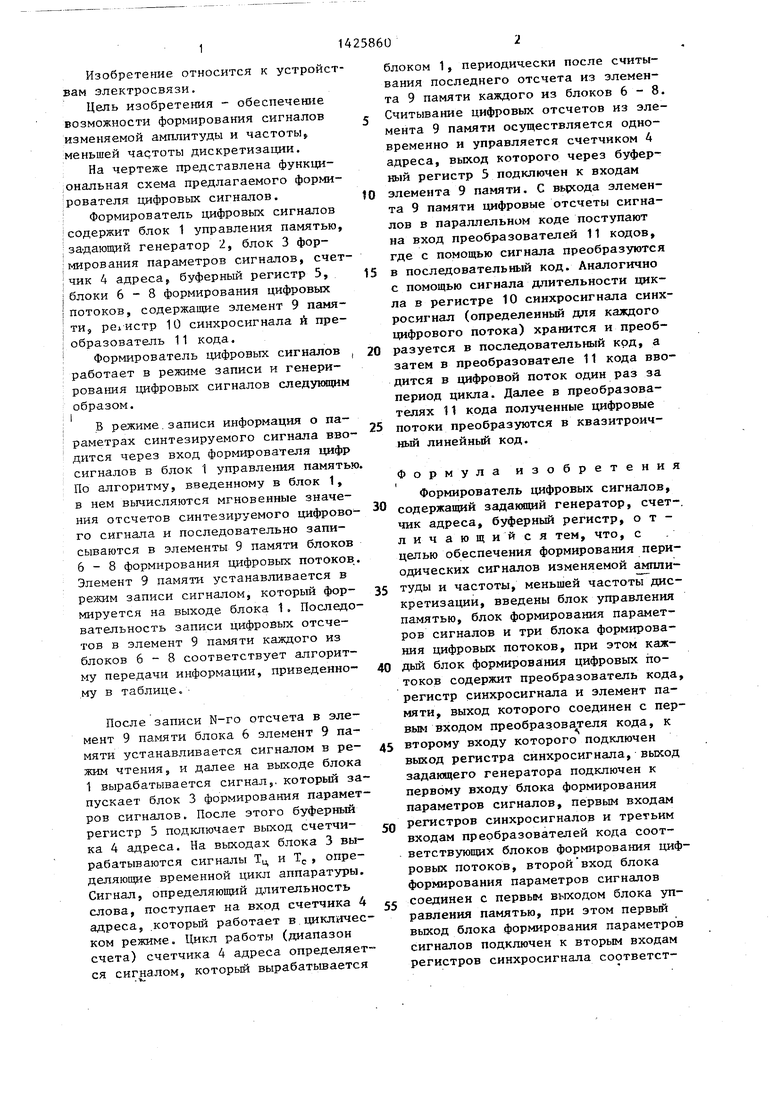

На чертеже представлена функциональная схема предлагаемого форми- ;рователя цифровых сигналов. Формирователь цифровых сигналов iсодержит блок 1 управления памятью, ;задающий генератор 2, блок 3 фор- iмирования параметров сигналов, счет чик 4 адреса, буферный регистр 5, 1 блоки 6-8 формирования цифровых : ПОТОКОВ, содержащие элемент 9 памяти, регистр 10 синхросигнала и преобразователь 11 кода.

Формирователь цифровых сигналов работает в режиме записи и генерирования цифровых сигналов следуннцим

образом. I

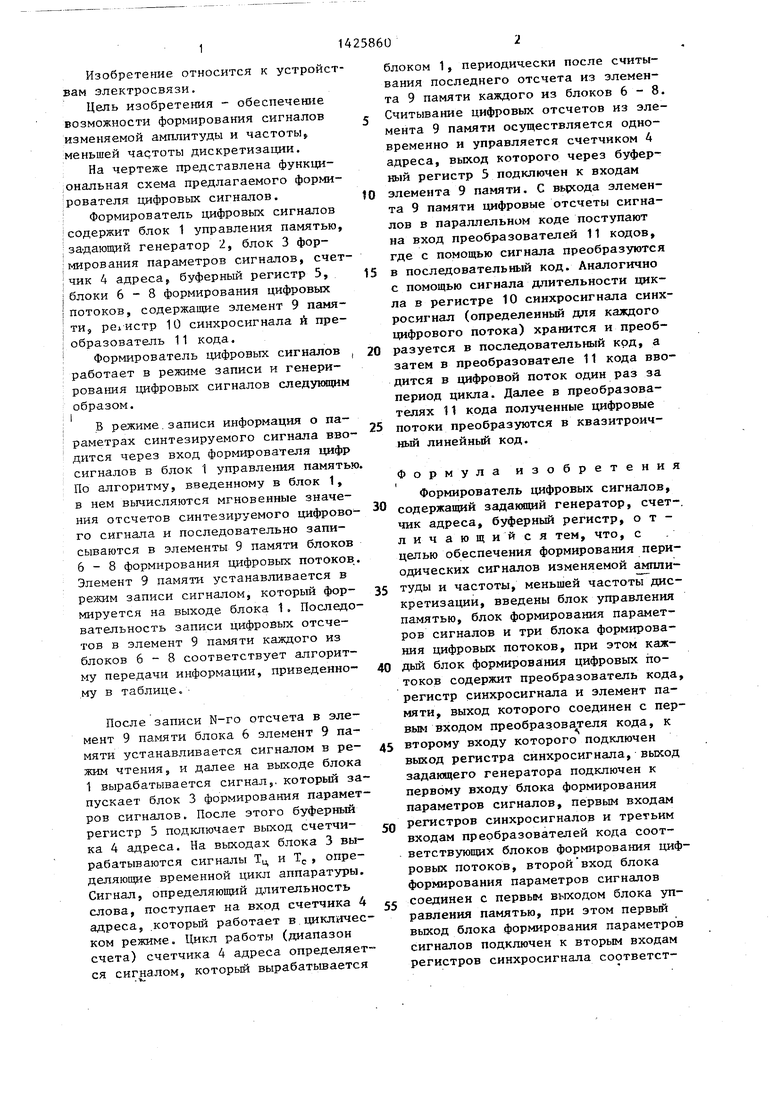

В режиме.записи информация о параметрах синтезируемого сигнала вводится через вход формирователя цифр сигналов в блок 1 управления памятью По алгоритму, введенному в блок 1, в нем вычисляются мгновенные значения отсчетов синтезируемого цифрового сигнала и последовательно записываются в элементы 9 памяти блоков 6-8 формирования цифровых потоков, Элемент 9 памяти устанавливается в режим записи сигналом, который формируется на выходе блока 1. Последовательность записи цифровых отсчетов в элемент 9 памяти каждого из блоков 6-8 соответствует алгоритму передачи информации, приведенному в таблице.

После записи N-ro отсчета в элемент 9 памяти блока 6 элемент 9 памяти устанавливается сигналом в режим чтения, и далее на выходе блока 1 вырабатывается сигнал,, который запускает блок 3 формирования параметров сигналов. После этого буферный регистр 5 подключает выход счетчика 4 адреса. На выходах блока 3 вырабатываются сигналы Тц и Тр, определяющие временной цикл аппаратуры. Сигнал, определяющий длительность слова, поступает на вход счетчика 4 адреса, который работает в циклическом режиме. Цикл работы (диапазон счета) счетчика 4 адреса определяется сигналом, который вырабатьшается

блоком 1, периодически после считывания последнего отсчета из элемента 9 памяти каждого из блоков 6-8.

Считывание цифровых отсчетов из элемента 9 памяти осуществляется одновременно и управляется счетчиком 4 адреса, выход которого через буферный регистр 5 подключен к входам

элемента 9 памяти. С вьрсода элемента 9 памяти цифровые отсчеты сигналов в параллельном коде поступают на вход преобразователей 11 кодов, где с помощью сигнала преобразуются

в последовательный код. Аналогично с помощью сигнала длительности цикла в регистре 10 синхросигнала синхросигнал (определенный для каждого цифрового потока) хранится и преобразуется в последовательный код, а затем в преобразователе 11 кода вводится в цифровой поток один раз за период цикла. Далее в преобразователях 11 кода полученные цифровые

потоки преобразуются в квазитроичный линейный код.

Формула изобретения

Формирователь цифровых сигналов,

содержащий задающий генератор, счет-, чик адреса, буферный регистр, отличающийся тем, что, с целью обеспечения формирования периодических сигналов изменяемой амплитуды и частоты, меньшей частоты дискретизации, введены блок управления памятью, блок формирования параметров сигналов и три блока формирования цифровых потоков, при этом кажДьш блок формирова;ния цифровых потоков содержит преобразователь кода, регистр синхросигнала и элемент памяти, выход которого соединен с первым входом преобразователя кода, к

второму входу которого подключен выход регистра синхросигнала, выход задающего генератора подключен к первому входу блока формирования параметров сигналов, первым входам

регистров синхросигналов и третьим входам преобразователей кода соответствующих блоков формирования цифровых потоков, второй вход блока формирования параметров сигналов

соединен с первым выходом блока управления памятью, при этом первый выход блока формирования параметров сигналов подключен к вторым входам регистров синхросигнала соответствующих блоков формирования цифровых потоков, второй выход блока формирования параметров сигналов соединен с первым входом счетчика адреса и с четвертыми входами преобразователей кода соответствуклцих блоков формирования цифровых потоков, второй выход блока управления памятью соединен с вторым входом счетчика адреса, выход которого подключен к первому входу буферного регистра, второй вход которого соединен с третьим выходом блока управления памятью и с первыми входами элементов памяти.

соответствующих блоков формирования цифровых потоков, четвертый выход блока управления памятью соединен с выходом буферного регистра и с вторыми входами элементов памяти соответствующих блоков формирования цифровых потоковj пятый выход блока управления памятью соединен с третьими входами элементов памяти соответствующих блоков формирования цифровых потоков, при этом вход блока управления памятью является входом формирователя цифровых сигналов.

15

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Система радиосвязи | 1989 |

|

SU1660187A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ГИДРОЛОКАТОРА БОКОВОГО ОБЗОРА | 1993 |

|

RU2060516C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Автокоррелятор | 1989 |

|

SU1617447A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

Изобретение относится к электросвязи. Цель изобретения - обеспечение возможности формирования сигналов изменяемой амплитуды и частоты, меньшей частоты дискретизации. Формирователь содержит блок управления (БУ) 1 памятью, заданлций г-р 2, блок формирования (БФ) 3 параметров сигналов, счетчик 4 адреса, буферный регистр 5 и БФ 6 - 8 цифровых потоков, каждьй из которых состоит из эл-та 9 памяти, регистра 10 синхросигнала и преобразователя 11 кода, формирователь работает в двух режимах. В режиме записи информация о параметрах синтезируемого сигнала вводится в БУ 1. В нем вычисляются мгновенные значения отсчетов синтезируемого цифрового сигнала, которые последовательно записьшаются в эл-ты 9. После записи N-ro отсчета осу1цествляется считьшание цифровых отсчетов из эл-тов 9 на преобразователи 11. В них полученные цифровые потоки преобразуются в квази- троичньй линейный код. 1 ил., 1 табл. (Л

t

Блок формирования цифровых потоков

IIjmiZIII --IIII

1-й отсчет 2-й отсчет 3-й отсчет

4-й отсчет

....-....

(N-2)-й отсчет

римечание.

N - количество отсчетов, необходимое для получе дая целого периодов синтезируемого сигнала с заданной точностью.

5-й отсчет

6-й отсчет

(. (

(Н-1)-й отсчет N- й отсчет

| Егранжиев А.Н., Шехтман Б.И | |||

| Генератор цифрового периодического сигнала | |||

| - Техника средств связи | |||

| Сер | |||

| Техника радиовещательного приема и акустики | |||

| Вьш | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-25—Подача