to

СО N5

00

1

Изобретение относится к области импульсной техники и может быть ис- пЬльзовано в цифровой, измерительной и вычислительной аппаратуре, а также в устройствах автоматики в качестве синхронного D-триггера.

Целью изобретения является повышение надежности путем упрощения c|iHxpoHHoro D-триггрра,

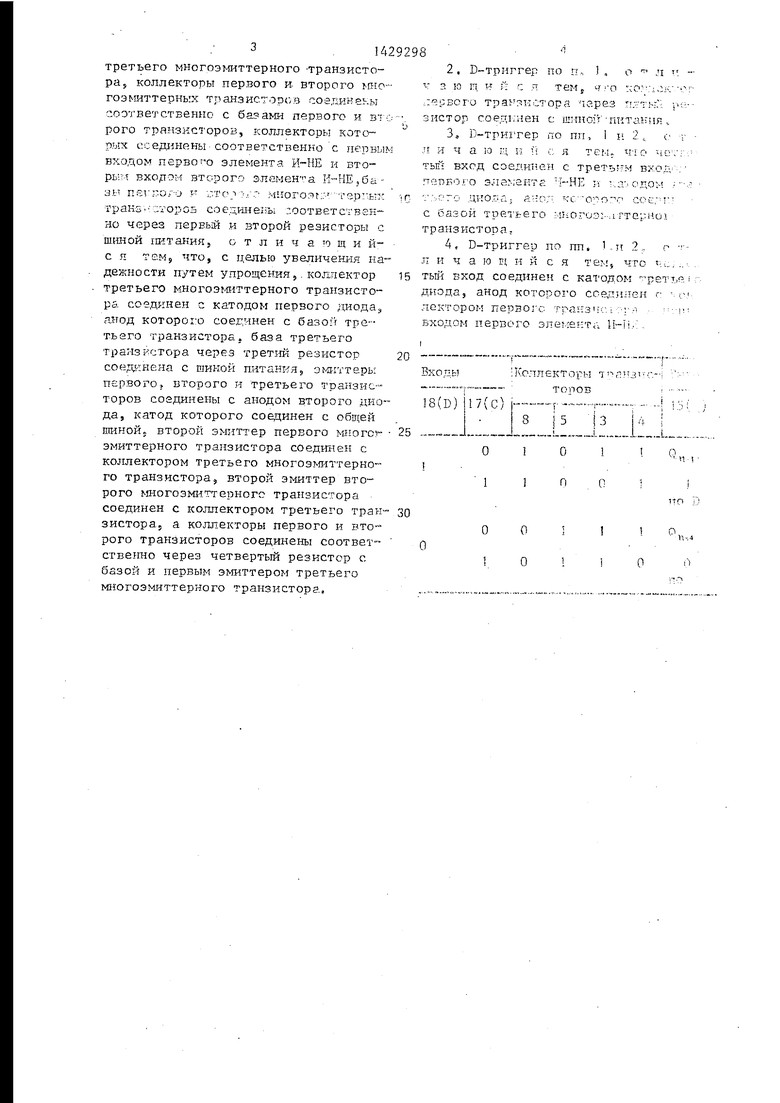

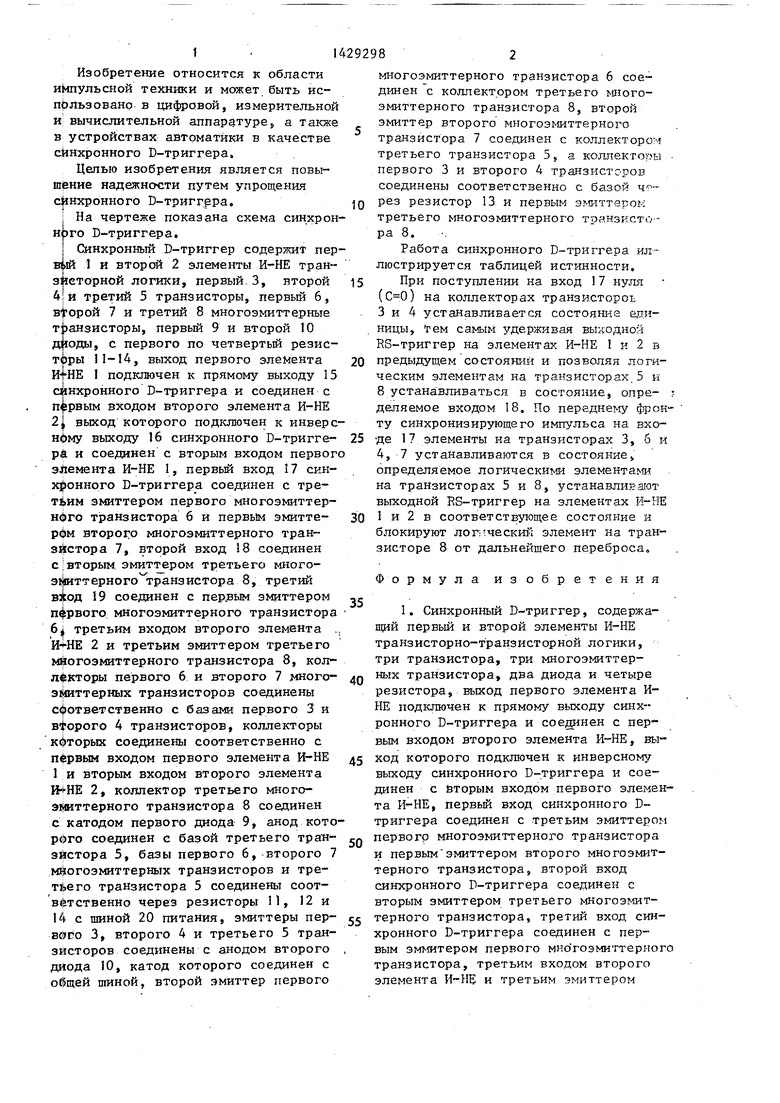

i На чертеже показана схема синхрон нрго D-триггера.

I Синхронный D-триггер содержит пер Bitfi 1 и второй 2 элементы И-НЕ тран- з еторной логики, первый.3, второй 4}и третий 5 транзисторы, первый 6, второй 7 и третий 8 многоэмиттерные т;)анзисторы, первый 9 и второй 10 диоды, с первого по четвертый резисторы 1 1-14, выход первого элемента И--НЕ 1 подхслючен к прямому выходу 15 aiHxpoHHoro D-триггера и соединен с П( рвым входом второго элемента И-НЕ 2i выход которого подключен к инверс нфму выходу 16 ctmxpoHHoro D-тригге- рй и соединен с вторым входом первог элемента И-НЕ 1, первый вход 17 синхронного D-триггера соединен с тре- т$им эмиттером первого многоэмиттер- нфгс транзистора 6 и первым эмитте- рфм второго многоэмиттерного транзистора 7, второй вход 18 соединен с I вторым эмиттером третьего много- э 1иттерного транзистора 8, третий вфод 19 соединен с пер.вым змиттером первого многоэмиттерного транзистора 6i третьим входом второго элемента 2 и третьим эмиттером третьего мйогоэмиттерного транзистора 3, кол- лфкторы первого 6 и второго 7 много- Э11 иттерных транзисторов соединены )ответственно с базами первого 3 и вфорого 4 транзисторов, коллекторы к(|)торых соединены соответственно с пфрвым входом первого элемента И-НЕ 1 и вторым входом второго элемента Й4-НЕ 2, коллектор третьего много- эИиттерного транзистора 8 соединен с катодом первого диода 9, анод кото рфго соединен с базой третьего тран- зйстора 5, базы первого 6, второго 7 м$огоэмиттерных транзисторов и третьего транзистора 5 соединены соот- в тственно через резисторы 11, 12 и 14 с шиной 20 питания, эмиттеры пер- BcJro 3, второго 4 и третьего 5 транзисторов соединены с анодом второго диода 10, катод которого соединен с общей шиной, второй эмиттер первого

многоэмиттерного транзистора 6 соединен с коллектором третьего многоэмиттерного транзистора 8, второй эмиттер второго многоэмиттерного транзистора 7 соединен с коллектором третьего транзистора 5, а коллекторы первого 3 и второго 4 транзисторов соединены соответственно с базой Ч П- рез резистор 13 и первым эмиттерок третьего многоэмиттерного транзксто-- ра 8.

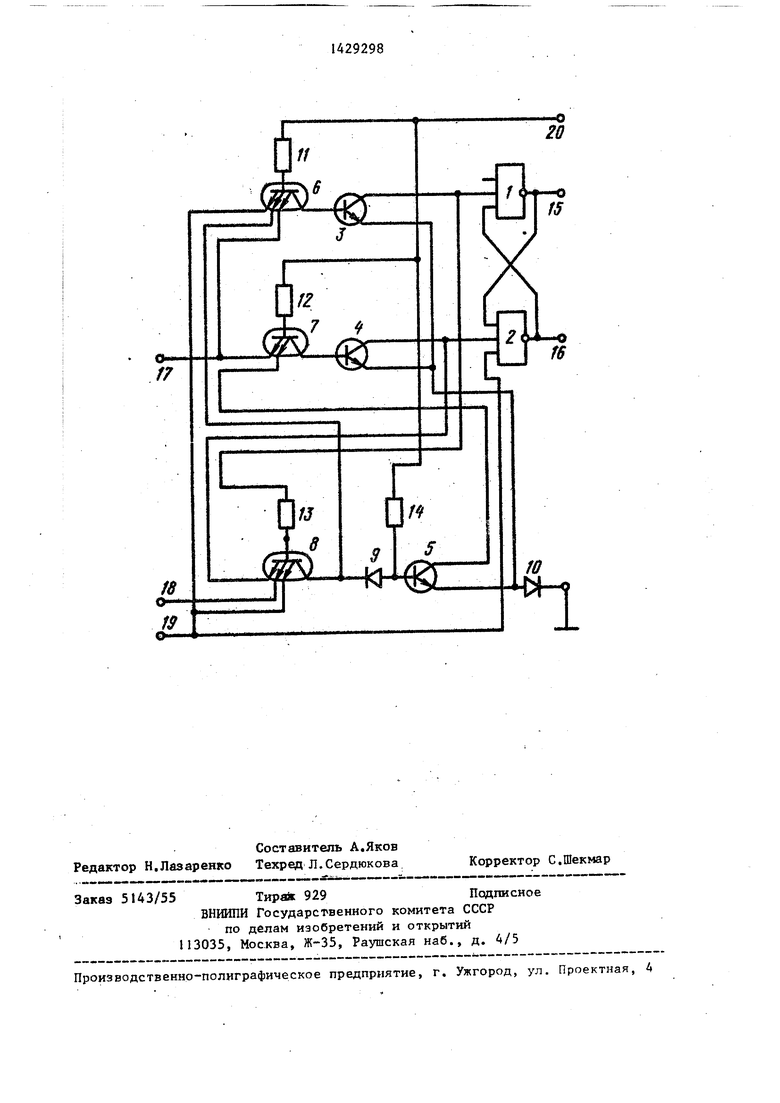

Работа синхронного D-триггера иллюстрируется таблицей истинности.

При поступлении на вход 17 нуля () на коллекторах транзистороь 3 и 4 устанавливается состояние единицы, тем самым удерживая выходной RS-триггер на элементах И-НЕ 1 и 2 в предыдущем состояний и позволяя логическим элементам на транзисторах,5 к 8 устанавливаться в состояние, опре- деляемое входом 18. По переднему фрон ту синхронизирующего импульса на входе 17 элементы на транзисторах 3, б и 4, 7 устанавливаются в состояннВ), определяемое логическими элементами на транзисторах 5 и 8, устанавливают выходной RS-триггер на элементах И-НЕ 1 и 2 в соответствующее состояние и блокируют лог .ческик элемент на транзисторе 8 от дальнейшего переброса.

Формула изобретения

1. Синхронный D-триггер, содержащий первьш и второй элементы И-НЕ транзисторно-транзисторной логики, три транзистора, три многоэмиттер- ных транзистора, два диода и четыре резистора, выход первого элемента И- НЕ подключен к прямому выходу синхронного D-триггера и с первым входом второго элемента И-НЕ, выход которого подключен к инверсном}/ выходу синхронного D-триггера и соединен с Вторым входом первого элемента И-НЕ, первьй вход синхронного D- триггера соединен с третьим эмиттером первогр многоэмиттерного транзистора и первым эмиттером второго многоэмиттерного транзистораJ второй вход синхронного D-триггера соединен с вторым эмиттером третьего многоэмиттерного транзистора, третий вход синхронного D-триггера соединен с первым эм {итером первого мно гоэмиттериог транзистора, третьим входом второго элемента И-НЕ и третьим эмиттером

31429298

третьего многоэмиттерного -транзисто.

ра j коллекторы первого и- второго мне- гоэмиттернь:х транзисторов соединекы соответственно с базами первого и зт о рого транзисторов, коллекторы которых соединены соответствен11О с первым входом первого элемента и вторым входом второго элемен а Н--НЕ,ба- зъ пепюг О F -To -ir- многояг::- терньпс транз ;;торОБ coe mieHb; соответственно через первый и второй резисторы с гштагшя, о т л и ч а та щ и й- с я тИМ, что, с целью увеличения надежности путем упрощения 5.коллектор третьего многоэ№1ттврного транзистора соедогнен с катодом нервого днода,, яиод которого соединен с базой третьего транзистора} база третьего транзистора через третий резистор соедагнена с шиной питания, э№ггтеры первого, второго и третьего транзисторов соединены с анодом второго диода, катод которого соединен с общей гоинойр второй эмиттер первого многое эмиттерного транзистора соединен с коллектором третьего многоэмиттерного транзистора, второй эмиттер второго ffloгoэмиттepнoгc транзистора соединен с коллектором третьего тра зистора, а коллекторы первого и второго транзисторов соединены соответ- ственно через четвертый резистор с базой и первым эмиттером третьего многоэмиттерного транзистора.

2,D-триггер по п, 1 , о .ч тг - V 3 ю ш и ft с я TeMj 1со;-:.1,;к -ог .zecBoro Tpai KCTopa перез Т1; : ьг ; v u- 3 ист op соед1;:иен с ш тноз т -питания.,

3,D-тригтер по пп, 1 к 2. с г - л и ч а ю щ и li с, я тем. Ч Ю чсчт тьй вход соедиТ бн с третьг м Bxofv . гтйПЕОго элг ;ентй i-HE н т,д-, одом .-. г:-, ,Ц1-:ог;а; ано;; сое;-т

с базой третьего ,м: 10гоэ:-,1гтер - .о1 транзистора.

4,D-триггер по пп, К и 2,, г ; л и ч а ю щ и и с я что t;,., . , тый вход соединен с катодом ретт.е i диода, анод которого г: г лектором nepBOj c транз к-1 : ;-л входом первого элемента И-П/

-

Т

;Коллекторы

ТОрОБ

,.Оi

1

8 1 1

О О

5 О

13 1 О

|3 М ..1.„.,-L

I

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Разностный элемент управления | 1974 |

|

SU500590A1 |

| Синхронный @ -Триггер | 1985 |

|

SU1336208A1 |

| Элемент троичной логики | 1980 |

|

SU892729A1 |

| Одновибратор | 1978 |

|

SU733088A1 |

| Интегральный логический элемент для возбуждений линий передачи коллективного пользования | 1974 |

|

SU636804A1 |

| Транзисторно-транзисторный логический элемент | 1983 |

|

SU1128387A1 |

| Сумматор | 1986 |

|

SU1338053A1 |

| УНИВЕРСАЛЬНЫЙ ТРИГГЕР | 1973 |

|

SU364079A1 |

| Ячейка памяти для регистра сдвига | 1973 |

|

SU543013A1 |

| JK-триггер | 1989 |

|

SU1713091A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики в качестве синхронного D-триггера. Цель изобретения - повыпение надежности путем упрощения. Синхронный D-триггер содержит два элемента И-НЕ, три много- змиттёрных транзистора, три транзистора, четыре резистора и два диода. Введение новых связей позволяет обеспечить -работоспособность триггера при меньшем количестве элементов. 3 з.п. ф-лы, 1 ил, 1 табл.

| Пятлин О.А., Овсищер П.И., Лазер И.М | |||

| и др | |||

| Проектирование микроэлектрониых цифровых устройств | |||

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Контрольный стрелочный замок | 1920 |

|

SU71A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шагурин И.И | |||

| Транзисторно-транзисторные логические схемы | |||

| - М.; Советское радио, 1974, с | |||

| Реверсивный дисковый культиватор для тросовой тяги | 1923 |

|

SU130A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-10-07—Публикация

1987-02-04—Подача