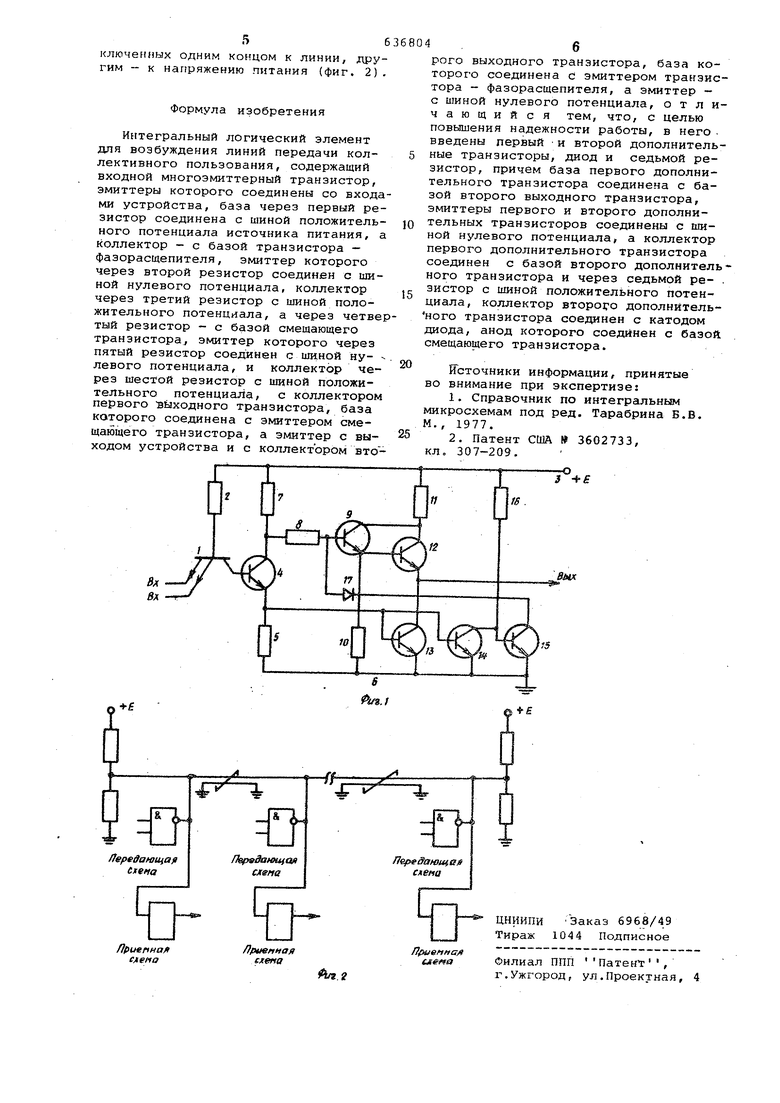

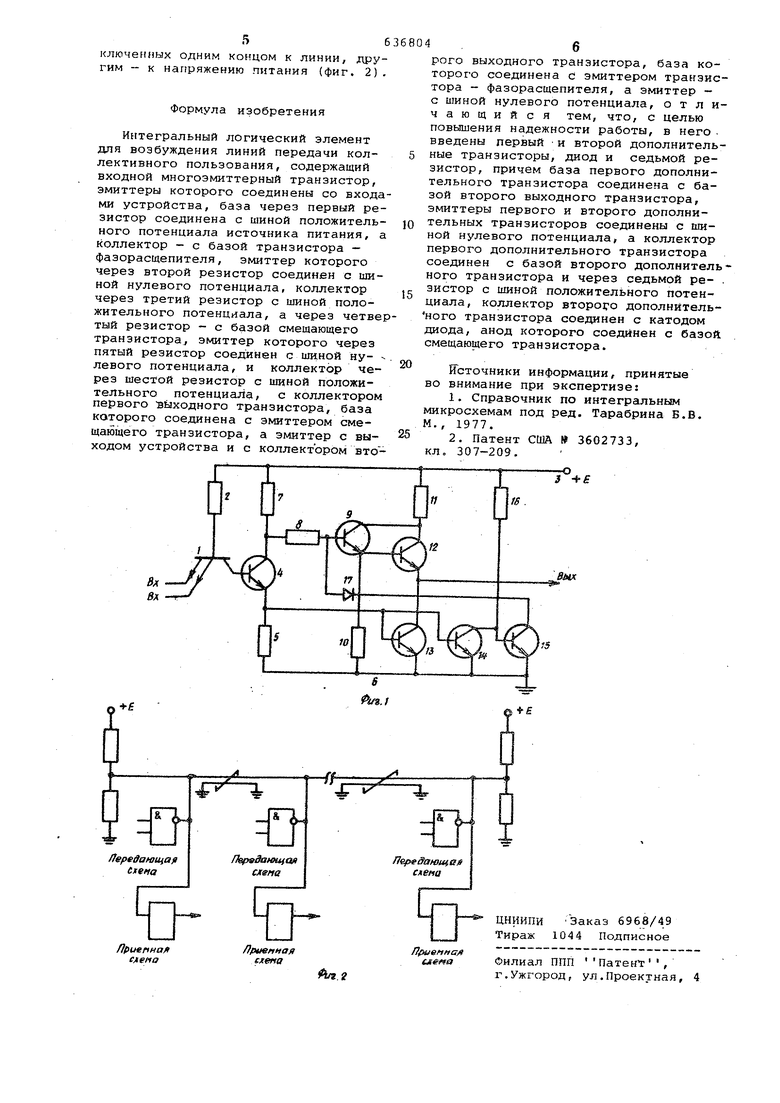

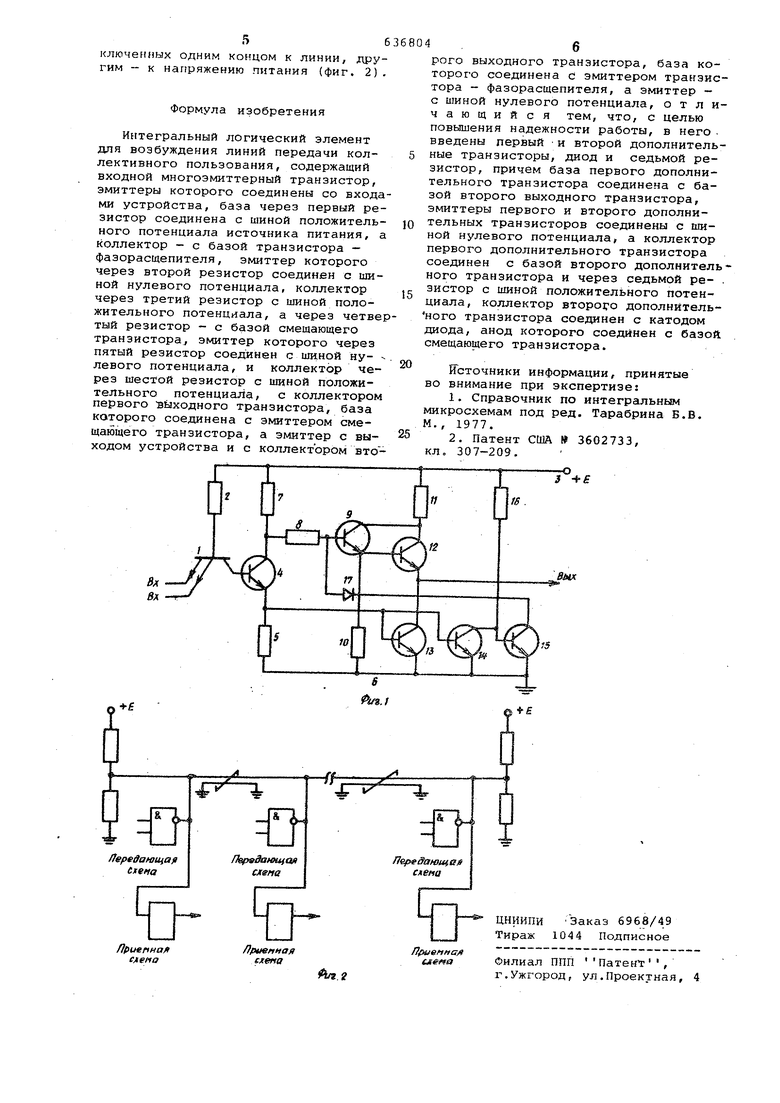

ходным xpaiiSHCTOpOM и смещающим .транзистором передающей схем-Ы, нахо дящейся в состоянии логического 0. Цель предлагаемого изобретения - повышение надежности работы устройства при одновременном включении нескольких устройств в линию коллективного пользования о Для этого интегральный логический элемент д,гш воэбулодения линий передачи коллективного пользованияf содержавдй Еходи зй миогоэмкттерный транзистор; элетттеры которого соединены со входами устройства база через первый резистор соединена с шиной пололдательногр потенциала источника питания, а коллектор - с базой транзистора - фазорасгцепителя эмиттер которого через второй резистор соединен с миной иулазого потен циаЛс1, коллектор через третий резистор с шиной положительного потенгдиала. а через четвертый резистор -- с базой смещающего транзистора, э литтер кото рого через пятый резистор соединен с шиной нулевого потенциала, и коллектор через шестой резистор с шиной положительного потенциалаf с коллек тором первого выходного транзистора, база которого соединена с эмиттером смещающего транзистора, а эмиттер с выходом устройства и с коллектором второго выходного транзистора,- база которого соединена с эг.етттером транФазорасщепителя,, а эмиттер зистора с шиной нулевого потенциала, В предл гаемое устройство введены первый и второй дополнительные транзисторы, диод и седьмой резистор,, причем база первого дополнчтельного трг1нзистора соединена с базой второз.-о вш-содного транзи.стораг эмиттерьз первого и втор го дополнительных транзцсторов соеди ненн с шиной Е- улевого потенциала, а коллектор .гО; дополни.тель{ ого транзистора соединен с базой второго дополнительного транзистора и через седьмой резистор с ЕШНОЙ положителБного потенциг ла, коллектор БторЬго,. .. дополнительного транзистора соедки.ей катодом диоды, анод которого сбедиие с базой смещающего транзистора. На фиг о I представлена-принципиая ная схема предлагаемого интегральног логнче-ского эле мента для, возбуждения линий передач коллективного пользова ния; на фиг. 2 - схема согласования линии передачи. Элемент содержит многоэмиттер-° ный транзмстор 1, эмиттеры которого соединень} со входами , устрой ства / база чераз ревистор 2 соединен с шиной 3 полояятельного потенциала источника питания.;. аколлектор соединен с базой транзистора - фазорасщепителя 4, э штгep которого соединен через резистор 5 с нулевого потенциала (5, а коллектор через резистор 7 сое.динеи с ашной 3 а через резистор 8 с базой смещающего транзистора 9, эмиттер которого через резистор 10 соединен с шиной 6, а коллектор соединен с первым выводом резистора 11, второй вывод которого соединен с шиной 3. При этом первый вывод резистора 11 соединен с коллектором верхнего выходного транзистора 12, база которого соединена с эмиттером транзистора 9, а эмиттер с выходом устройства и с коллектором нижнего .выходного транзистора 13, база которого соединена с эмиттером транзистора 4, а эмиттер - с шиной б. Устройство содержит первый дополнительный транзистор -14, второй дополнительный транзистор 15, резистор 16, диод 17. Причем база транзистора 14 соединена с базой транзистора 13, а эмиттер транзистора 14 соединен с эмиттером транзистора 15 и с шиной 6, а коллектор - с базой транзистора 15 и через резистор 16 с шиной 3, коллектор транзистора 15 соединен с катодом диод 17, анод которого соединен с базой транзистора 9. Предлагаемый элемент работает следуюцдам образом. Передаваемые сигналы подаются со стандартных ТГЛ схем на входы многоэмиттерного транзистора 1. При подаче на все входы высокого напряжения уровня логической 1, на вы-ходе схемы устанавливается низкий уровень лог. единицы . При этом транзистор 13 наCHaiSHy транзисторы 9, 12 выключены. Транзистор 14 в данном режиме работы выключается выключая транзистор 15, и цепь на транзисторе 15 и диоде 17 не влияет на работу схег4Ы. При подаче на любой из входов низког-о уровня лог. нуля , в переходном режиме выходной каскад работает как в обычном ТТП-клапане; транзистор 13 выклгочается, а транзисторы9, 12 включаются, обеспечивая быстрый перезаряд нагрузочной,емкости. Кроме того, при подаче низкого входного напряжения лог. О происходит выключение транзистора 14 и включение tpciHSHCTOpa 15, ка коллекторе которото устанавливается низкое напряжение в. Это приводит к выключенйю; .т.ранзисгоров 9 и 12 схемы. .Таким, образом, в переходном режимепри переключении. вызсоДа- с.хемы в состояние лог. 1 происходит быстрое nepeKjxio-tieHHe схемы за- .счет включения транзисторов 7,- .11, а Ч1ерез время, необходимое для переключения транзис-. торов 13, 15 дополнительная цепь защиты обеспечивает выкл1бчение транзисторов 9 и 12.-Выключение транзисторов 9 и 12 в установившемся состоянии обеспечивает защиту .от недопустимой мощности рассеяния, перёдаюощх рхем. Согласование линии передачи осуществляется на обеих- концах линии с помощью согласуюищх резисторов, подключеняых одним концом к линии, дру гим к напряжению литания (фиг. 2) Формула изобретения Интегральный логический элемент для возбуждения линий передачи коллективного пользования, содержащий входной многоэмиттерный транзистор, эмиттеры которого соединены со входа ми устройства, база через первый ре зистор соединена с шиной положитель ного потенциала источника питания, коллектор - с базой транзистора - фазорасщепителя, эмиттер которого через второй резистор соединен с шиной нулевого потенциала, коллектор через третий резистор с шиной положительного потенциала, а через четве тый резистор - с базой смещающего транзистора, эмиттер которого через пятый резистор соединен с шиной нулевого потенциала, и коллектор через шестой резистор с шиной положительного потенциала, с коллектором первого выходного транзистора, база которого соединена с эмиттером смещающего транзистора, а эмиттер с выходом устройства и с коллектором вто ,б рого выходного транзистора, база которого соединена с эмиттером транзистора - фазорасщепителя, а эмиттер с шиной нулевого потенциала, отличающийся тем, что, с целью повышения надежности работы, в него. введены первый и второй дополнительные транзисторы, диод и седьмой резистор, причем база первого дополнительного транзистора соединена с базой второго выходного транзистора, эмиттеры первого и второго дополнительных транзисторов соединены с шиной нулевого потенциала, а коллектор первого дополнительного транзистора соединен с базой второго дополнительного транзистора и через седьмой ре- . зистор с шиной положительного потенциала, коллектор второго дополнительного транзистора соединен с катодом диода, анод которого соединен с базой смещающего транзистора. Источники информации, принятые во внимание при экспертизе: 1.Справочник по интегральным микросхемам под ред. Тарабрина Б.В. М., 1977. 2.Патент США № 3602733, кл. 307-209,

,

| название | год | авторы | номер документа |

|---|---|---|---|

| Входное устройство схемы сранения токов | 1985 |

|

SU1363452A1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Устройство согласования интегральных инжекционных схем с линиями передачи коллективного пользования | 1983 |

|

SU1092726A1 |

| Интегральный логический элемент и-не | 1978 |

|

SU790333A1 |

| Пороговый логический элемент | 1975 |

|

SU600711A1 |

| Входное устройство схемы сравнения токов | 1989 |

|

SU1626360A1 |

| Устройство преобразования однофазового логического сигнала в парафазный ток | 1976 |

|

SU570201A1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| Логический элемент | 1983 |

|

SU1138941A1 |

| Логическое устройство | 1977 |

|

SU738171A1 |

Авторы

Даты

1978-12-05—Публикация

1974-05-29—Подача