СП

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1624459A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ ИНФОРМАЦИОННЫХ СВОЙСТВ ТЕСТА | 1991 |

|

RU2068580C1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1723661A1 |

Изобретение относится к устрой- ствйм автоматики и вычислительной техники и может быть использовано в качестве встроенной системы контроля цифровых блоков в процессе эксплуатации. Целью изобретения является повышение производительности контроля, а также расширение области применения за.счет обеспечения возможности контроля цифровых блоков, работающих в реальном масштабе времени. Устройство содержит блок 1 управления, генератор 2 тестов, коммутатор 9, шифратор,- счетчик 3, дешифратор 7, узел 8 контроля. В случае освобождения системы, в которую входит цифровой блок, устройство автоматически переходит в режим контроля проверяемого блока. Во время контроля при необходимости включения цифровой системы в работу в предлагаемом устройсчрве (обычно в случае возникновения экстренной необходимости включения системы в работу режим контроля не может прерываться) режим контроля автоматически прекращается, и система может выполнять свои рабочие функции. Устройство каждый свободный от работы системы промежуток времени использует для организации контроля. Контроль системы проводится чаще, что позволяет своевременно обнаруживать и устранять неисправности и повьш1ает надежность работы. Такой режим контроля не мешает системе выполнять свои рабочие функции, т.к. при необходимости контроль автоматически прекращается, 1 з.п. ф-лы, 4 ил. с: (С СП 4ib СС

&. f

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве встроенной системы контроля цифровых блоков в процессе эксплуатации.

Цель изобретения - повьшение производительности контроля, а также расширение области применения устройства путем обеспечения возможности контроля цифровьк блоков, работающих в реальном масштабе времени.

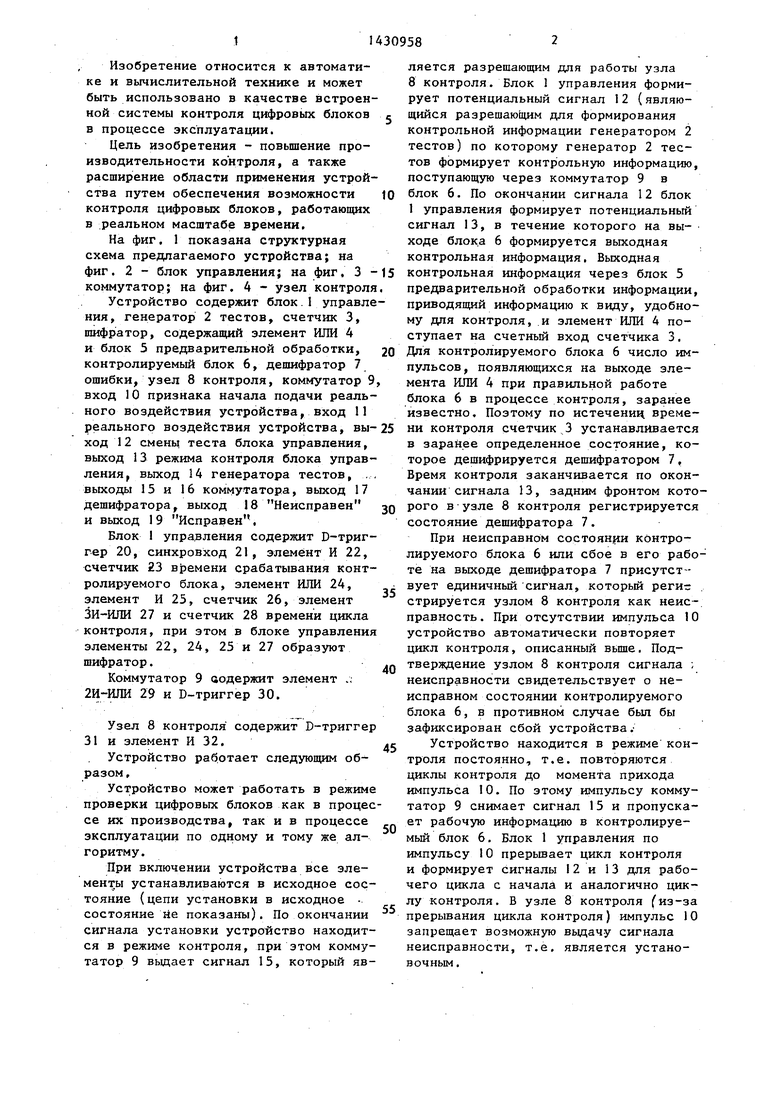

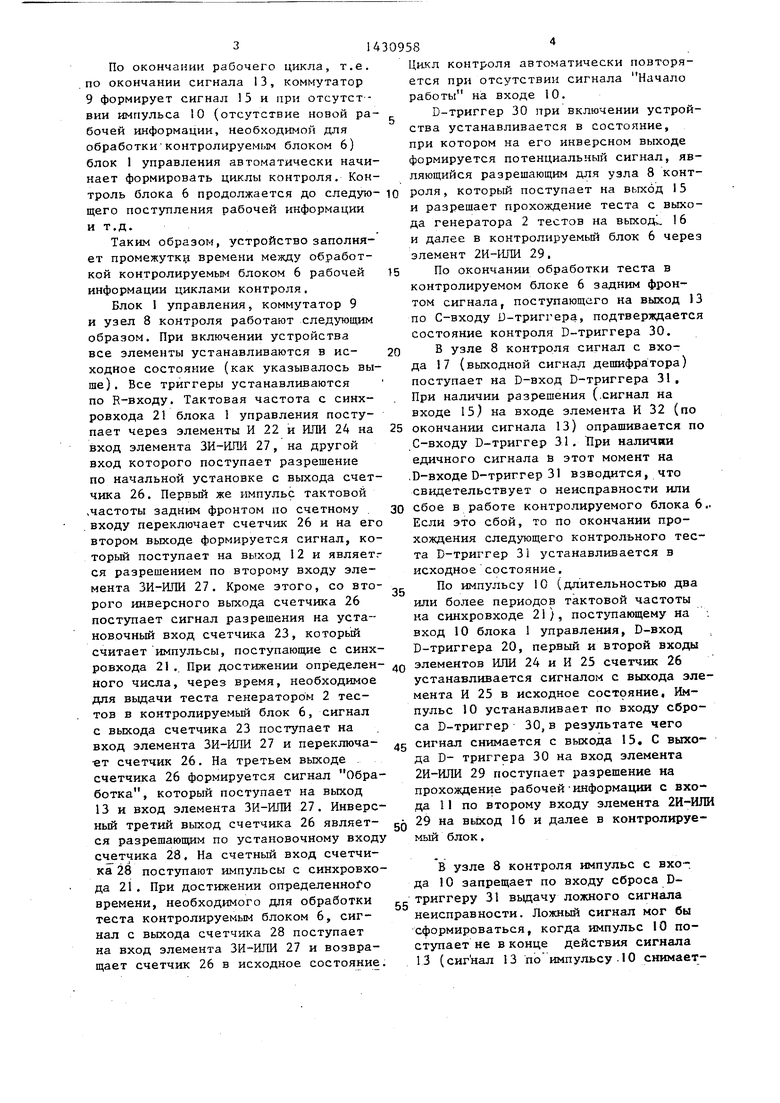

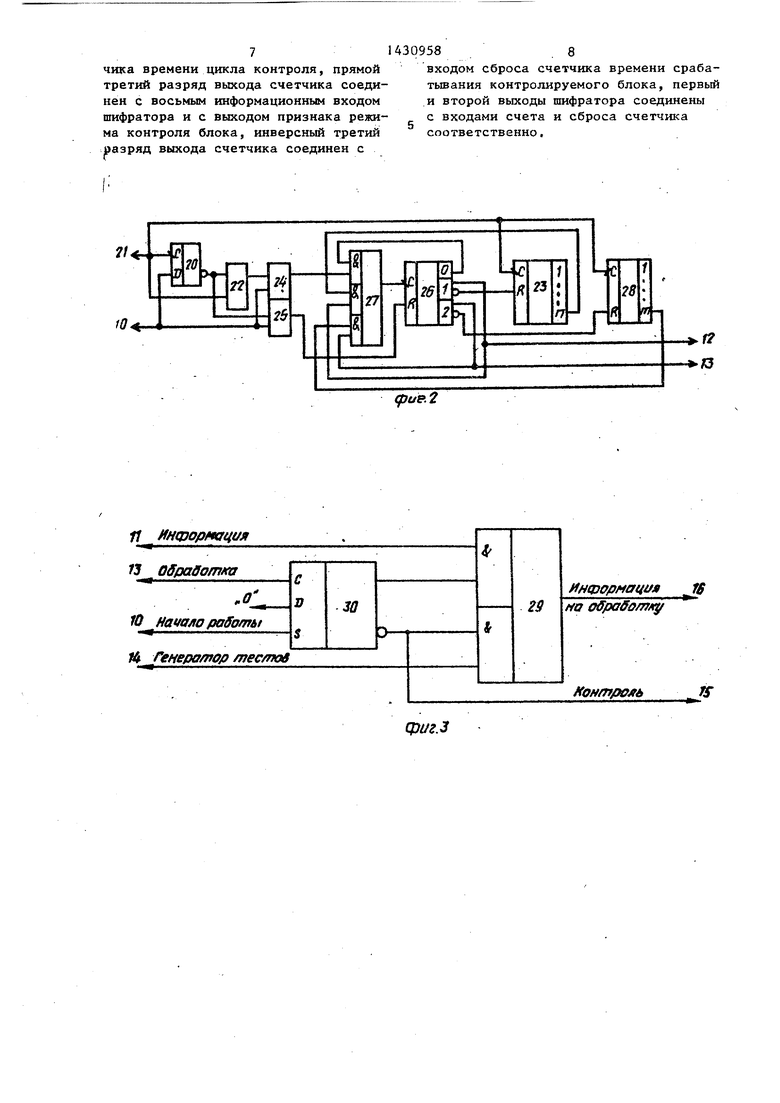

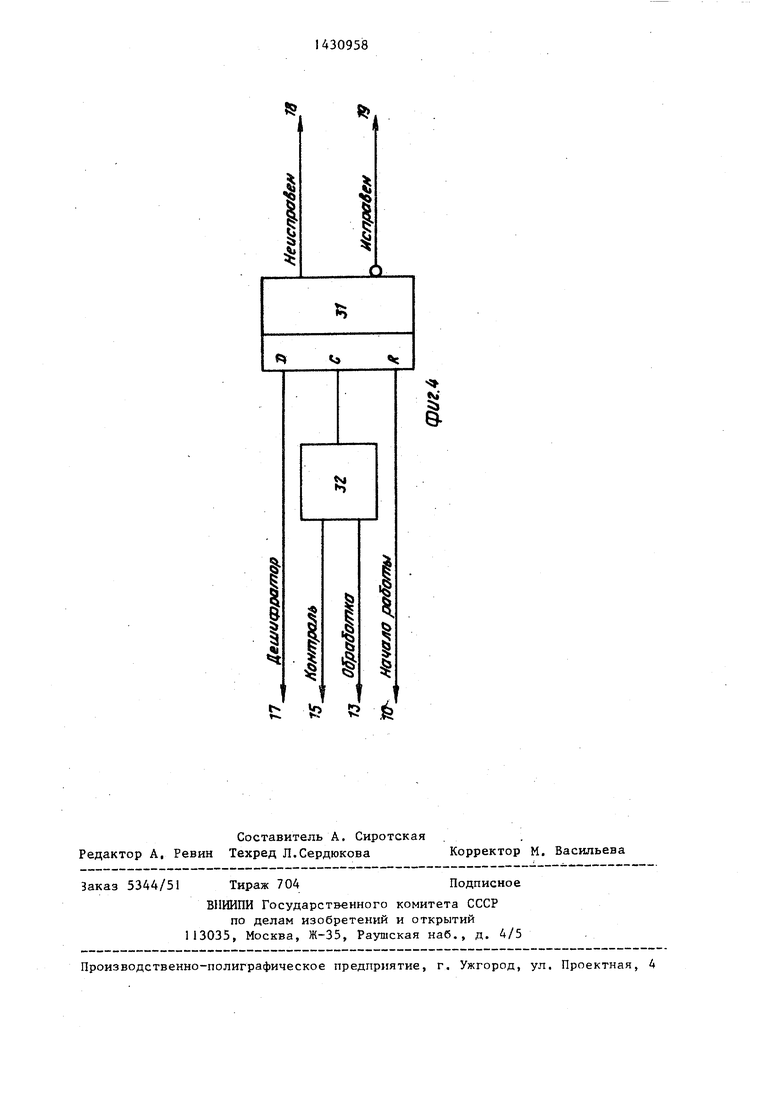

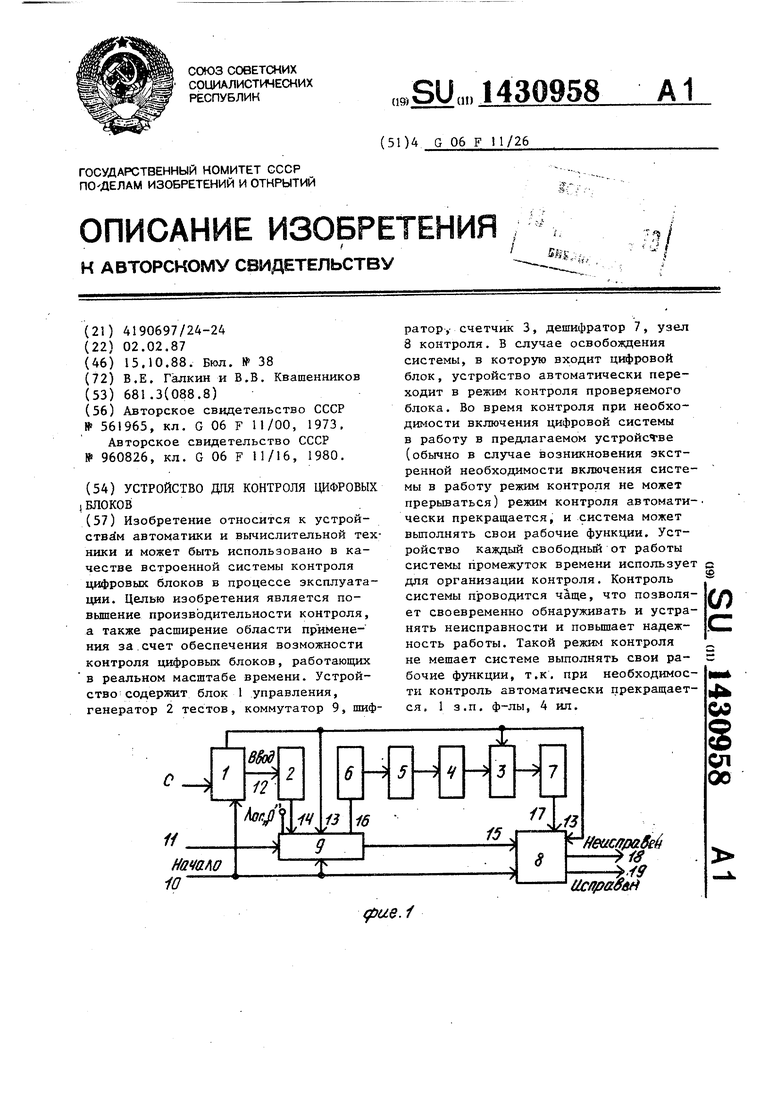

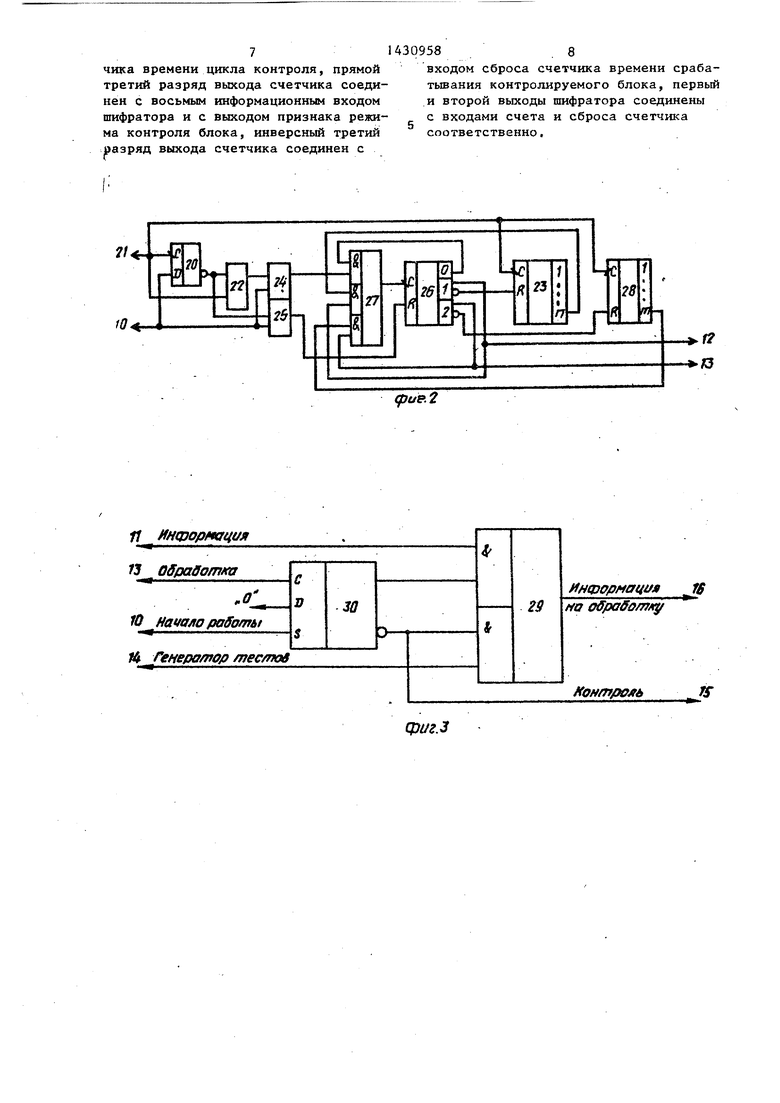

На фиг. 1 показана структурная схема предлагаемого устройства; на фиг. 2 - блок управления; на фиг, 3 коммутатор; на фиг. 4 - узел контроля

Устройство содержит блок.1 управления, генератор 2 тестов, счетчик 3, шифратор, содержащий элемент ИЛИ 4 и блок 5 предварительной обработки, контролируемый блок 6, дешифратор 7 ошибки, узел 8 контроля, коммутатор 9 вход 10 признака начала подачи реального воздействия устройства, вход 11 реального воздействия устройства, выход 12 смены теста блока управления, выход 13 режима контроля блока управления, выход 14 генератора тестов, . выходы 15 и 16 коммутатора, выход 17 дешифратора, выход 18 Неисправен и выход 19 Исправен,

Блок 1 управления содержит D-триг- гер 20, синхровход 21, элемент И 22, счетчик 23 времени срабатывания контролируемого блока, элемент ИЛИ 24, элемент И 25, счетчик 26, элемент ЗИ-ИЛИ 27 и счетчик 28 времени цикла контроля, при этом в блоке управления элементы 22, 24, 25 и 27 образуют шифратор.

Коммутатор 9 аодержит элемент ., 2И-ИЛИ 29 и D-триггер 30.

Узел 8 контроля содержит D-триггер 31 и элемент И 32.

Устройство работает следующим образом ,

Устройство может работать в режиме проверки цифровых блоков как в процессе их производства, так и в процессе эксплуатации по одному и тому же алгоритму.

При включении устройства все элементы устанавливаются в исходное состояние (цепи установки в исходное состояние не показаны). По окончании сигнала установки устройство находится в режиме контроля, при этом коммутатор 9 выдает сигнал 15, который яв

g

Q

5

5

ляется разрешающим для работы узла 8 контроля. Блок 1 управления формирует потенциальный сигнал 12 (являющийся разрешающим для формирования контрольной информации генератором 2 тестов) по которому генератор 2 тестов формирует контрольную информацию, поступающую через коммутатор 9 в блок 6. По окончании сигнала 12 блок 1 управления формирует потенциальный сигнал 13, в течение которого на выходе блока 6 формируется выходная контрольная информация, Выходная контрольная информация через блок 5 предварительной обработки информации, приводящий информацию к виду, удобному для контроля, и элемент или 4 поступает на счетный вход счетчика 3, Для контролируемого блока 6 число импульсов, появляющихся на выходе элемента ИЛИ 4 при правильной работе блока 6 в процессе контроля, заранее известно. Поэтому по истечении времени контроля счетчик 3 устанавливается в заранее определенное состояние, которое дешифрируется дешифратором 7, Время контроля заканчивается по окончании сигнала 13, задним фронтом которого в узле 8 контроля регистрируется состояние дешифратора 7.

При неисправнсэм состоян си контролируемого блока 6 или сбое в его работе на выходе дешифратора 7 присутствует единичный сигнал, который региг стрируется узлом 8 контроля как неисправность . При отсутствии импульса 10 устройство автоматически повторяет цикл контроля, описанный Bbmie. Подтверждение узлом 8 контроля сигнала ; неисправности свидетельствует о неисправном состоянии контролируемого блока 6, в противном случае был бы зафиксирован сбой устройства .

Устройство находится в режиме контроля постоянно, т.е. повторяются циклы контроля до момента прихода импульса 10. По этому импульсу коммутатор 9 снимает сигнал 15 и пропускает рабочую информацию в контролируе- мьш блок 6. Блок 1 управления по импульсу IО прерьшает цикл контроля и формирует сигналы I2 и 13 для рабочего цикла с начала и аналогично циклу контроля. В узле 8 контроля fиз-за прерывания цикла контроля) импульс 10 запрещает возможную выдачу сигнала неисправности, т.е. является установочным .

По окончании рабочего цикла, т.е. по окончании сигнала 13, коммутатор 9 формирует сигнал 15 и при отсутствии импульса 10 (отсутствие новой рабочей информации, необходимой для обработки контролируемым блоком 6) блок 1 управления автоматически начинает формировать циклы контроля. Контроль блока 6 продолжается до следую- щего поступления рабочей информации и т.д.

Таким образом, устройство заполняет промежутку времени между обработкой контролируемым блоком 6 рабочей информации циклами контроля.

Блок 1 управления, коммутатор 9 и узел 8 контроля работают следующим образом. При включении устройства все элементы устанавливаются в исходное состояние (как указывалось выше). Все триггеры устанавливаются по R-входу. Тактовая частота с синх- ровхода 21 блока 1 управления поступает через элементы И 22 к ИЛИ 24 на вход элемента ЗИ-ИЛИ 27, на другой вход которого поступает разрешение по начальной установке с выхода счетчика 26. Первый же импульс тактовой ,частоты задним фронтом по счетному входу переключает счетчик 26 и на его втором выходе формируется сигнал, который поступает на выход 12 и являетг ся разрешением по второму входу элемента ЗИ-ИЛИ 27. Кроме этого, со второго инверсного выхода счетчика 26 поступает сигнал разрешения на установочный вход счетчика 23, который считает импульсы, поступающие с синх- ровхода 21. При достижении определен- него числа, через время, необходимое для вьщачи теста генератором 2 тестов в контролируемый блок 6, сигнал с выхода счетчика 23 поступает на вход элемента ЗИ-ИЛИ 27 и переключает счетчик 26. На третьем выходе . счетчика 26 формируется сигнал Обработка, который поступает на выход 13 и вход элемента ЗИ-ИЛИ 27. Инверсный третий выход счетчика 26 является разрешающим по установочному входу счетчика 28, На счетный вход счетчика 28 поступают импульсы с синхровхо- да 21. При достижении определенного времени, необходимого для обработки теста контролируемым блоком 6, сигнал с выхода счетчика 28 поступает на вход элемента ЗИ-ИЛИ 27 и возвращает счетчик 26 в исходное состояние

5

0

5

Q

0

5

5

0

5

Цикл контроля автоматически повторяется при отсутствии сигнала Начало работы на входе 10.

D-триггер 30 при включении устройства устанавливается в состояние, при котором на его инверсном выходе формируется потенциальный сигнал, являющийся разрешающим для узла 8 контроля, который поступает на выход 15 и разрешает прохождение теста с выхода генератора 2 тестов на выход 16 и далее в контролируемый блок 6 через элемент 2И-ИЛИ 29.

По окончании обработки теста в контролируемом блоке 6 задним фронтом сигнала, поступающего на выход 13 по С-входу D-триггера, подтверждается состояние контроля D-триггера 30.

В узле 8 контроля сигнал с входа 17 (выходной сигнал дешифратора) поступает на D-вход D-триггера 31, При наличии разрешения (.сигнал на входе 15) на входе элемента И 32 (по окончании сигнала 13) опрашивается по С-входу D-триггер 31. При наличии едичного сигнала в этот момент на ,В-входе D-триггер 31 взводится, что свидетельствует о неисправности или сбое в работе контролируемого блока 6.. Если это сбой, то по окончании прохождения следующего контрольного теста D-триггер 31 устанавливается в исходное состояние,

По импульсу 10 (длительностью два или более периодов тактовой частоты на синхровходе 21), поступающему на . вход 10 блока 1 управления, D-вход D-триггера 20, первый и второй входы элементов ИЛИ 24 и И 25 счетчик 26 устанавливается сигналом с выхода элемента И 25 в исходное состояние, Импульс 10 устанавливает по входу сброса D-триггер 30, в результате чего сигнал снимается с выхода 15, С вь1хо да D- триггера 30 на вход элемента 2И-ИЛИ 29 поступает разрешение на прохождение рабочей-информации с входа 1 I по второму входу элемента 2И-ИЛИ 29 на вь1ход 16 и далее в контролируемый блок,

в узле 8 контроля импульс с входа 10 запрещает по входу сброса D- триггеру 31 выдачу ложного сигнала неисправности. Ложный сигнал мог бы сформироваться, когда импульс 10 поступает не в конце действия сигнала 13 (сиг нал 13 по импульсу .10 сиимается) и на входе 17 не сформирован сигнал с выхода дешифратора 7,

В блоке 1 управления сигнал установки с выхода элемента И 25 присутствует до первого заднего фронта тактового импульса, который по С-входу взводит D-триггер 20, Сигнал с инверсного выхода D-триггера ,20 по первому входу элементу И 25 снимает сигнал ю выход которого является выходом уст

установки счетчика 26 и по второму входу элемента И 22 запрещает прохождение тактов.

Таким образом, блок 1 управления находится в исходном состоянии и готов к формированию рабочего цикла. Рабочий цикл формируется по заднему фронту импульса 10 аналогично циклу контроля. Кроме того, после окончания импульса 10 D-трйггер 20 в блоке 1 управления устанавливается в исходное состояние и разрешает прохождение тактов через элемент И 22 для нового цикла контроля.

1о окончании рабочего цикла, т.е. по концу сигнала 13, D-триггер устанавливается в исходное состояние и с его инверсного выхода поступает сигнал 15. При отсутствии следующего импульса 10 блок 1 управления автома тически и непрерьшно начинает формировать циклы контроля.

Формула изобретения

5

0

ЗО

5

ройства для подключения к входу контролируемого цифрового блока,второй выход коммутатора соединен с вторым входом элемента И, выход которого соединен с С-входом D-триггера, D-вход которого соединен с выходом дешифратора ошибки, вход сброса D-триггера соединен с входом признака начала подачи реального воздействия устройства, с первым управляющим входом коммутатора, с входом логического условия блока управления, прямой и инверсный выходы D-триггера являются выходами Ошибки и Исправность устройства, вход синхронизации которого соединен с входом синхронзации блока управления, второй информационный вход коммутатора соединен с выходом генератора тестов. ,

55

чика времени цикла контроля, прямой третий разряд вькода счетчика соединен с восьмым информационным входом пгафратора и с выходом признака режима контроля блока, инверсный третий разряд выхода счетчика соединен с

Т Инфор оция

uSpaOo/nifa

С

Hava/io paSomiti

С л

30

П Генера/пор /пес/под

входом сброса счетчика времени сраба- тьшания контролируемого блока, первый и второй выходы шифратора соединены с входами счета и сброса счетчика соответственно.

(рие.2

29

Ннформацил Т6

на offpaffomf

/fOHfryjffJtu

ф1/г.З

| Устройство для обнаружения неисправностей цифровых систем | 1973 |

|

SU561965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых блоков | 1980 |

|

SU960826A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-15—Публикация

1987-02-02—Подача