4ii

ОО IvD

Изобретение предназначено для использования в системе управления нагревом и может быть применено в металлургии, химии, авиации.

Цель изобретения - повышение точности управления.

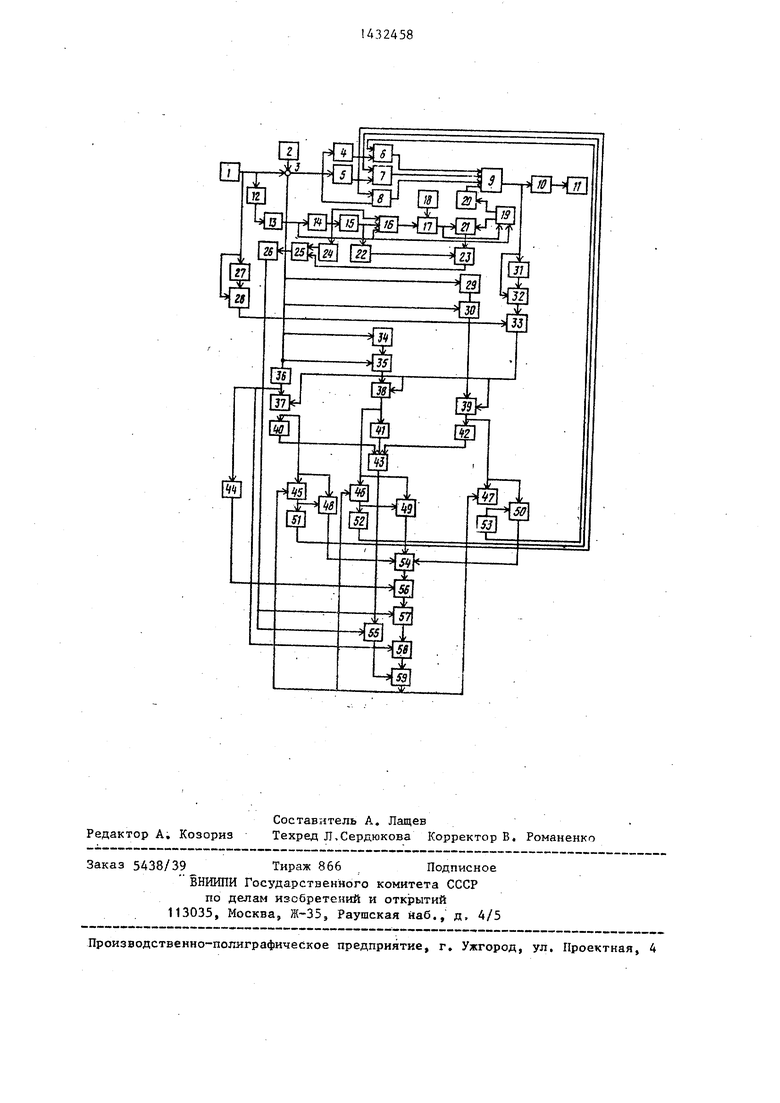

На чертеже приведена блок-схема самонастраивающегося регулятора.

Самонастраивающийся регулятор со- держит датчик I температуры, задат- чик 2 температуры, элемент . 3 сравнения, первый интегратор 4, первый дифференциатор 5, первый 6, второй 7 и третий 8 .блоки умножения, первый сумми- рующий усилитель 9, третий усилитель 10, исполнительный элемент 11, второй дифференциатор 12, компаратор 13, первый 14 и второй 15 блоки импульс-, ной задержки, первый элемент ИЛИ 16, первый элемент И 17, генератор 18 импульсов, триггер 19, формирователь 20 импульсов, второй элемент И 21, второй элемент ИЛИ 22, счетчик 23, третий элемент ИЛИ 24, третий эле- мент И 25, цифроаналоговый преобразователь (ЦАП) 26, второй блок 27 временной задержки, третий суммирующий усилитель 28, второй интегратор 29, седьмой блок 30 умножения, первый блок 31 временной задержки, второй суммирующий усилитель 32, первый блок 33 деления, третий дифференциатор 34 четвертый блок 35 умножения, второй квадратор 36, шестой 37, пятый 38 и восьмой 39 блоки умножения, третий 40, первый 41 и четвертый 42 квадраторы, четвертый суммирующий усилитель 43, четвертый дифференциатор 44, девятьй 45, десятый 46, одиннадцатый 47, четырнадцатый 48, шестнадцатый 49 и пятнадцатый 50 блоки умножения, третий 51, четвертый 52 и пятый 53 интеграторы, пятьй суммирующий усилитель 54, двенадцатьй блок 55 умножения, шестой суммирующий усилитель 56, тринадцатый блок 57 умножения, седьмой суммирующий усилитель 58 и второй блок 59 деления,.

Самонастраивающийся регулятор ра- ботает следующим образом.

На вход элемента сравнения поступают сигналы: первый от задатчика температуры, второй от датчика пературы. Разность этих сигналов (t) поступает на первый вход третьего блока умножения, вход первого дифференциатора, вход первого интегратора

На второй вход третьего блока умножения поступает сигнал K.(t + 2) с выхода третьего интегратора. На выходе третьего блока умножения образуется сигнал, пропорциональный

К,e(t).

с выхода первого дифференциатора сигнал (t) поступает на первый вход второго блока умножения, на второй вход которого поступает сигнал K(t + С ) с выхода четвертого интегратора, а на входе блока образуется сигнал, пропорциональный К (t +) (t)

С выхода первого интегратора сигнал (t)dt поступает на первый вхо

о

первого блока умножения, на второй вход которого поступает сигнал К j(t + Z ) с выхода пятого интегратора, а на выходе блока 6 образуется сигнал, пропорциональный t

Kj(t + 1) 5 E(t)dt,

С выходов первого, второго, тре- тьего блоков умножения сигналы поступают на входы первого суммирующего усилителя, с выхода которого сигнал, пропорциональньй

U(t) K,(t -t- t)(t) +

+ K(t +t)(t) + Kj(t + t;) JE(t)dt,

о

поступает на вход усилителя 10, а с его выхода - на исполнитальпьй элемент 11,

Генератор 18 вырабатьшает непре- рьшные прямоуго тьные импульсы, которые с его выхода поступают на первый вход элвмента 17, При наличии разрешающего сигнала на втором входе элемента 17, который поступает с выхода элемента 16, на выходе элемента 17 появляются импульсы. Первый импульс с выхода элемента 17 переводит триггер 19 в единичное состояние. Срабатывание триггера 19 обеспечивает запуск формирователя 20 импульсов и прохождение импульсов через элемент 21 на счетчик 23, Импульс с выхода формирователя 20 импульсов поступает на вход первого суммирующего усилителя 9, в котором суммируется с основным сигналом управления регулятора.

Момент реакции объекта управления на прямоугольньй импульс определяет

ся с ПОМОЩЬ второго дифференциатора 12, вход которого соединен с выходом датчика 1 температуры, и компаратора 13, вход которого соединен с выходом дифференциатора 12. Для устранения появления на выходе компаратор 13 ложного сигнала на его вход подается опорньш сигнал, равный (T.jg)ya на у шстке управления. Импульс с вы- хода компаратора 13 пбступает на второй вход триггера I9 и переводит его в нулевое состояние. Одновременно импульс с выхода компаратора 13 поступает через элемент I6 на второй вход элемента 17. В результате этого запрещается прохождение импульса с генератора 18 на триггер 19 и элемент 21. Импульс с выхода компаратора 13 после прохождения через первый блок 14 импульсной задержки поступает через элемент 24 на второй вход элемента 25. Код- со счетчика 23 пе- реписьшается в регистр цифроаналого- вого преобразователя 26, Последний преобразует код в напряжение, пропорциональное времени 1, определяемое инерционностью объекта управления. Импульс с выхода первого блока 14 импульсной задержки поступает на вход второго блока 15 импульсной задержки, выходной импульс которого переводит триггеры счетчика 23 в нулевое состояние. После обнуления счетчика 25 процесс определения может быть повторен.

Длительность задержки импульсов подбирается при наладке схемы. Перед началом работы регулятора на входы элементов 22 и 24 подаются импульсы для обнуления счетчика 23 и цифро- аналогового преобразователя 26. Для запуска схемы по определенно време- . ни ll, определяемого инерционностью объекта управления, на вход элемента 17 подается сигнал запуска в виде постоянного единичного сигнала. Схем определения Z с помощью импульсов Сброс счетч1жа и Запись в регистр ЦАП приводится в исходное состояние перед началом работы.

5

Q о

С выхода суммирующего усилителя 9 сигнал U(t) поступает на вход бло- ка 31 временной задержки и первый вход суммирующего усилителя 32, на выходе которого образуется сигнал, пропорциональный разности U(t) - U(t - f, ).

На входы первого блока 33 деления поступают сигналы с выходов усилителей 28 и 32. На выходе первого блока 33 деления образуется сигнал, пропорциональный

IllKi t} (t)()

JU

u(t) - u(t

- P.

)

с выхода элемента 3 сравнения сигнал (t) поступает на вход квадратора 36, с выхода которого сигнал Е (t) поступает на первый вход блока 37 умножения,, на второй вход котор.,го поступает сигнал

II(Kjlt)

эи

пропорциональный С вывыхода первого блока 33 деления. На входе блока 37 образуется сигнал,

5.t (Kji.t)

aici,

хода элемента 3 сравнения сигнал 5(t) поступает на вход третьего дифференциатора 34 и второй вход блока 35 умножения. С выхода третьего дифференциатора 34 сигнал (t) поступает на первый вход блока 35 умножения, на выходе которого образуется сигнал (t). f (t). На входы блока 38 умножения поступают сигналы с выходов блоков 33 и 35.

На выход блока 38 умножения образуется сигнал, пропорциональный

---Tf-- (( -- fe d к йи

С выхода элемента 3 сравнения сигнал (t) поступает на вход второго интегратора 29 и второй вход блока 30 умножения, на первый вход которого поступает сигналJ(t)dt с выхода второго интегратора 29. На выходе блока 30 умножения образуется сигнал

(t)S(t)dt.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2013 |

|

RU2544312C1 |

| Тензометрическое устройство | 1991 |

|

SU1796890A1 |

| Многоканальная система экстремального регулирования | 1974 |

|

SU528544A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2006 |

|

RU2307344C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2009 |

|

RU2392612C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 1996 |

|

RU2108568C1 |

| Устройство для моделирования удара твердых тел | 1988 |

|

SU1567889A2 |

| Частотно-управляемый электропривод | 1989 |

|

SU1720138A1 |

| СИСТЕМА АДАПТИВНОГО УПРАВЛЕНИЯ НЕСТАЦИОНАРНЫМИ НЕЛИНЕЙНЫМИ ОБЪЕКТАМИ | 1990 |

|

RU2031434C1 |

| Устройство для идентификации объекта | 1985 |

|

SU1298718A1 |

Изобретение предназначено для использования в системе управления нагревом и может быть применено в металлургии, химии, авиации. Цель изобретения - повышение точности управления. Параметры регулятора определяют в ходе управления градиентным Ь етодом с переменным шаговым множителем запаздьшания объекта управления с учетом инерционности объекта управления. Запаздьшание объекта управления находят путем определения момента реакции объекта управления на прямоугольный импульс, вырабатьша- емый Генератором и фОрмИройателем импульсов. 1 ил.

С выхода датчика 1 температуры сигнал, пропорциональный Tg(t), поступает на вход блока 27 временной . задержки и первый вход с мкпр тощего усилителя 28, на выходе которого образуется сигнал, пропорциональный разности Tg(t) - Tg(t - -2 ) .

5

На входы блока 39 умножения поступают сигналы с выходов блоков 30 и 33. На.выходе блока 39 образуется сигнал, пропорциональный

) р.,ч iTilKjitb ,

iv , j

-ЭК

3

аи

«(t)dt.

С выхода блока 37 умножения сигналы поступают на вход квадратора АО, на выходе которого образуется

1Ж :

С выхода блока 38

ум/ -5 si

сигнал ()

ноження поступает на вход

квадратора 41, на выходе которого 2 разуется сигнал (;--) . С выхода

c Kj

восьмого блока 39 умножения сигнал поступает на вход квадратора 42, на выходе которого образуется сигнал

Сигналы с выходов блоков AGf---)2 5К/

42 поступают на входы суммирующего усилителя 43, на выходе которого образуется сигнал, пропорциональный 3

У ()

,

5

пропорциональный

(fl). dK/

С выхода блока 43 сигнал поступает на первый вход блока 55 умножения на второй вход которого поступает сигнал с выхода цифроаналогового преобразователя, пропорциональный 2 , На выходе блока 55 образуется сигнал,

3

I

с выхода блока 37 сигнал поступает на первый вход блока 48 умножения на второй вход которого поступает сигнал, пропорциональный-К), На выхо де блока 48 образуется сигнал

ЗФ .

Т--К , С выхода блока 38 сигнал по оК 1

ступает на первый вход блока 49 умножения, на второй вход которого поступает сигнал, пропорциональный К, На выходе блока 49 образуется сиг- (9Ф .

выхода блока 39 сигнал поступает на первый вход блока 50 умножения на второй вход которого поступает сигнал, пропорциональный kj. На выходе блока 50 образуется сигнал

- - ЗК/3

с выходов блоков 48-50 сигналы поступают на входы суммирующего усилителя 54, на выходе которого обра3 1ф .

зуется сигнал - Z, ---К .,

iil dK; 1

с выхода квадратора 36 сигнал поступает на вход дифференциатора 44, на выходе которого образуется сигнал ф, На входы суммирующего усилисигналы с выходов

56 образуется

теля 56 поступают блоков 44 и 54,

На выходе усилителя

$Ф , 4 т сигнал -- - Z --К.,

Сигналы с выходов блоков 26 и 56 поступают на входы блока 57 умножения, на выходе которого образуется

Ф

сигнал -Г--1-, На входы суммирующего с t

усилителя 58 поступают сигналы с выходов блоков 36 и 57. На выходе усилителя 58 образуется сигнал, пропор 94 .

циональныи

ФоЧ + -- а t

который пос0

5

0

5

0

5

0

5

тупает на первый вход второго блока 59 деления, на второй вход которого

, ЗФ .2 поступает сигнал t, 2- (---) с выхода

.1

блока 55, На выходе блока 59 образуется сигнал, пропорциональный

)(t.o (ф | ;/4/4

который поступает на вторые входы блоков 45-47 умножения.

На первый вход блока 45 умножедФ

НИН поступает сигнал - --- с выхода

5К,

блока 27 умножения. На выходе блока 45 образуется сигнал ), который поступает на вход интегратора 51, на выходе которого образуется сигнал + S ), которьм затем поступает на второй вход блока 8 умножения.

На первый вход блока 46 умножения

поступает сигнал - --- с выхода блооК

ка 38 умножения. На выходе блока .46 образуется сигнал K(t + С), который поступает на вход интегратора 52, на выходе которого образуется сигнал K/j(t + C), который затем поступает на второй вход блока 7 умножения, На первый вход блока 47 умножения

аф

поступает сигнал - --- с выхода бловК }

ка 39 умножения. На выходе блока 47 образуется сигнал K,(t ), который поступает на вход интегратора 53, на выходе которого образуется сигнал K.(t + 2), которьш затем поступает на второй вход блока 6 умножения. Определение параметров регулятора

K,(t + С),

KjCt

i),

Kj(t

) в

процессе управления с учетом инерционности объекта градиентньм методом с переменным шаговьм множителем позволяет повысить точность управления,

Формула изобретения Самонастраивающийся регулятор, содержащий датчик температуры и задат- . Q двенадцатый блок умножения, послечик температуры, последовательно соединенные элемент сравнения, первый дифференциатор;.второй блок умноже- HIл, последовательно соединенные первый суммирующий ус илитель, усилитель, 5 тель, соединенный выходом с входом делимого второго блока деления, а также четвертый дифференциатор, четырнадцатый блок умножения, пятнадцатый блок умножения, шестнадцатый блок умножеисполнительныи элемент, последовательно соединенные первый.интегратор и первый блок умножения, задатчик температуры соединен с неинвертирующим входом элемента сравнения, йыход датчика температуры соединен с инвертирующим входам элемента сравнения, выход которого соединен с входом первого интегратора, первым входом третьего блока умножения, а выходы первого, второго, третьего блоков умножения соединены с соответствующими входами первого суммирующего .усилителя, о т л и - чающийс я тем, ч то, с целью Повышения точности управления, в него включены первый и второй блоки деления, последовательно соединенные второй дифференциатор, компаратор, первый- блок импульсной задержки, второй блок импульсной задержки, последовательно соединенные первый элемент ИЛИ, первый элемент И, последова- } ельно соединенные триггер и формирователь импульсов, последовательно, соединенные второй элемент И, -счетчик, третий элемент И и цифроаналоговьгй преобразователь, последовательно соединенные первый блок временной задержки и второй суммирующий усили- .тель, последовательно соедккенные второй блок временной задержки, третий суммирующий усилитель, соединенный выходом с входом делимого первого блока деления, последовательно соединенные третий дифференциатор, четвертьй блок умножения, пятьш блок умножения, первый квадратор, последовательно соединенные второй квадратор, шестой блок умножения, третий квадратор, последовательно соедине н- ные второй интегратор, седьмой блок умножения, восьмой блок умножения, четвертый квадратор, последователь20

ния, второй и третий элементы ИЛИ,

30

35

генератор, выходы третьего и седьмого суммирующих усилителей соединены с входами делимого соответственно : первого и второго блоков деления, вы- 25 ход датчики температуры соединен с входом второго дифференциатора, выход компаратора соединен с первым входом первого элемента ИЛИ и вторым входом триггера, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом первого элемента И, выход первого блока импульсной задержки соединен с третьим входом первого элемента 1ШИ, входом третьего элемента ИЛИ, выход которого соединен с вторым входом третьего элемента И, выход второго блока импульсной задержки соединен с входом второго элемента ИЛИ, выход которого соединен с вторым входом счет -1ика, а выход генератора соединен с вторым входом первого элемента И, выход формирователя 1мпульсов соединен с входом первого суммируюп;его усилителя, выход цифроаналогоБого преобразователя соединен с вторым входом двенадцатого блока умножения и вторым входом тринадцатого блока умножения, вход второго блока временной задержки соединен с выходом датчика температуры и первьп- входом третьего суммирующего усилителя, выход первого суммирующего усилителя соединен с входом первого блока временной задержки и пер- входом второго суммирующего усилителя, выход которого соединен с входом делителя первого блока деления, выход которого соединен с вторы40

45

50

65

но соединенные девятый блок умножения, третий интегратор, последо-. вательно соединенные десятый блок т-пюжения и четвертьш интегратор, последовательно соединенные одиннадцатый б.лок умножения и пятый интегратор, последовательно соединенные четвертый су мирующий усилитель и

ловательно соединенные пятый суммирующий усилитель, шестой суммирующий усилитель, тринадцатый блок умножения, седьмой суммирующий усили20

ния, второй и третий элементы ИЛИ,

0

5

генератор, выходы третьего и седьмого суммирующих усилителей соединены с входами делимого соответственно : первого и второго блоков деления, вы- 5 ход датчики температуры соединен с входом второго дифференциатора, выход компаратора соединен с первым входом первого элемента ИЛИ и вторым входом триггера, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом первого элемента И, выход первого блока импульсной задержки соединен с третьим входом первого элемента 1ШИ, входом третьего элемента ИЛИ, выход которого соединен с вторым входом третьего элемента И, выход второго блока импульсной задержки соединен с входом второго элемента ИЛИ, выход которого соединен с вторым входом счет -1ика, а выход генератора соединен с вторым входом первого элемента И, выход формирователя 1мпульсов соединен с входом первого суммируюп;его усилителя, выход цифроаналогоБого преобразователя соединен с вторым входом двенадцатого блока умножения и вторым входом тринадцатого блока умножения, вход второго блока временной задержки соединен с выходом датчика температуры и первьп- входом третьего суммирующего усилителя, выход первого суммирующего усилителя соединен с входом первого блока временной задержки и пер- входом второго суммирующего усилителя, выход которого соединен с входом делителя первого блока деления, выход которого соединен с вторы0

5

0

5

ми входами шестого, пятого и восьмого блоков умножения, выход элемента сравнения соединен с входом второго интегратора, вторым входом седьмого блока умножения, входом третьего дифференциатора, вторым входом четвертого блока умножения, входом второго квадратора, выход которого соединен с входом четвертого дифференциатора и вторым входом седьмого суммирующего усилителя, выход четвертого дифференциатора соединен с вторым входом шестого суммирующего усилителя, выход шестого блока умножения со- 15 блока умножения, выход которого соеединен с первыми входами девятого и четырнадцатого блоков умножения, второй вход девятого блока умножения соединен с выходом второго блока деления, выход девятого блока умно- жения соединен с вторым входом четырнадцатого блока умножения, выход которого соединен с вторым входом пятого суммирующего усилителя, выход пятого блока умножения соединен с пер- выми входами десятого и шестнадцато-

го блоков умножения, второй вход десятого блока умножения соединен с выходами второго блока деления, выход десятого блока умножения соединен с вторым входом шестнадцатого блока умножения, выход восьмого блока умножения соединен с первыми входами одиннадцатого и пятнадцатого блоков умножения, второй вход одиннадцатого блока умножения соединен с выходом второго блока деления, выход одиннадцатого блока умножения соединен с вторым входом пятнадцатого

динен с третьим входом пятого суммирующего усилителя, выходы первого, третьего, четвертого квадраторов соединены с входами четвертого суммирующего усилителя, выход двенадцатого блока умножения соединен с входом делителя второго блока деления, выходы третьего, четвертого, пятого интеграторов соединены с вторыми входами соответственно третьего, второго и первого блоков умножения.

| Устройство для управления нагревом | 1979 |

|

SU851386A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Программный регулятор температуры | 1978 |

|

SU699501A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-10-23—Публикация

1986-07-11—Подача