со

00 СХ5

00

ел

со

Изобретение относится к вычислительной технике и может найти применение при создании спгщиализирован- ных систем переработки цифровой ий- формации.

Целью изобретен11я является повышение точности вычислений.

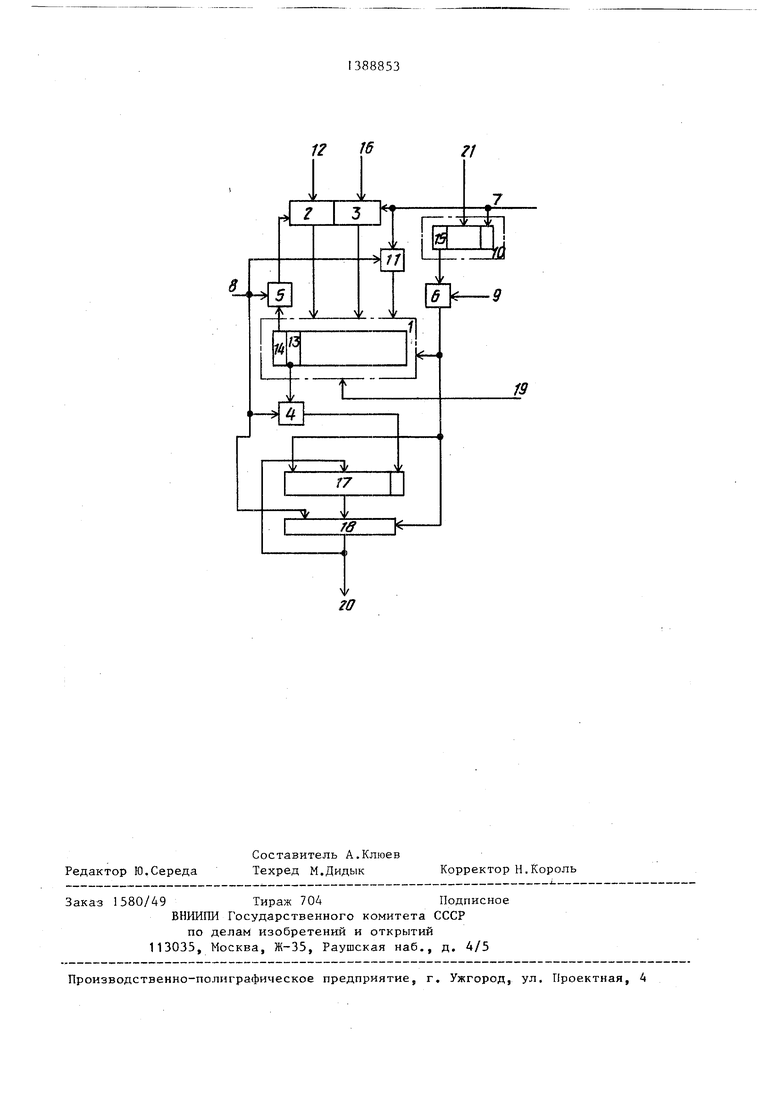

На чертеже представлена схема предлагаемого устройства для деления чисел с фиксированной запятой.

Устройство содержит сумматор 1, блоки 2 и 3 элементов И, элементы И 4-6, тактовые входы 7-9 устройства счетчик 10 аргумента, элемент ИЛИ 11 прямой вход 12 дешителя устройства, инверсный выход 13 знакового разряда .сумматора 1, прямой выход 14 знакового разряда сумматора 1, инверсный выход 15 знакового разряда счетчика 10 аргумента, инверсный вход 16 делителя устройства, счетчик 17 частного регистр 18, вход 19 делимого устройства, выход 20 частного устройства. Вход 21 аргумента устройства, ; На тактовые входы 7-9 устройства поступает последовательность импульсов.

Алгоритм работы устройства для по лучения п-разрядного частного следую щий.

Выполняется г циклов формирования старших разрядов частного. При этом в каждом цикле: от аргумента г вычи тается единица;; по формуле х х + у вычисляется остаток; по формуле

Zc

.. fz.-H,

Zj.+ при X ёО,

формируются значения старших разрядов частного и, если полученный оста ток X меньше нуля, то по формуле X х+у производится его восстановление .

Вьтолняется п-г циклов определения младших разрядов частного.

Устройство работает следующим образом.

Для реализации деления делимое х напра вляется в сумматор 1 , делитель у - на входы 12 и I6 делителя, аргумент (-г) масштабного множителя, представленный в дополнительном коде, - в счетчик 10 аргумента. Пусть необходимо реализовать пример

«-3

Z

gjoio

0,0110

5 0 5

0

с

0

5

0 5

в этом случае на входе 12 делителя будет находиться код 0,0110, в сумматоре - I - 0,1010, в счетчике аргумента -1,101.

Для определения () цифр частного выполняется 4 цикла деления. Для () первых циклов устройство работает следующим образом.

В первом такте (тактовый вход 7) каждого цикла из кода на сумматоре 1 вычитается делитель и производится прибавление единицы, к содержимому счетчика 10 аргумента. Во втором такте (тактовый вход 8) в случае, если на сумматоре 1 остаток положителен, то по переднему фронту сигнала с- тактового входа 8 на счетный вход счетчика 17 поступает единица. Кроме того, по заднему фронту сигнала с тактового входа 8 производится запись содержимого счетчика 17 на регистр 18, и, если на сумматоре 1 остаток отрицателен, то производится его восстановление (к остатку прибавляется делитель).

По третьему такту для г первых циклов в устройстве арифметические и логические действия не производятся.

Для последующих циклов в первом и втором такте устройство работает аналогично описанному. По третьему такту на входе элемента И 6 возникает сигнал, по переднему фронту которого производится сдвиг на один разряд влево содержимого сумматора I и регистра 18, а по заднему фронту этого сигнала производится перезапись содержимого регистра 18 на счетчик 17.

Для нашего примера формирование частного на выходном регистре 18 в зависимости, от содержимого сумматора 1, счетчика 10 аргумента и счетчика 17 происходит следующим образом.

В первом цикле деления по сигналу. (тактовый вход 7) инвертированное значение делителя с входа 16 (1,1001) складывается с содержимым сумматора 1 (0,1010). На сумматоре 1 образует ся код 0,0100. По переднему фронту сигнала (тактовый вход В) на выходе первого элемента И 4 возникает единичный сигнал, по которому на счетный вход счетчика I7 поступает единичный сигнал. На счетчике 17 образуется код 0001, который по заднему

фронту сигнала (тактовый вход 8) переписывается на регистр 18.

Во втором цикле деления по сигналу (тактовый вход 7) на сумматоре 1 формируется отрицательный код 1,1101 а на счетчике 10 аргумента - код 1111. По переднему фронту сигнала (тактовый вход 8) производится восстановление остатка х 1,1101 и на сумматоре 1 образуется код 0,0100.

В третьем цикле деления по сигналу (тактовый вход 7) на сумматоре 1 (формируется отрицательный код 1,1101 а на счетчике 10 аргумента - код 0000. По переднему фронту сигнала (тактовый вход 8) произвЬдится восстановление остатка X и на сумматоре 1 образуется код 0,0100. По переднему фронту сигнала (тактовый вход 9) производится сдвиг на один разряд влево содержимого сумматора 1 и регистра 18, На сумматоре 1 образуется код 0,1000, а на регистре 18-код 0,0010, По заднему фронту этого сиг- нала содержимое регистра 18.переписывается на счетчик 17,

В четвертом цикле деления по сигналу (тактовый вход 7) на сумматоре I образуется код 0,0010. По переднему фронту сигнала (тактовый вход 8) на выходе первого элемента И 4 возникает сигнал, по которому на счетный вход счетчика I7 поступает единичный сигнал. На счетчике 17 образуется код 0011, который по заднему фронту переписывается на регистр 18, По переднему фронту третьего сигнала (тактовый вход 9) содержимое регистра 18 сдвигаетс я на один разряд влево.

После окончания четвертого цикла на регистре 18 будет сформирован код 00110, который после добавления зна- кового разряда (формирование знакового разряда не рассматривается) будет иметь вид 0,00110,.

Среднекзвадратическая ошибка деле- ния по алгоритму предлагаемого уст- ройства может быть определена по формуле

для X 1 , у

/иик

2- ,

g

r 0 5

о .-.

5

5

Формула изобретения

Устройство для деления чисел с фиксированнор запятой, содержащее сумматор, два блока элементов Pi, три элемента И, счетчик аргумента и регистр, причем вход делимого устройства соединен с установочным входом сумматора, вход разрешения сдвига влево которого соединен с входом разрешения сдвига влево регистра, выход которого является выходом частного устройства, вход аргумента которого соединен с установочным входом счетчика аргумента, прямой и инверсный входы делителя устройства соединены соответственно с первыми входами первого и второго блоков элементов И, выходы которых соединены соответственно с входами первого и второго слагаемых сумматора, инверсный и прямой выходы знакового разряда которого соединены соответственно с первыми входами первого и второго элементов И, первый тактовый вход устройства соединен с вторым входом второго блока элементов И, второй тактовый вход устройства соединен с вторыми входами первого и второго элементов И, выход второго элемента И соединен с вторым входом первого блока элементов И, инверсный выход знакового разряда счетчика аргумента соединен с первым входом третьего элемента И, второй вход которого соединен с третьим тактовым входом устройства, отличающееся тем, что, с целью повышения точности вычислений, оно содержит счетчик частного и элемент ИЛИ, причем первый тактовый вход устройства соединен со счетным входом счетчика аргумента и с первым входом элемента 1ШИ, выход которого соединен с входом разрешения сложения сумматора, вход разрешения сдвига влево которого соединен с выходом третьего элемента И, и с входом разрешения записи счетчика частного, второй тактовый вход устройства соединен с вторым входом элемента ИЛИ и с входом разрешения записи регистра, в ыход которого соединен с информационным входом счетчика частного, выход которого соединен с информационным входом регистра, выход первого элемента И соединен со счетным входом счетчика частного.

12 16

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел с фиксированной запятой | 1982 |

|

SU1059570A1 |

| Устройство для деления чисел с фиксированной запятой | 1986 |

|

SU1417009A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления чисел | 1985 |

|

SU1287149A1 |

| Устройство для вычисления дробнойРАциОНАльНОй фуНКции | 1979 |

|

SU842796A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Цифровой анализатор спектра | 1978 |

|

SU734579A1 |

Изобретение относится к цифровой вычислительной технике и может найти применение в специализированных системах обработки информации. Цель изобретения состоит в повышении точности вычислений. Поставленная цель достигается тем, что устройство для деления чисел с фиксированной запятой, содержащее сумматор 1, блоки 2, 3 элементов И, элементы И 4, 5, 6, счетчик 10 аргумента и регистр 18, содержит элемент ИЛИ 11 и счетчик 17 частного с соответствующими связями. 1 ил.

| Устройство для деления двоичных чисел | 1984 |

|

SU1203514A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU105A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-15—Публикация

1986-11-20—Подача