(46) 30.12.90. Бгал. № 48 j . . „.

(21)4159621/24-24

(22)31.10.86

(72) Б.И.Кобозев, М.В.Харитонов,

А.Н.Ильин, С.В.Корнеев и Л.П.Яковлев

,(5.3) 681.325 (088.8)

(56)Заявка Франции №2431733, кл. G 06 F 9/4б, опублик. 1983.

. Патент США № 4356550, кл. G 06 F 11/20, опублик. 1984.

; (54) МНОГОПРОЦЕССОРНАЯ СИСТЕМА ОБРА- .. БОНШ ДАННЫХ . ,

(57)Изобретение относится к вычислительной технике, в частности к архитектуре высокопроизводительных, многопр оцессорпых систем обработки данных. Целью изобретения является расширение класса решаемых задач, повышение производительности и надежности многопроцессорной системы обработки данных при работе в ип роком диапазоне объемов обрабатывае1.{ых данных. Многопроцессорная система содержит две шины 1, 2 межпроцессорного обмена, устройства 3, 4 управления шинами мехспроцессорного обмена, процессорные модули, локальные шины 17, блоки 5 общей памяти, устройства 10 управления вводом-выводом. 1 з.и. ф-лЫ, 1 ил..

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОПРОЦЕССОРНАЯ СИСТЕМА ОБРАБОТКИ ДАННЫХ | 1997 |

|

RU2139566C1 |

| Многопроцессорная система | 1988 |

|

SU1605247A1 |

| СПОСОБ ФИЛЬТРАЦИИ МЕЖПРОЦЕССОРНЫХ ЗАПРОСОВ В МНОГОПРОЦЕССОРНЫХ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМАХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2189630C1 |

| Многопроцессорная система | 1990 |

|

SU1709330A1 |

| КОМПЬЮТЕРНАЯ СИСТЕМА И СПОСОБ ПЕРЕДАЧИ ДАННЫХ В КОМПЬЮТЕРНОЙ СИСТЕМЕ | 1999 |

|

RU2220444C2 |

| Устройство обработки данных для многопроцессорной системы | 1988 |

|

SU1683039A1 |

| Многопроцессорная система | 1988 |

|

SU1522228A1 |

| МНОГОПРОЦЕССОРНЫЙ КОНТРОЛЛЕР ДЛЯ УПРАВЛЕНИЯ СЛОЖНЫМ ТЕХНОЛОГИЧЕСКИМ ОБЪЕКТОМ | 2003 |

|

RU2263952C2 |

| ИСПОЛЬЗОВАНИЕ АУТЕНТИФИЦИРОВАННЫХ МАНИФЕСТОВ ДЛЯ ОБЕСПЕЧЕНИЯ ВНЕШНЕЙ СЕРТИФИКАЦИИ МНОГОПРОЦЕССОРНЫХ ПЛАТФОРМ | 2014 |

|

RU2599340C2 |

| Устройство для запоминания трассы функционирования многопроцессорных систем | 1990 |

|

SU1737454A1 |

L«JL«J

С.Ж«J

Изобретение относится к вычислительной технике, в частности ,к архитектуре высокопроизводительных мно- гоггроцессорных систем обработки дан- ных.

Целью изобретения является расширение класса решаемых задач, повышение производительности и надежности процессорной системы обработки данных при работе в широком диапазоне объемов обрабатываемых данных.

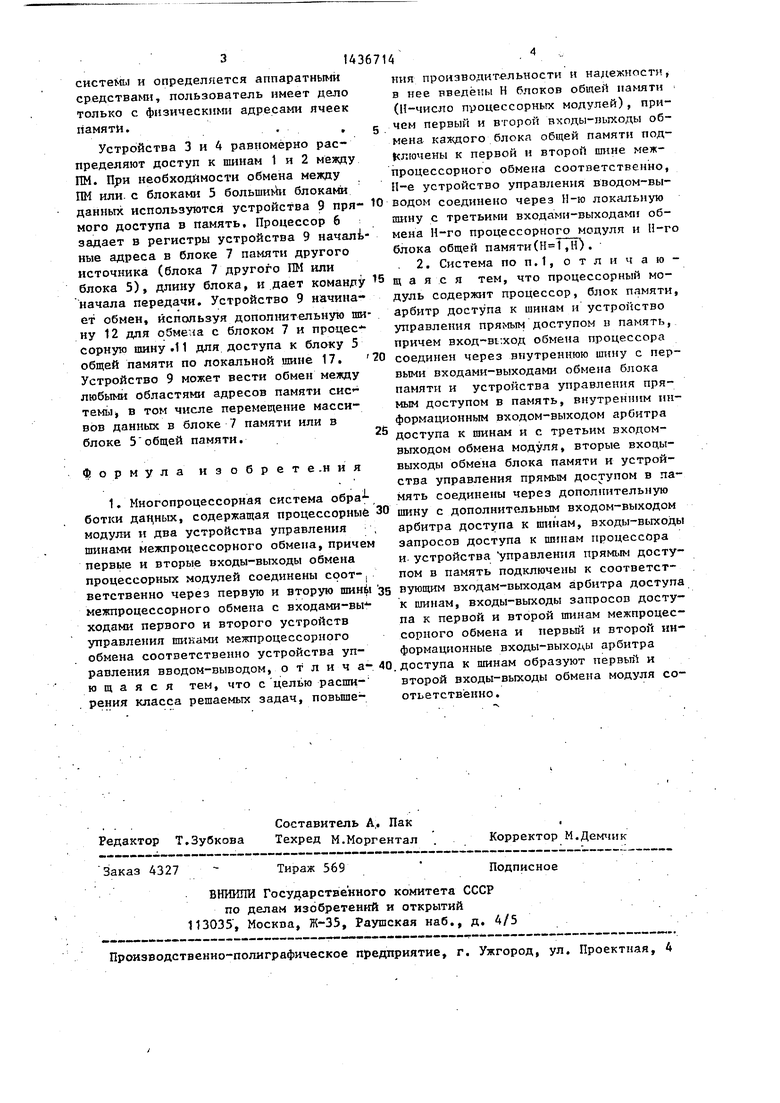

На чертеже приведена структурная схема многопроцессорной системы обработки данных. :

Система содержит две шины 1, 2 , межпроцессорного обмена, устройства 3 и А управления шинами межпроцессорного обмена,.бло1Ш 5 общей памяти с тремя входами-выходами, к шинам 1 и 2 межпроцессорного обмена подютю- чены процессорные модули, содержащие процессор 6, блок 7 памяти, арбитр 8 к шинам, устройство 9 управления прямым доступом в память; уст- ройства 10 управления вводаг вывода. Процессор 6, арбитр 8;-доступа к ши- .нам, блок 7 и устройство 9 подключены к внутренней шине 11, а вторые вхомы-выходы блока 7 и устройства 9 подключены к дополнительной шине 12. С помощью арбитра 8 доступа к шинам ведется обмен информацией между уст- ройствами на шинах 1, 2,11, 12, для арбитража доступа к которым арбитр 8; связан по линиям 13, 14 запроса дос- тупа с Устройством 9 и процессором 6 соответственно/ И .по линиям 15, 1б с устройствами 3, 4.

Внутренняя шина 11 может быть сое динёна (при необходимости) С локальной атной 17, к которой присоединяются третий вход-выход обмена блока 5 и устройства 10,

Предлагаемая система функционирует следующим образом.

При инигщализации системы производится загрузка операционной системы либо из устройства 10, либо из посто- « янной памяти (одного из блоков 3). С устройств 10 инициируется определенная задача, которая загружается в процессорные модули (Щ). В процессе выполнения задачи имеют место обмены данньп- между отдельными подзадачами, выполняемь ми разными Г1М.

Рассмотрим обмен одного 1Ш с блоком 7 другого ИМ. Процессор 6 или .устройство 9 первого ИМ обращаются по

конкретному адресу в адресном пространстве системы, относящемуся к адресам второго ОМ, вьщавая сигнал о зап- росе доступа на шинЬт 11 или 12, арбит 8 по соответствующим линиям 13, 14. Арбитр 8 первого ПМ анализирует каждый адрес при обменах по шинам 1, 2, 11, 12. Если адрес данных находится за пределами внутренней шины 11, ло- кальной шины 17, то арбитр 8 передаст запросы на захват шин 1 и 2 устройствами 3 и 4 по соответствующим линиям 15, 16. Первое из освободившихся от обменов по шинам i, 2 межпроцессорного обмена устройство 3 или 4 miiH межпроцессорного обмена разрешает захват шины 1 или 2 межпроцессорного обмена первому ПМ. Арбитр 8 предоставляет доступ процессору 6 или устройству 9 к соответствующей шине 1 или 2 межпроцессорного обмена по шине 11 или по Шине 12 и первый ПМ на захваченной шине 1 или 2 организует цикл обращения, в котором на шину 1 или 2 выставляютс адрес и данные, поступающие с процессора 6 или устройства 9. Этот адрес анализируется арбитрами 8 всех ПМ, а ПМ, которому принадлежит указанный адрес, организует доступ к указанному адресу в своем адресном пространстве (ячейки памяти 7, регистры управления устройства 9, регистры устройства 10) по шине 11 или 12, причем если обмен направлен к блоку 7, то доступ организуется по дополнительной шине 12, в ином случае - по внутренней шине 11, приостанавливая на время одного обмена работу процессора 6. Если процессор 6 второго ПМ обращается для обме- jfia к другому модулю, то производится аналогичная процедура захвата второй шины межпроцессорного обмена 1 или 2 и обращение к памяти ПМ, в том числе и первого, не замедляя при этом работу процессоров 6 и обеспечивая таким обраагом прозрачный канал обмена данными между двумя любыми ПМ. Аналогичным образом ведется обмен ПМ с общей памятью 5, причем если блок 5 общей памяти, к которому организу- ется обращение ПМ, подключен к локальной шине 17 данного ПМ, то обмен производится по локальной шине 17, а если блок 5 подключен к локальной щи- не 17 другого ПМ, то обмен организуется по шинам 1 или 2 межпроцессорного обмена. Выбор путей о.бмена при этом зависит от текущего состояния

CHCTeisn. и определяется аппаратными ния производительности н надежности, средстваш, пользователь имеет дело g нее введены Н блоков общей памяти только с физическ11№1 адресами ячеек (И-число процессорных модулей), при- памятИ., .5 чем первый и второй входы-ныходы обУстройства 3 и 4 равномерно рас- мена каждого блока общей памяти под- пределяют доступ к шинам 1 и 2 между Клгачены к первой и второй шине меж- ПМ. При необходимости обмена между процессорного обмена соответственно, ПМ или. с блоками 5 большими блока№1 П-в устройство управления вводом-вы- данных используются устройства 9 пря- 10 водом соединено через Н-ю локальную мого доступа в памятьt Процессор 6 шину с третьими входами-выходами об- задает в регистры устройства 9 началА.- мена Н-го процессорного модуля и П-го иые адреса в блоке 7 памяти другого блока общей памяти(,Н). источника (блока 7 другого ПМ или .2. Система по п.1, отличаю- блока 5), длину блока, и дает команду 5 щ а я с я тем, что процессорный мо- иачала передачи. Устройство 9 начина- дуль содержит процессор, блок памяти, ет обмен, используя дополнительную ши- арбитр доступа к шинам и устройство ну 12 для обмеиа с блоком 7 и процес- управления прямым доступом и память, сорную шину .11 для доступа к блоку 5 причем вход-вь-.ход обмена процессора общей памяти по локальной шине 17, соединен через внутреннюю uniHy с пер- Устройство 9 может вести обмен между выми входами-выходами обмена блока любыми областями адресов памяти сис памяти и устройства управления пря- темЫ) в том числе перемещение масси- мым доступом в память, внутренним ин- вов данных в блоке 7 памяти или в формационным входом-выходом арбитра блоке 5 общей памяти. доступа к шинам и с третьим входомвыходом обмена модуля, вторые вхоцыФормула изобрете.ниявыходы обмена блока памяти и устрой- ства управления прямым доступом в па1. Многопроцессорная система обра - мять соединены через дополнительную ботки данных, содержащая процессорные 30 шину с дополнительным входом-выходом модули и два устройства управления , арбитра доступа к шинам, входы-выходы тинами межпроцессорного обмена, причем запросов доступа к шинам процессора первые и вторые входы-выходы обмена и- устройства управления прям1.1м досту- процессорных модулей соединены соот-, пом в память подключены к соответст- ветственно через первую и вторую вуюпщм входам-выходам арбитра доступа межпроцессорного обмена с входами-вы к шинам, входы-выходы запросов досту- ходами первого и второго устройств па к первой и второй шинам межпроцес- управления шинами межпроцессорного сорного обмена и nepBbrii и второй ин- обмена соответственно устройства уп- формационные входы-выходы арбитра равления вводом-выводом, о т л и ч а- 40. доступа к шинам образуют первьп и ю щ а я с я тем, что с целью расши- второй входы-выходы обмена модуля со- рения класса решаемых задач, повьш1е- отьетствеино.

Авторы

Даты

1990-12-30—Публикация

1986-10-31—Подача