Фие.1

Изобретение относится к вычислительной технике и может быть использовано в системах программного управления различного назначения,

Цель изобретения - повышение производительности за счет обеспечения возможности захвата общей шины каждым из процессоров только на время одного машинного такта,

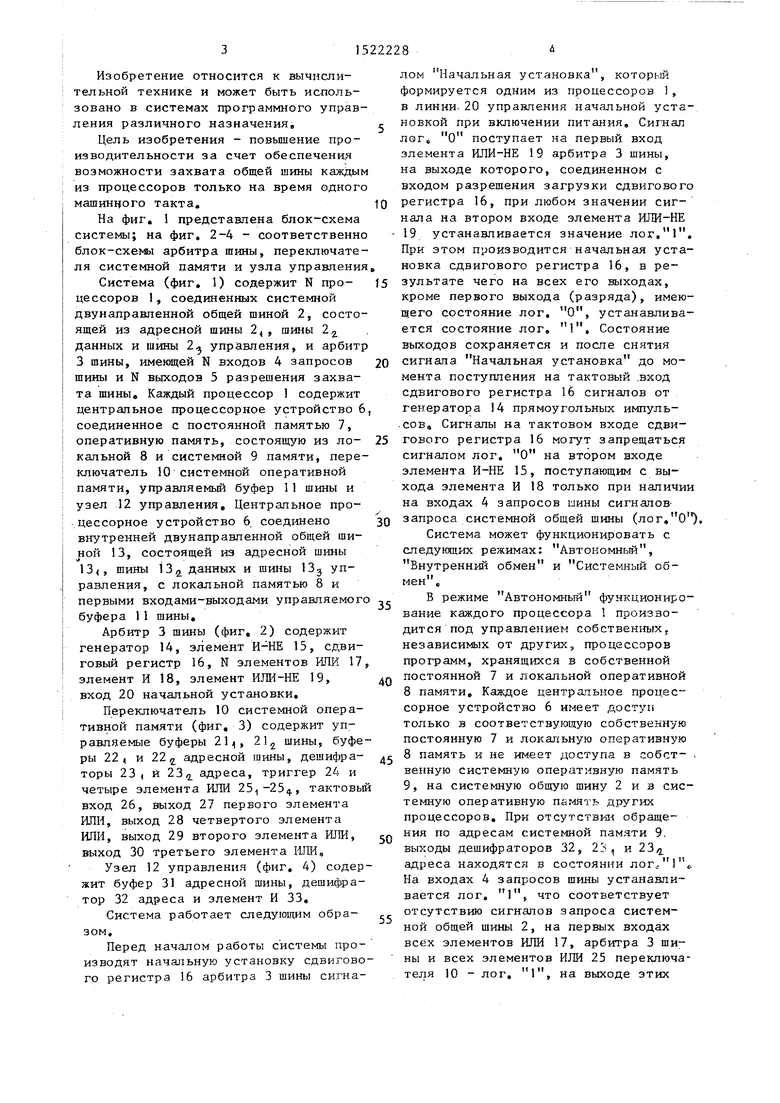

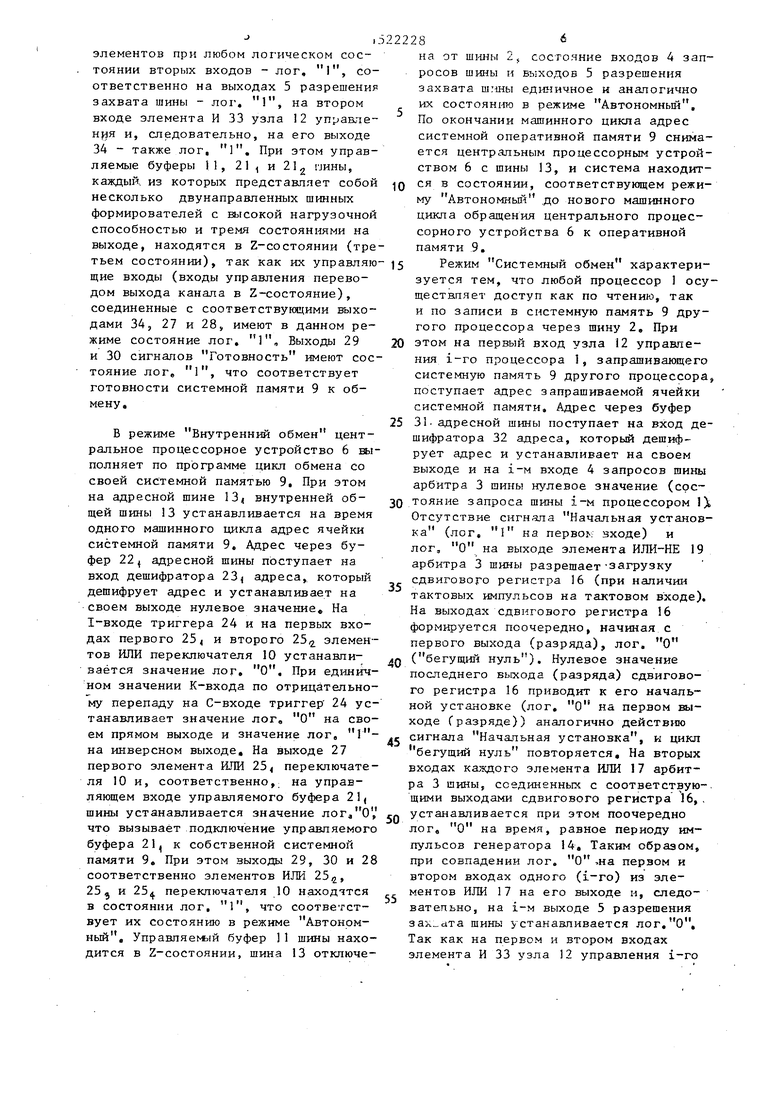

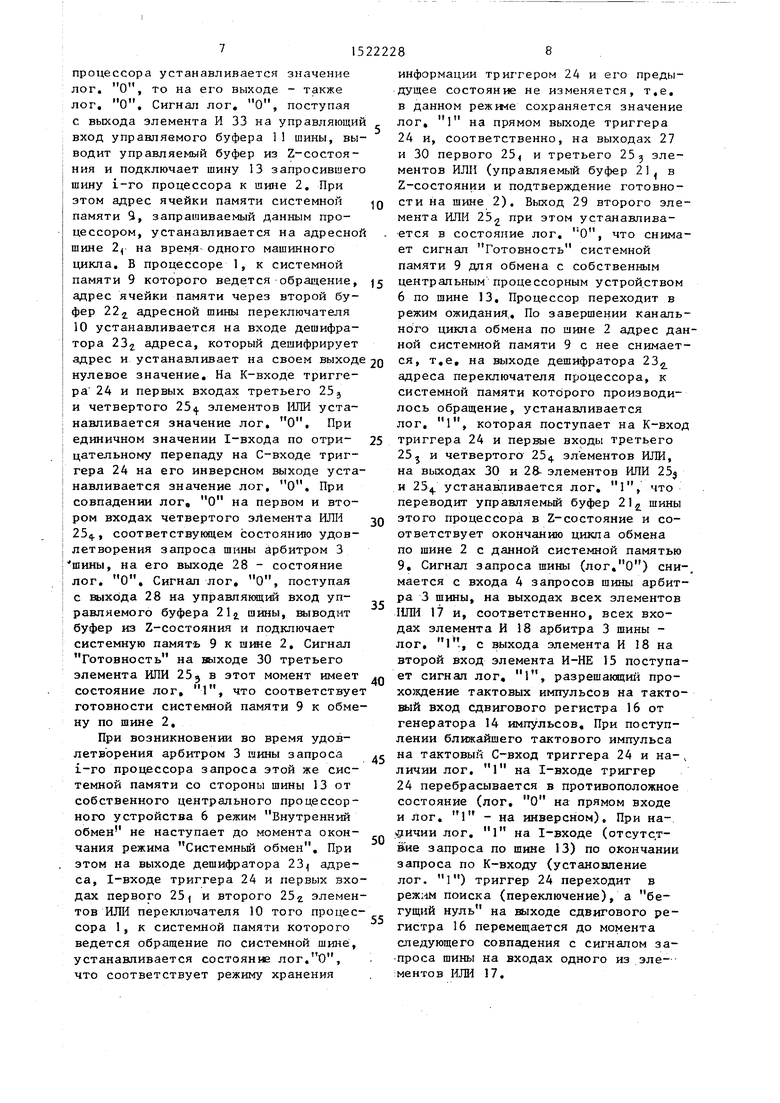

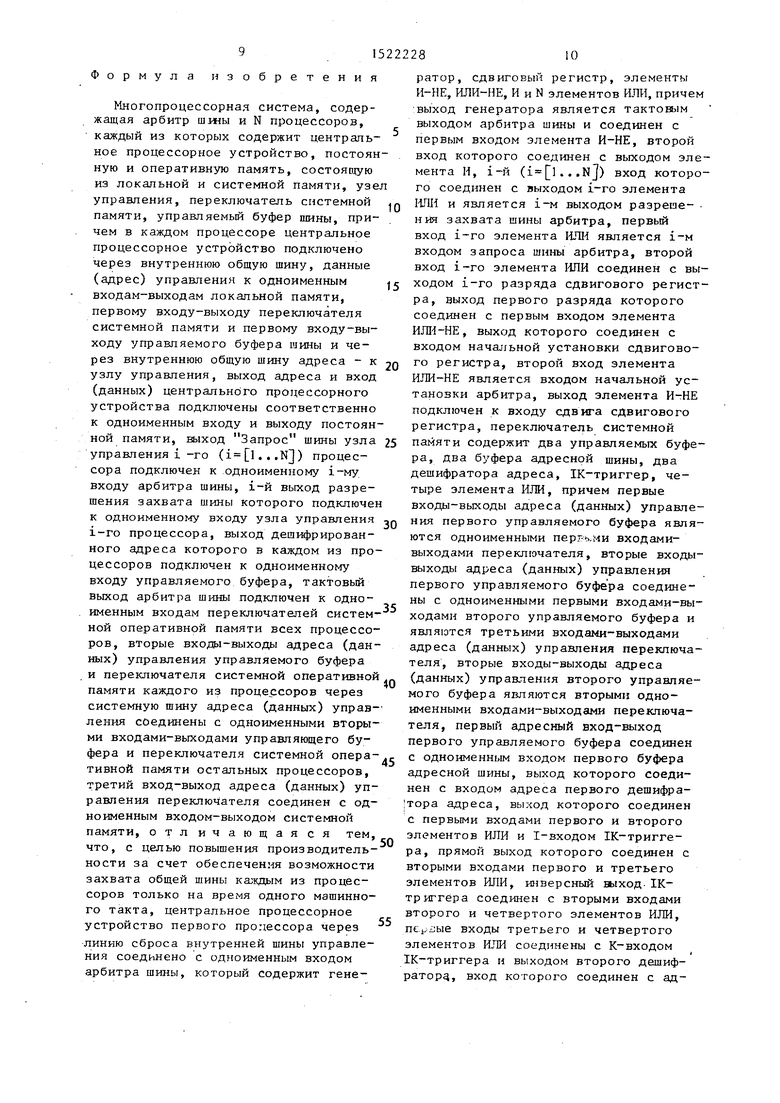

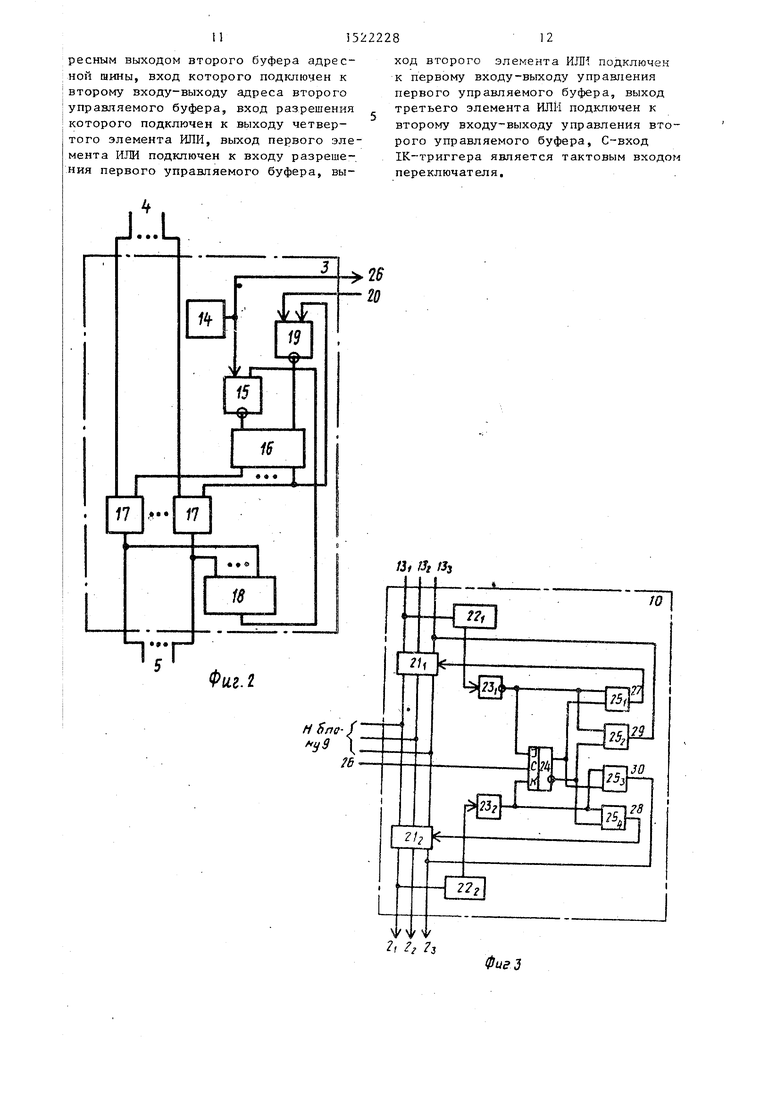

На фиг. 1 представлена блок-схема системы; на фиг, 2-4 - соответственно блок-схемы арбитра шины, переключателя системной памяти и узла управления

Система (фиг, 1) содержит N про- цессоров , соединенных системной двунаправленной общей шиной 2, состоящей из адресной шины 2,, шины 2 данных и шины 2 управления, и арбитр 3 шины, имеющей N входов 4 запросов шины и N выходов 5 разрешения захвата шины. Каждый процессор содержит центральное процессорное устройство 6 соединенное с постоянной памятью 7, оперативную память, состоящую из ло- кальной 8 и системной 9 памяти, переключатель 10 системной оперативной памяти, управляемый буфер 11 шины и узел 12 управления. Центральное процессорное устройство 6 соединено внутренней двунаправленной общей шиной 13, состоящей из адресной шины 13, шины i3,j данных и шиIiы 13з управления, с локальной памятью 8 и первыми входами-выходами управляемого буфера 11 шины.

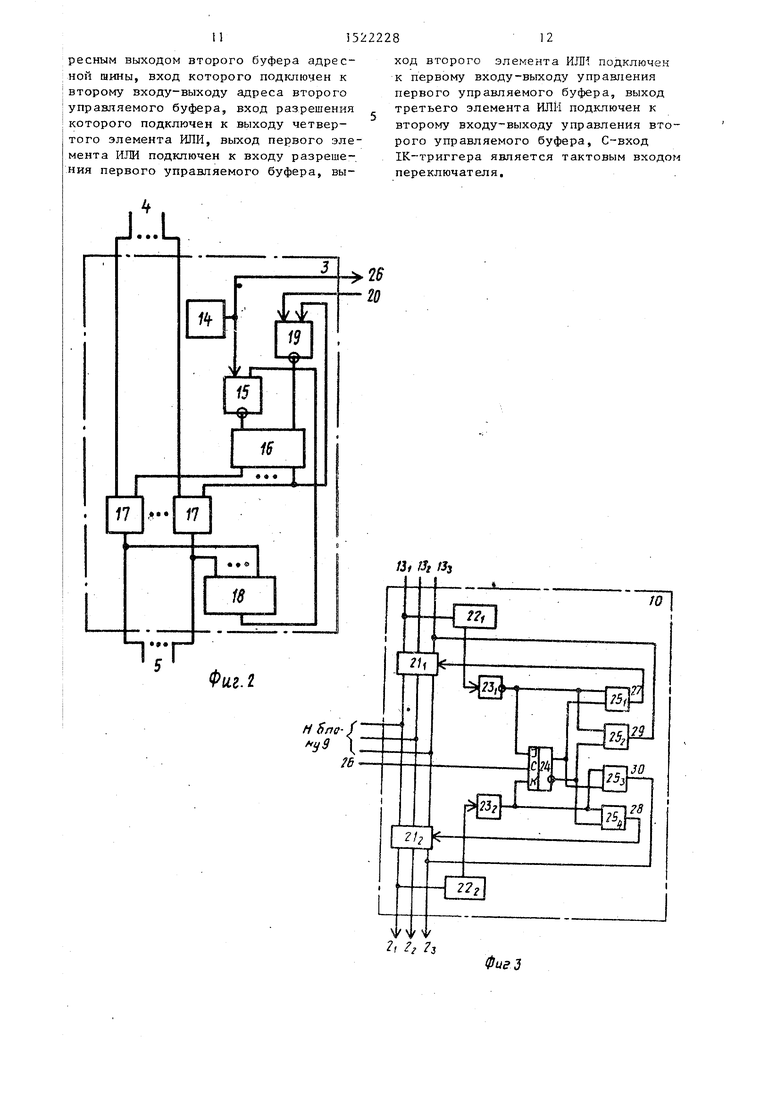

Арбитр 3 шины (фиг, 2) содержит генератор 14, элемент И-НЕ 15, сдвиговый регистр 16, N элементов ИЛИ 17, элемент И 18, элемент ИЛИ-НЕ 19,

вход 20 начальной установки.

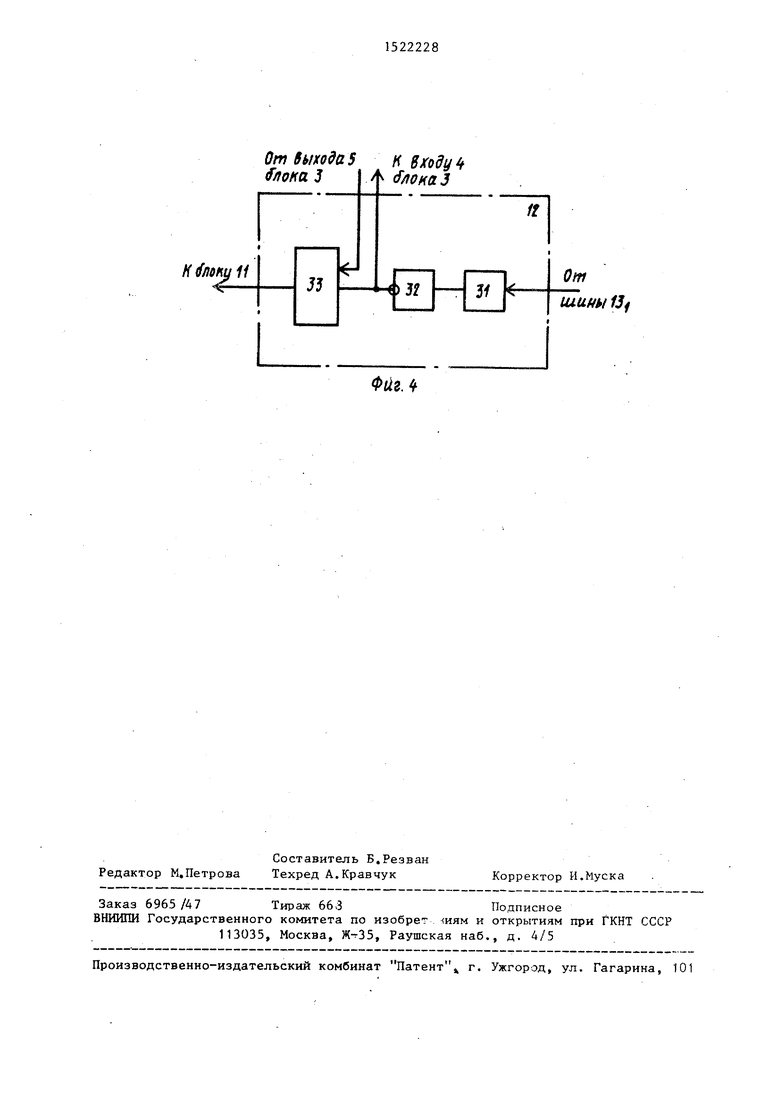

Переключатель 10 системной оперативной памяти (фиг, 3) содержит управляемые буферы 21, 21 шины, буферы 22 4 и 22, адресной шины, дешифра- торы 23, и 23 адреса, триггер 24 и четыре элемента ИЛИ 25,-25(. тактовый вход 26, выход 27 первого элемента ИЛИ, выход 28 четвертого элемента ИЛИ, выход 29 второго элемента ИЛИ, выход 30 третьего элемента 11Ш,

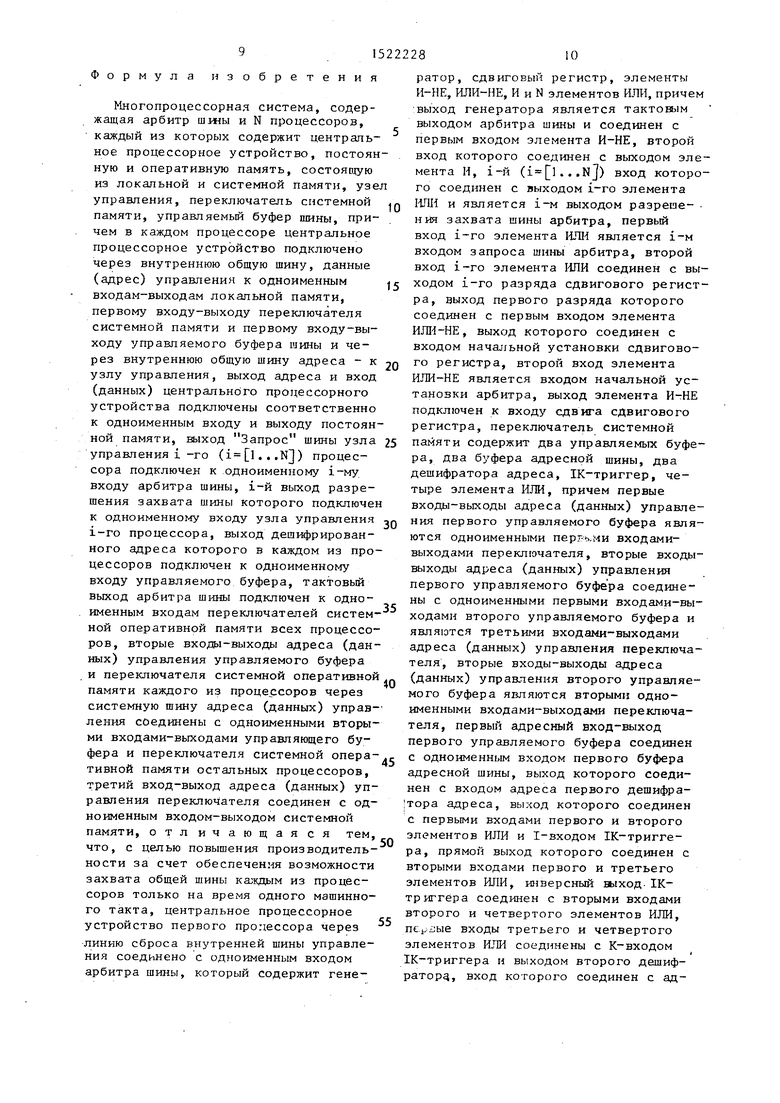

Узел 12 управления (фиг, 4) содержит буфер 31 адресной шины, дешифратор 32 адреса и элемент И 33,

Система работает следующим обра- зом.

Перед началом работы системы производят начальную установку сдвигового регистра 16 арбитра 3 шины сигналом Начальная установка, который формируется одним из процессоров I, в линии. 20 управления начальной установкой при включении питания, Сигаал лог. О поступает на первый вход элемента ИЛИ-НЕ 19 арбитра 3 шины, на выходе которого, соединенном с входом разрешения загрузки сдвигового регистра 16, при любом значении сигнала на втором входе элемента ИЛИ-НЕ 19 устанавливается значение лог,1, При этом производится начальная установка сдвигового регистра 16, в результате чего на всех его выходах, кроме первого выхода (разряда), имеющего состояние лог, О, устанавливается состояние лог, 1, Состояние выходов сохраняется и после снятия сигнала Начальная установка до момента поступления на тактовый .вход сдвигового регистра 16 сигналов от генератора 14 прямоугольных импуль- сов Сигналы на тактовом входе сдвигового регистра 16 могут запрещаться сигналом лог, О на втором входе элемента И-НЕ 15, поступающим с выхода элемента И 18 только при наличии на входах 4 запросов шины сигналов- запроса системной общей шины (лог,О

Система может функционировать с следукхцих режимах: Автономньй, Внутренний обмен и Системный обмен ,

В режиме Автономный функционирование каждого процессора 1 производится под управлением собственных, независимых от других, процессоров программ, хранящихся в собственной постоянной 7 и локальной оперативной 8 памяти. Каждое центральное процессорное устройство 6 имеет доступ только в соответствующую собственную постоянную 7 и локальную оперативную 8 память и не имеет доступа в собст- венную системную оперативную память 9, на системную общую шину 2 и в системную оперативную память других процессоров. При отсутствие обращения по адресам системной памяти 9. выходы дешифраторов 32, 23, и 23/2. адреса находятся в состоянии логе На входах 4 запросов шины устанавливается лог, 1, что соответствует отсутствию сигналов запроса системной общей шины 2, на первых входах всех элементов ИЛИ 17, арбитра 3 шины и всех элементов ИЛИ 25 переключателя 10 - лог, 1, на выходе этих

-1

элементов при любом логическом состоянии вторых входов - лог, 1, соответственно на выходах 5 разрешения захвата шины - лог, 1, на втором входе элемента И 33 узла 12 управле- нця и, следовательно, на его выходе 34 - также лог, 1, При этом управляемые буферы 11, 21 и 212 , каждый., из которых представляет собой несколько двунаправленных шинных формирователей с высокой нагрузочной способностью и тремя состояниями на выходе, находятся в Z-состоянии (третьем состоянии), так как их управляющие входы (входы управления переводом выхода канала в Z-состояние), соединенные с соответствующими выходами 34, 27 и 28, имеют в данном режиме состояние лог, 1, Выходы 29 и 30 сигналов Готовность имеют состояние лог 1, что соответствует готовности системной памяти 9 к обмену,

В режиме Внутренний обмен центральное процессорное устройство 6 выполняет по программе цикл обмена со своей системной памятью 9, При этом на адресной шине 13, внутренней общей шины 3 устанавливается на время одного машинного цикла адрес ячейки системной памяти 9, Адрес через буфер 224 адресной шины поступает на вход дешифратора 23 адреса, который дешифрует адрес и устанавливает на своем выходе нулевое значение На 1-входе триггера 24 и на первых входах первого 25 и второго 25 элементов ИЛИ переключателя 10 устанавливается значение лог, О, При единичном значении К-входа по отрицательному перепаду на С-входе триггер 24 устанавливает значение лог О на своем прямом выходе и значение лог, на инверсном выходе. На выходе 27 первого элемента ИЛИ 25 переключателя 10 и, соответственно, на управляющем входе управляемого буфера 21, шины устанавливается значение лог,0, что вызывает подключение управляемого буфера 21 к собственной системной памяти 9, При этом выходы 29, 30 и 28 соответственно элементов ИЛИ 252, 25 и 25 переключателя 10 находится в состоянии лог, 1, что соответствует их состоянию в режиме Автономный, Управляем й буфер 1 1 шины находится в Z-состоянии, шина 13 отключе2228

на от Ш1-ШЫ 2, состояние входов 4 запросов шины и вь:ходов 5 разрешения захвата ш.чны едш ичное и аналогично их состоянию в режиме Автономный, По окончании машинного цикла адрес системной оперативной памяти 9 снимается центральным процессорным устройством 6 с шины 13, и система находит- 0 ся в состоянии, соответствующем режиму Автономньш до нового машинного цикла обращения центрального процессорного устройства 6 к оперативной памяти 9,

)5Режим Системный обмен характеризуется тем, что любой процессор 1 осу- щестнпяет доступ как по чтению, так и по записи в системную память 9 другого процессора через шину 2, При 20 этом на первый вход узла 12 управления i-ro процессора 1, запрашивающего системную память 9 другого процессора, поступает адрес запрашиваемой ячейки системной памяти. Адрес через буфер 5 31. адресной шины поступает на вход дешифратора 32 адреса, который дешифрует адрес и устанавливает на своем выходе и на i-м входе 4 запросов шины арбитра 3 шины нулевое значение (срс 0 тояние запроса шины i-м процессором 1 Отсутствие сигнала Начальная установка (лог, I на первое входе) и лог, О на выходе элемента ИЛИ-НЕ 19 арбитра 3 шины разрешаетзагрузку сдвигового регистра 16 (при наличии тактовых импульсов на тактовом входе), На выходах сдвигового регистра 16 формируется поочередно, начиная с первого выхода (разряда), лог, О iQ (бегущий нуль). Нулевое значение последнего выхода (разряда) сдвигового регистра 16 приводит к его начальной установке (лог, О на первом ходе (разряде)) аналогично действию е сигнала Начальная установка, и цикл бегущий нуль повторяется. На вторых входах каждого элемента ИЛИ 17 арбитра 3 шины, соединенных с соответствую-, щими выходами сдвигового регистра 16, , п устанавливается при этом поочередно лог О на время, равное периоду импульсов генератора 14, Таким образом, при совпадении лог, О ,на первом и втором входах одного (i-ro) из элементов ИЛИ 17 на его выходе и, следовательно, на i-M выходе 5 разрешения зах„ата шины устанавливается лог,О, Так как на первом и втором входах элемента И 33 узла 12 управления i-ro

5

процессора устанавливается значение лог. О, то на его выходе - также лог, О. Сигнал лог, О, поступая с выхода элемента И 33 на управляющий вход управляемого буфера 11 шины, выводит управляемый буфер из Z-состоя- ния и подключает шину 13 запросившего шину i-ro процессора к шине 2, При этом адрес ячейки памяти системной памяти 9, запрашиваемый данным процессором, устанавливается на адресной шине 2 на время- одного машинного цикла, В процессоре 1, к системной памяти 9 которого ведется обрап;ение, адрес ячейки памяти через второй буфер 222 адресной шины переключателя 10 устанавливается на входе дешифратора 23 адреса, который дешифрирует

22288

информации триггером 24 и его предыдущее состояние не изменяется, т,е, в данном режиме сохраняется значение лог, 1 на прямом выходе триггера 24 и, соответственно, на выходах 27 и 30 первого 25 и третьего 25 элементов ИЛИ (управляемьй буфер 21 в Z-состоянии и подтверждение готовно- 0 сти на шине 2). Выход 29 второго элемента ИЛИ 25

при этом устанавпива- . ется в состояние лог, О, что снимает сигнал Готовность системной памяти 9 для обмена с собственным J5 центральным процессорным устройством 6 по шине 13, Процессор переходит в режим ожидания,. По завершении канального цикла обмена по шине 2 адрес данной системной памяти 9 с нее снимает

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная система | 1989 |

|

SU1647597A1 |

| МНОГОМАШИННАЯ СИСТЕМА УПРАВЛЕНИЯ | 2006 |

|

RU2320003C2 |

| Устройство для обмена данными между процессором и периферийными устройствами | 1987 |

|

SU1501078A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Устройство для обмена данными между процессорами | 1988 |

|

SU1566361A1 |

| Устройство доступа к видеопамяти | 1988 |

|

SU1523058A3 |

| Многопроцессорная система | 1990 |

|

SU1709330A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Устройство для управления памятью | 1983 |

|

SU1151975A1 |

| Устройство для регенерации динамической памяти | 1980 |

|

SU943845A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах программного управления различного назначения. Целью изобретения является повышение производительности системы за счет обеспечения возможности захвата общей шины каждым из процессоров только на время одного машинного такта. Поставленная цель достигается тем, что в системе, содержащей арбитр шины 3 и N процессоров 1, каждый из которых состоит из центрального процессорного устройства 6, ПЗУ 7, локальной памяти 8, системной памяти 9, переключателя системной памяти 10, управляемого буфера шины 11, узла управления 12, арбитр шины содержит генератор, сдвиговый регистр, элементы И-НЕ, ИЛИ-НЕ и N элементов ИЛИ, а переключатель системной памяти содержит два управляемых буфера, два буфера адресной шины, два дешифратора, JK - триггер, четыре элемента ИЛИ. 4 ил.

адрес и устанавливает на своем выходе 2о ся, т.е. на выходе дешифратора 23

нулевое значение. На К-входе триггера 24 и первых входах третьего 25j и четвертого 25 элементов ИЛИ устанавливается значение лог, О, При единичном значении 1-входа по отрицательному перепаду на С-входе триггера 24 на его инверсном выходе устанавливается значение лог, О, При совпадении лог, О на первом и втором входах четвертого элемента ИЛИ 25,)., соответствукядем состоянию удовлетворения запроса шины арбитром 3 | шины, на его выходе 28 - состояние I лог, О, Сигнал лог, О, поступая I с выхода 28 на управпякяций вход уп- равляемого буфера 21j шины, выводит буфер из Z-состояния и подключает системную память 9 к Ш1дае 2, Сигнал Готовность на выходе 30 третьего элемента ИЛИ 25j в этот момент имеет состояние лог, 1, что соответствует готовности системной памяти 9 к обмену по шине 2,

При возникновении во время удовлетворения арбитром 3 шины запроса i-ro процессора запроса этой же системной памяти со стороны шины 13 от собственного центрального процессорного устройства 6 режим Внутренний обмен не наступает до момента окончания режима Системньй обмен. При этом на выходе дешифратора 23 адреса, 1-входе триггера 24 и первых входах первого 25( и второго 25 элементов ИЛИ переключателя 10 того процессора 1, к системной памяти которого ведется обращение по системной шине, устанавливается состояние лог.О, что соответствует режиму хранения

25

адреса переключателя процессора, к системной памяти котЬрого производи лось обращение, устанавливается лог, 1, которая поступает на К-вх триггера 24 и первые входы третьего 25J и четвертого 254 элементов ИЛИ,

на выходах и 25

30

25

30

35

40

45

50

55

и 28- элементов ИЛИ л. устанавливается лог, 1, что переводит управляемый буфер 2151 шин этого процессора в Z-состояние и со ответствует окончанию цикпа обмена по шине 2 с данной системной память 9, Сигнал запроса шины (лог,О) сн мается с входа 4 запросов шины арби ра 3 шины, на выходах всех элементо 1ШИ 17 и, соответственно, всех входах элемента И 18 арбитра 3 шины - лог, Г., с выхода элемента И 18 на второй вход элемента И-НЕ 15 поступ ет сигнал лог, 1, разрешакяци11 про хо5кдение тактовых импульсов на такт №1Й вход сдвигового регистра 16 от генератора 14 импульсов. При поступ лении ближайшего тактового импульса на тактовый С-вход триггера 24 и на личии лог. 1 на 1-входе триггер 24 перебрасывается в противоположно состояние (лог, О на прямом входе и лог, 1 - на инверсном). При на- ричии лог, 1 на 1-входе (отсутст- йие запроса по шине 13) по окончани запроса по К-входу (установление лог. 1) триггер 24 переходит в реж;-1М поиска (переключение), а бегущий нуль на выходе сдвигового ре гистра 16 перемещается до момента следующего совпадения с сигналом за- проса шины на входах одного из эле- ;ментов ИЛИ 17,

5

адреса переключателя процессора, к системной памяти котЬрого производилось обращение, устанавливается лог, 1, которая поступает на К-вход триггера 24 и первые входы третьего 25J и четвертого 254 элементов ИЛИ,

на выходах и 25

30

25

S

0

5

0

5

0

5

и 28- элементов ИЛИ л. устанавливается лог, 1, что переводит управляемый буфер 2151 шины этого процессора в Z-состояние и соответствует окончанию цикпа обмена по шине 2 с данной системной памятью 9, Сигнал запроса шины (лог,О) сни-, мается с входа 4 запросов шины арбитра 3 шины, на выходах всех элементов 1ШИ 17 и, соответственно, всех входах элемента И 18 арбитра 3 шины - лог, Г., с выхода элемента И 18 на второй вход элемента И-НЕ 15 поступает сигнал лог, 1, разрешакяци11 про- хо5кдение тактовых импульсов на такто- №1Й вход сдвигового регистра 16 от генератора 14 импульсов. При поступлении ближайшего тактового импульса на тактовый С-вход триггера 24 и на- личии лог. 1 на 1-входе триггер 24 перебрасывается в противоположное состояние (лог, О на прямом входе и лог, 1 - на инверсном). При на- ричии лог, 1 на 1-входе (отсутст- йие запроса по шине 13) по окончании запроса по К-входу (установление лог. 1) триггер 24 переходит в реж;-1М поиска (переключение), а бегущий нуль на выходе сдвигового регистра 16 перемещается до момента следующего совпадения с сигналом за- проса шины на входах одного из эле- ;ментов ИЛИ 17,

Формула изобретения

Многопроцессорная система, содержащая арбитр шины и N процессоров,

каждый из которых содержит центральное процессорное устройство, постоянную и оперативную память, состоянию из локальной и системной памяти, узе управления, переключатель системной памяти, управляемый буфер шины, причем в каждом процессоре центральное процессорное устройство подключено через внутреннюю общую щину, данные (адрес) управления к одноименным

входам-выходам локальной памяти, первому входу-выходу переключателя системной памяти и первому входу-выходу управляемого буфера шины и через внутреннюю общую шину адреса - к узлу управления, выход адреса и вход (данных) центральнЬго процессорного устройства подключены соответственно к одноименным входу и выходу постоянной памяти, выход Запрос шины узла управления i -го (...Nj) процессора подключен к одноименному i-му входу арбитра шины, i-й вьгход разрешения захвата шины которого подключен к одноименному входу узла управления i-ro процессора, выход дешифрированного адреса которого в каждом из процессоров подключен к одноименному входу управляемого буфера, тактовьй выход арбитра шины подключен к одноименным входам переключателей системной оперативной памяти всех процессоров, вторые вход 1-выходы адреса (данных) управления управляемого буфера и переключателя системной оперативной памяти каждого из процессоров через системную шину адреса (данных) управления соединены с одноименными вторыми входами-выходами управляющего буфера и переключателя системной оперативной памяти остальных процессоров, третий вход-выход адреса (данных) управления переключателя соединен с одноименным входом-выходом системной памяти, отл ичающая ся тем, что, с целью повышения производительности за счет обеспечения возможности захвата общей шины каждым из процессоров только на время одного машинного такта, центральное процессорное устройство первого процессора через

линию сброса внутренней шины управления соединено с одноименным входом арбитра шины, который содержит гене

Q

о 5 n

0

ратор, сдвиговый регистр, элементы И-НЕ, ИЛИ-НЕ, И и N элементов ИЛИ, причем выход генератора является тактовым выходом арбитра шины и соединен с первым входом элемента И-НЕ, второй вход которого соединен с выходом элемента И, i-й (.,,Nj) вход которого соединен с выходом i-ro элемента ИЛИ и является i-м выходом разреше- нИя захвата шины арбитра, первый вход i-ro элемента ИЛИ является i-м входом запроса шины арбитра, второй вход i -го элемента 1-ШИ соединен с выходом i-ro разряда сдвигового регистра, выход первого разряда которого соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с входом начальной установки сдвигового регистра, второй вход элемента ИЛИ-НЕ является входом начальной установки арбитра, выход элемента И-НЕ подключен к входу сдвига сдвигового регистра, переключатель системной памяти содержит два управляемых буфера, два буфера адресной шины, два дешифратора адреса, 1К-триггер, четыре элемента ИЛИ, причем первые входы-выходы адреса (данных) управления первого управляемого буфера являются одноименными перг-ь.ми входами- выходами переключателя, вторые входы- выходы адреса (данных) управления первого управляемого буфера соединены с одноименными первыми входами-выходами второго управляемого буфера и являются третьими входами-выходами адреса (данных) управления переключателя, вторые входы-выходы адреса (данных) управления второго управляемого буфера являются вторыми одноименными входами-выходами перекпюча- теля, первый адресный вход-выход первого управляемого буфера соединен с одноименным входом первого буфера адресной шины, выход которого соединен с входом адреса первого дешифра- тора адреса, выход которого соединен с первыми входами первого и второго элементов ИЛИ и 1-входом 1К-тригге- ра, прямой выход которого соединен с вторыми входами первого и третьего элементов ИЛИ, инверсный выход-IK- триггера соединен с вторыми входами второго и четвертого элементов ИЛИ, пс.йые входы третьего и четвертого элементов ИЛИ соединены с К-входом 1К-триггера и выходом второго дешифратору, вход которого соединен с адресным выходом второго буфера адрес ной шины, вход которого подключен к второму входу-выходу адреса второго управляемого буфера, вход разрешения которого подключен к выходу четвертого элемента ИЛИ, выход первого элемента ИЛИ подключен к входу разрешения первого управляемого буфера, выФиг-2

Н Sno

ход второго элемента ИЛ подключен к первому входу-выходу управления первого управляемого буфера, выход третьего элемента ИЛИ подключен к второму входу-выходу управления второго управляемого буфера, С-вход 1К-триггера является тактовым входом переключателя.

13i f33

{

ь

От Вшо9а5 К gjfody

(f/roffuJ

4 /1окаЗ

К локи 11

J5

К gjfody

4 /1окаЗ

ojf

5f

От

luuffn 13i

Фиг. 4

| Коммутатор без переговорно-вызывных ключей с применением автоматических искателей | 1924 |

|

SU1810A1 |

| М., ИНЭУМ,,1986, Европейская заявка ЕР № 156921, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1989-11-15—Публикация

1988-03-14—Подача