Изобретение (отш.и.-ится к области автоматики и вычислительной техники и может быть использовано в устройствах числового программного управле- ния станками и в графических устройствах ввода - вывода вычислительных машин.

Цель изобретения - реализация интерполяции в трехмерном пространстве.

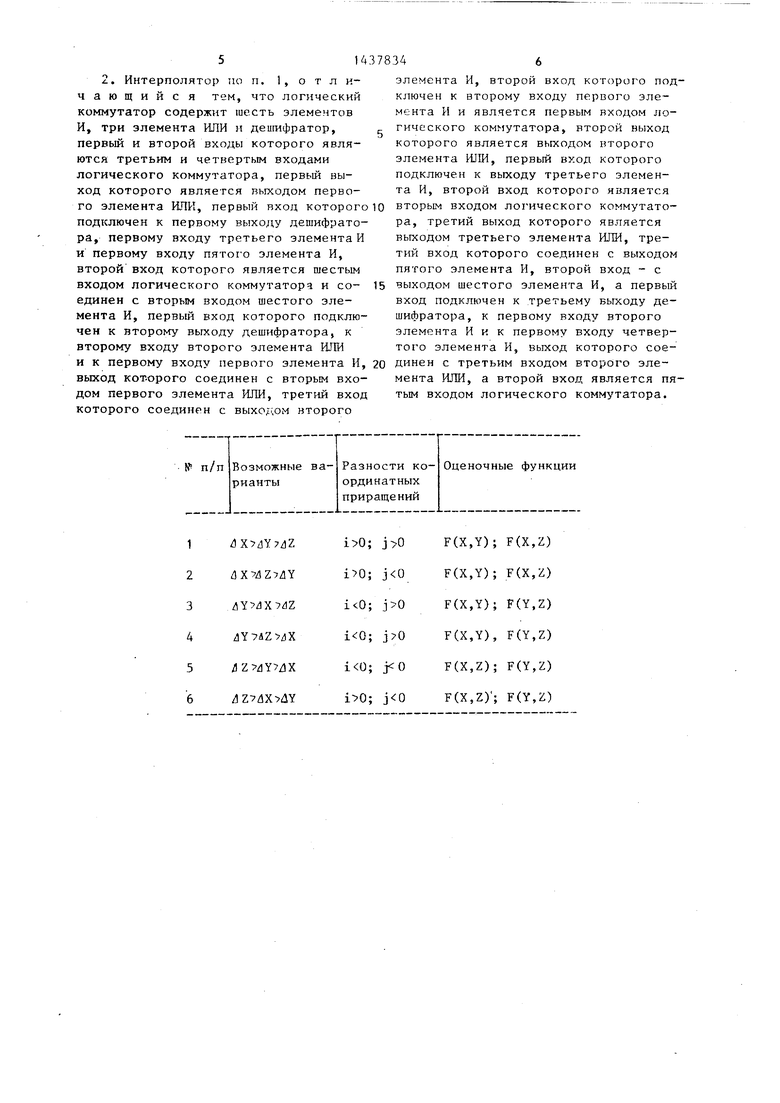

На фиг.1 приведена структурная схема линейного трехкоординатного интерполятора; на фиг. 2 - структурная схема логического коммутатора; на фиг. 3 - пример аппроксимируемой прямой в трехмерном дискретном пространстве.

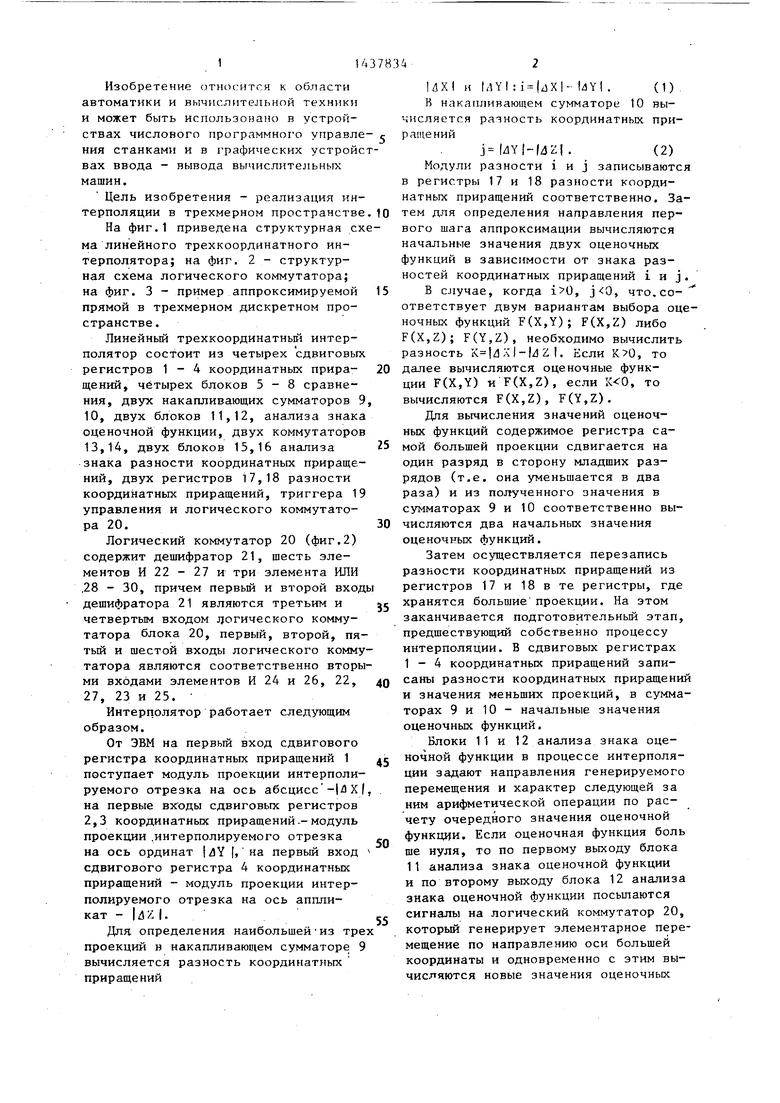

Линейный трехкоординатньй интерполятор состоит из четырех сдвиговых регистров 1 - 4 координатных прира- щений, четырех блоков 5-8 сравнения, двух накапливающих сумматоров 9, 10, двух блоков 11,12, анализа знака оценочной функции, двух коммутаторов 13,14, двух блоков 15,16 анализа знака разности координатных приращений, двух регистров 17,18 разности координатных приращений, триггера 19 управления и логического коммутатора 20.

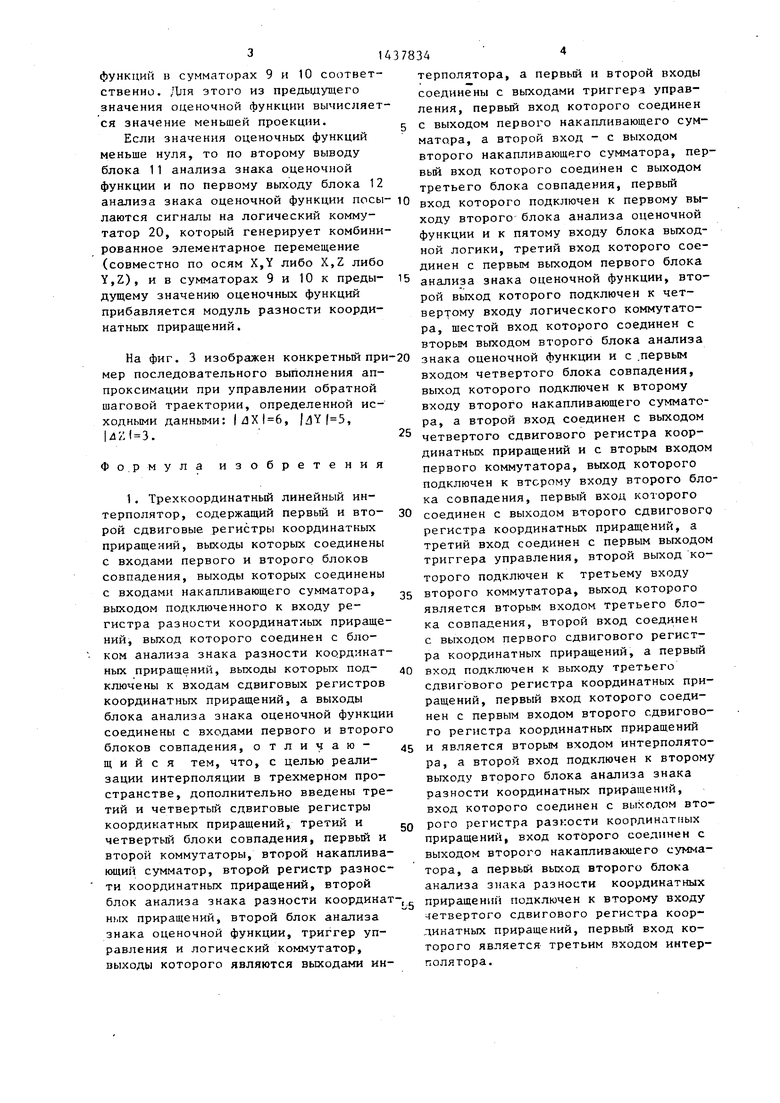

Логический коммутатор 20 (фиг.2) содержит дешифратор 21, шесть элементов И 22 - 27 и три элемента ИЛИ .28 - 30, причем первый и второй входы дешифратора 21 являются третьим и четвертым входом Л7огического коммутатора блока 20, первый, второй, пятый и шестой входы логического коммутатора являются соответственно вторыми входами элементов И 24 и 26, 22, 27, 23 и 25.

Интерполятор работает следующим образом.

От ЭВМ на первый вход сдвигового регистра координатных приращений 1 поступает модуль проекции интерполируемого отрезка на ось абсцисс -|ЛХ|, на первые вх оды сдвиговых регистров 2,3 координатных приращений.-модуль проекции .интерполируемого отрезка на ось ординат йЧ (, на первый вход сдвигового регистра 4 координатных приращений - модуль проекции интерполируемого отрезка на ось аппликат - 14 Z I.

Для определения наибольшейиз трех проекций в накапливающем сумматоре 9 вычисляется разность координатных приращений

с

5

0 5 0

5 0

j

5

UXI и :i jdX|- IdYl .(1) .

В накапливающем сумматоре 10 вычисляется разность координатных при- р аще НИИ

j UYl-MZ|. (2)

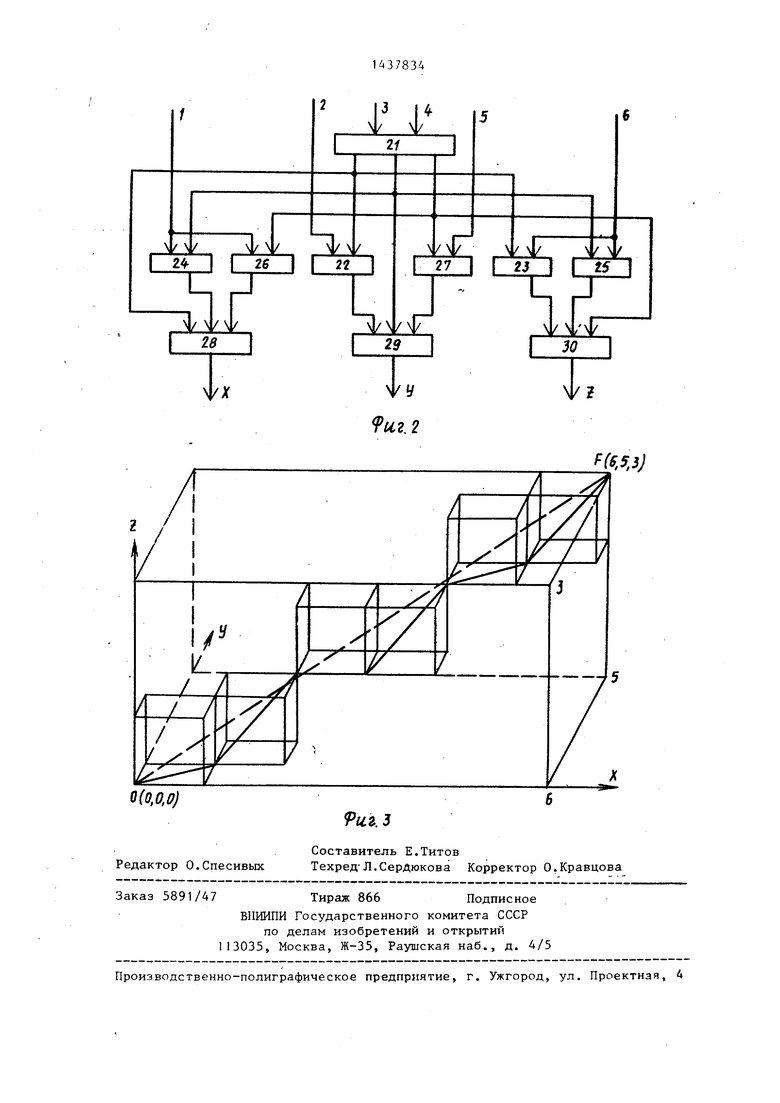

Модули разности i и j записываются в регистры 17 и 18 разности координатных приращений соответственно. Затем для определения направления первого шага аппроксимации вычисляются начальные значения двух оценочных функций в зависимости от знака разностей координатных приращений i и j.

В случае, когда , , что.со- ответствует двум вариантам выбора оценочных функций F(X,Y); F(X,Z) либо F(X,Z); F(Y,Z), необходимо вычислить разность л|-|Л Z I. Если , то далее вычисляются оценочные функции F(X,Y) и F(X,Z), если , то вычисляются F(X,Z), F(Y,Z).

Для вычисления значений оценочных функций содержимое регистра самой большей проекции сдвигается на один разряд в сторону младших разрядов (т.е. она уменьшается в два раза) и из полученного значения в сумматорах 9 и 10 соответственно вычисляются два начальных значения оценочных функций.

Затем осуществляется перезапись разности координатных приращений из регистров 17 и 18 в те регистры, где хранятся большие проекции. На этом заканчивается подготовительный этап, предшествующий собственно процессу интерполяции. В сдвиговых регистрах

I- 4 координатных приращений записаны разности координатных приращений и значения меньших проекций, в сумматорах 9 и 10 - начальные значения оценочных функций.

Блоки 11 и 12 анализа знака оценочной функции в процессе интерполяции задают направления генерируемого перемещения и характер следующей за ним арифметической операции по расчету очередного значения оценочной функции. Если оценочная функция боль ше нуля, то по первому выходу блока

I1анализа знака оценочной функции

и по второму выходу блока 12 анализа знака оценочной функции посылаются сигналы на логический коммутатор 20, который генерирует элементарное перемещение по направлению оси большей координаты и одновременно с этим вычисляются новые значения оценочных

функций н сумматорах 9 и 10 соответственно. /VIH этого из предыдущего значения оценочной функции вычисляется значение меньшей проекции.

Если значения оценочных функций меньше нуля, то по второму выводу блока 11 анализа знака оценочной функции и по первому выходу блока 12 анализа знака оценочной функции посы лаются сигналы на логический коммутатор 20, который генерирует комбинированное элементарное перемещение (совместно по осям X,Y либо X,Z либо Y,Z), и в сумматорах 9 и 10 к предыдущему значению оценочных функций прибавляется модуль разности координатных приращений.

терполятора, а первый и второй входы соединены с выходами триггера управления, первый вход которого соединен с выходом первого накапливающего сумматора, а второй вход - с выходом второго накапливающего сумматора, первый вход которого соединен с выходом третьего блока совпадения, первый вход которого подключен к первому выходу второго блока анализа оценочной функции и к пятому входу блока выходной логики, третий вход которого соединен с первым выходом первого блока анализа знака оценочной функции, второй выход которого подключен к чет- входу логического коммутатора, шестой вход которого соединен с

| название | год | авторы | номер документа |

|---|---|---|---|

| Графический интерполятор | 1985 |

|

SU1401509A1 |

| Линейный интерполятор | 1991 |

|

SU1809421A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Линейный интерполятор для систем интерактивной графики | 1988 |

|

SU1608691A1 |

| Линейный интерполятор | 1985 |

|

SU1298714A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Линейный интерполятор | 1980 |

|

SU920636A2 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

| Линейный интерполятор | 1987 |

|

SU1439534A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах числового программного управления станками и графических устройствах ввода-вывода вычислительных машин. Целью изобретения является реализация интерполяции в трехмерном пространстве, т.е. возможность производить интерполяцию заданного отрезка не только на двухмерной дискретной плоскости, но и в трехмерном дискретном пространстве. Трехкоординатный линейный интерполятор содержит четыре сдвиговых регистра координатных приращений 1,2,3,4, четыре блока сравнения 5,6,7,8, два накапливающих сумматора 9,10, два блока анализа знака оценочной функции 11,12, два коммутатора 13,14, два блока анализа знака разности координатных приращений 15, 16, два регистра разности координатных приращений 17,18, блок управления коммутаторами 19 и логический коммутатор 20. Трехкоординятный линейный интерполятор обладает достаточно высоким быстродействием благодаря одновременности интерполяций по трем координатам, высокой точностью интерполяции (менее 0,5 дискретности) и широкими функциональными возможностями, что позволит его использовать в составе УЧПУ второго класса по ГОСТу 21021-85 (типа NC) для токарных и фрезерных станков основных классов. 1 3.п. ф-лы, 3 ил. (Л 4 OJ vi 00 СО 1 4х 9Mtf

вторым выходом второго блока анализа

3 изображен конкретный при-20 знака оценочной функции и с .первым

входом четвертого блока совпадения, выход которого подключен к второму входу второго накапливающего сумматоНа фиг.

мер последовательного выполнения аппроксимации при управлении обратной шаговой траектории, определенной исходными данными: |/ЗХ| 6, MY (5, UZl 3.

25

ра, а второй вход соединен с выходом четвертого сдвигового регистра координатных приращений и с вторым входом первого коммутатора, выход которого подключен к второму входу второго блока совпадения, первый вход которого соединен с выходом второго сдвигового регистра координатных приращений, а третий вход соединен с первым выходом триггера управления, второй выход которого подключен к третьему входу второго коммутатора, выход которого является вторым входом третьего блока совпадения, второй вход соединен с выходом первого сдвигового регистра координатных приращений, а первый вход подключен к выходу третьего сдвигового регистра координатных приращений, первый вход которого соединен с первым входом второго сдвигового регистра координатных приращений и является вторым входом интерполятора, а второй вход подключен к второму выходу второго блока анализа знака разности координатных приращений, вход которого соединен с выходом второго регистра разкости кoopдинaт ыx приращений, вход которого соединен с выходом второго накапливающего сумматора, а первый выход второго блока анализа знака разности координатных

Фо.рмула изобретения

блок анализа знака разности координат-, приращений подключен к второму входу

w J

ных приращений, второй блок анализа знака оценочной функции, триггер управления и логический коммутатор, выходы которого являются вькодами ин етвертого сдвигового регистра координатных приращений, первый вход которого является третьим входом интерполятора.

5

0

5

0

5

0

ра, а второй вход соединен с выходом четвертого сдвигового регистра координатных приращений и с вторым входом первого коммутатора, выход которого подключен к второму входу второго блока совпадения, первый вход которого соединен с выходом второго сдвигового регистра координатных приращений, а третий вход соединен с первым выходом триггера управления, второй выход которого подключен к третьему входу второго коммутатора, выход которого является вторым входом третьего блока совпадения, второй вход соединен с выходом первого сдвигового регистра координатных приращений, а первый вход подключен к выходу третьего сдвигового регистра координатных приращений, первый вход которого соединен с первым входом второго сдвигового регистра координатных приращений и является вторым входом интерполятора, а второй вход подключен к второму выходу второго блока анализа знака разности координатных приращений, вход которого соединен с выходом второго регистра разкости кoopдинaт ыx приращений, вход которого соединен с выходом второго накапливающего сумматора, а первый выход второго блока анализа знака разности координатных

етвертого сдвигового регистра координатных приращений, первый вход которого является третьим входом интерполятора.

514

динен

элемента И, второй вход которого подключен к второму входу первого элемента И и является первым входом логического коммутатора, второй выход которого является выходом второго элемента ИЛИ, первый вход которого подключен к выходу третьего элемента И, второй вход которого является вторым входом логического коммутатора, третий выход которого является выходом третьего элемента ИЛИ, третий вход которого соединен с выходом пятого элемента И, второй вход - с выходом шестого элемента И, а первый вход подключен к третьему выходу дешифратора, к первому входу второго элемента Ник первому входу четвертого элемента И, выход которого соес третьим входом второго элемента ИЛИ, а второй вход является пятым входом логического коммутатора.

F(X,Y); F(X,Z) F(X,Y); F(X,Z) F(X,Y); F(Y,Z) F(X,Y), F(Y,Z) F(X,Z); F(Y,Z) F(X,Z) ; F(Y,Z)

I 1 I Ф

f L

/ A

I

X

/

I TI

L

f fwj

/

/

X

/7

X

| Патент Великобритании № 1453943, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| ТРЕХКООРДИНАТНЫЙ ЦИФРОВОЙ ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 0 |

|

SU271903A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Трехкоординатный линейный интерполятор | 1982 |

|

SU1037214A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Линейный интерполятор | 1980 |

|

SU920636A2 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-11-15—Публикация

1987-03-19—Подача