3

оо

ЭО

СП

Јь

Изобретение относится к вычислительной технике.

Цель изобретения - повышение надежности устройства.

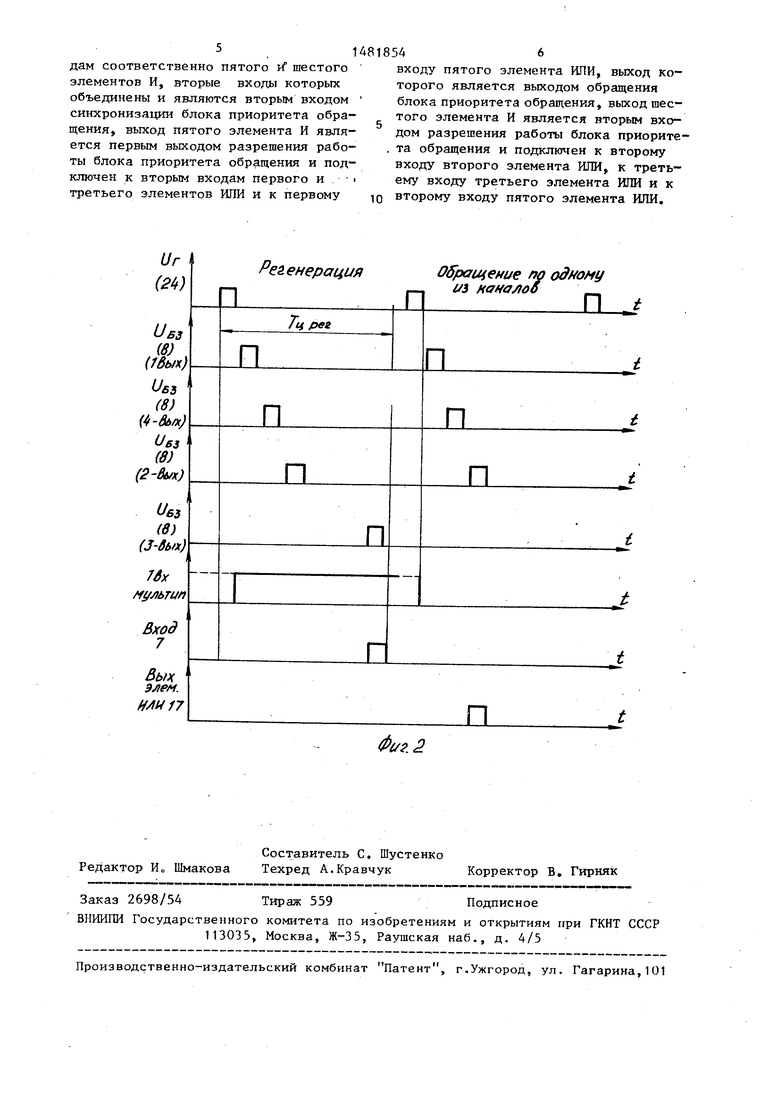

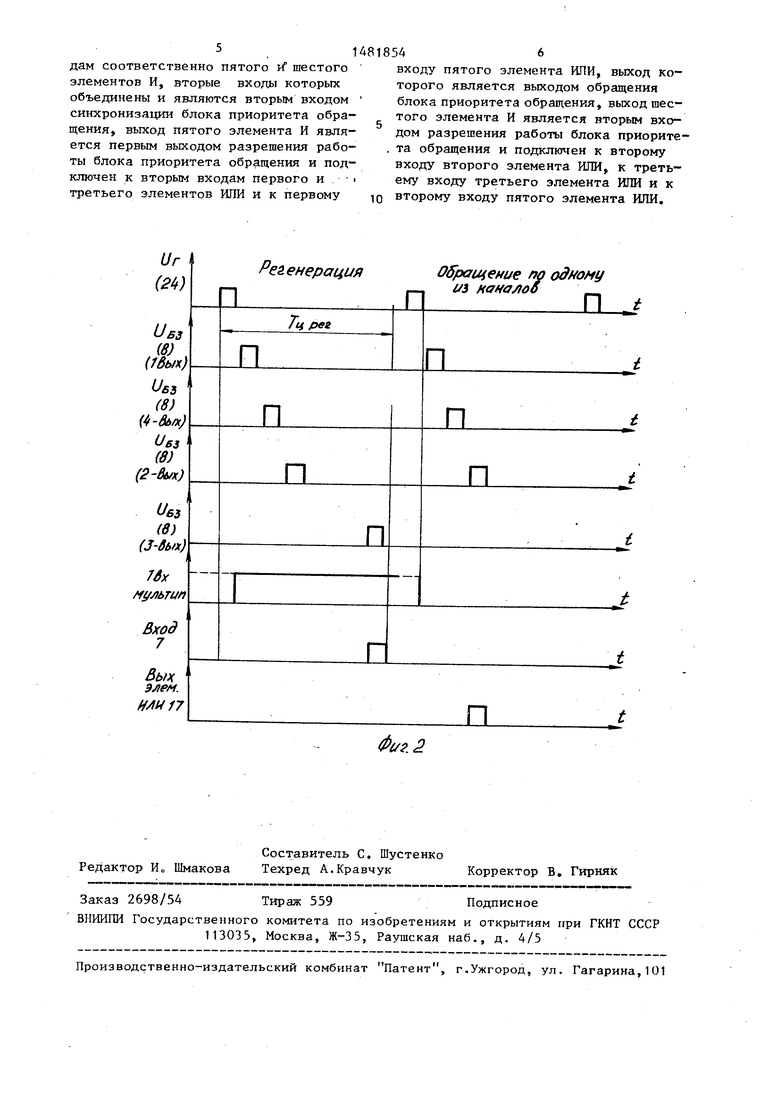

На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг.2 - временная диаграмма работы блоков устройствао

Устройство содержит блок 1 памяти мультиплексор 2, блок 3 синхронизации, счетчик 4 адресов, блок 5 приоритета обращения, триггер 6 и элементы И 7 и 8.

Блок 3 синхронизации содержит элемент И 9, блок 10 элементов задержки и генератор 11.

Блок 5 приоритета обращения содержит элементы ИЛИ 12-16, триггеры 17-20 и элементы И 21-24.

Устройство работает следующим образом.

При включении устройства с входа начальной установки поступает сигнал на входы сброса счетчика 4, триггеров 6 и 17-20. После прихода разрешающего потенциала на запуск устройства на вход элемента И 9 сигнал с генератора 11 поступает на вход блока 10 элементов задержки. С выхода блока 10 управляющий импульс поступает на вход элемента И 7. На втором входе элемента И 7 имеется высокий потенциал, поступающий с триггера 6, а на третьем входе - низкий, прихо- дящий с элемента ИЛИ 16, Следовательно, на выходе элемента И 7 отсутствует сигнал управления и с выхода триггера 6 поступает разрешение на регенерацию, т.е. приходит управля- ющий потенциал на управляющий вход мультиплексора 2, подключающий код адреса регенерации к блоку 1 памяти, разрешающий потенциал на регенерацию приходит и на вход регенерации бло- ка 1.

Затем с блока 10 элементов задержки поступает сигнал опроса на элементы И 21 и 22. Если обращения к ЗУ не было, то триггеры 19 и 20 находятся в состояний О и на выходах указанных элементов И нулевые сигналы. Далее с блока 10 поступает сигнал опроса на элементы И 24 и 23, кото- рый через них не проходит на выход элемента ИЛИ 15, а следовательно, не поступает на вход блока 1 памяти сигнал обращения. Затем с выхода

блока 10 подается сигнал на один из входов элемента И 8, за счет которого в счетчике 4 увеличивается на единицу адрес регенерации.

При записи или считывании устройство имеет два приоритета обмена информацией, к примеру, обмен инфбрма- цией с ЭВМ и внешними ЗУ ЭВМ. Старший приоритет обеспечивается установкой триггера 17 в состояние 1 по сигналу, поступившему с первого входа обращения, а младший - по сигналу с второго входа обращения устройства.

Пусть, к примеру, необходимо считать или записывать информацию по некоторому адресу старшего приоритета, т.е„ в некоторое время триггер 17 устанавливается в состояние 1. В этом случае поступает запрещающий потенциал на элемент И 22 к разрешающий потенциал через элемент ИЛИ 13 на вход элемента И 7. Поэтому очередной импульс с выхода блока 10 проходит через элемент И 7 и устанавливает триггер 6 в состояние 1. За сче этого поступает разрешающий потенциал на входы элементов И 21 и 22. Очередной импульс с выхода блока 10 проходит через элемент И 21 (элемент И 22 закрыт потенциалом от триггера 17) и устанавливает триггер 20 в состояние 1. Поэтому управляющий импульс с выхода блока 10 проходит через элемент И 23 и элемент ИЛИ 15, который и служит сигналом обращения к накопителю, а потенциал записи или считьгоания приходит на накопитель Ј входа режима устройства. Кроме того, с триггера 20 на вход мультиплексора подается потенциал, который подключает адрес, пришедший на информационные входы первой группы мультиплексора. Кроме того, имульс с выхода элемента К 23 поступает на выход разрешения работы к на входы элементов ИЛИ 14 и 12. При этом триггеры 17, 6 и 20 устанавливаются в исходное состояние. Сигнал с выхода блока 10 не проходит на счетчик 4 и в нем хранится очередной адрес регенерации.

Работа по младшему приоритету аналогична, но в ней участвуют триггеры 19 и 22. По окончании считывания или записи информации в блок 1 памяти по тому или другому приоритету триггер 6 сбрасывается в состояние О, подключая цепь регенерации к блоку 1 памяти и мультиплексору 2.

Таким образом, в данном устройстве надежность сохранения информации в накопителе обеспечивается тем, что отсутствуют одновременно режим регенерации и режим обращения, причем регенерация осуществляется с часто- той генератора, величина которой в расчетное число раз выше частоты воз- можных обращений. В нем также обеспечены приоритетные режимы обслуживания каналов (их можно увеличить ана- логичным образом, как показано для двух каналов на фиг. 1).

Формула изобретения

1. Динамическое запоминающее устройство, содержащее блок памяти, мультиплексор, счетчик адресов, блок синхронизации, триггер, инверсный выход которого подключен к входу ре- генерации блока памяти и к первому управляющему входу мультиплексора, информационные входы первой группы которого являются адресными входами первой группы устройства, выходы мультиплексора подключены к адресным входам блока памяти, входы-выходы которого являются информационными входами-выходами устройства, входы второй группы мультиплексора под- ключены к выходам счетчика адресов, вход сброса которого является входом начальной установки устройства, вход задания режима блока памяти является входом задания режима уст- ройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит блок приоритета обращения, первый и второй элементы И, первые входы которых подключены к инверсному выходу триг- ,гера, вторые входы первого и второго элементов И подключены соответственно к первому и второму выходам блока синхронизации, третий и четвер- тый выходы которого подключены соответственно к первому и второму входам синхронизации блока приоритета обращения, вход регенерации которого подключен к прямому выходу триггера, вход установки которого подключен к выходу первого элемента И, третий вход которого подключен к выходу наличия обращения блока приоритета

с ю J5

20

5 30 ,5 о 5

5

обращения, выход второго элемента И подключен к счетному входу счетчика адресов, первый и второй выходы блока приоритета обращения подключены соответственно к второму и третьему управляющим входам мультиплексора, информационные входы третьей группы которого являются адресными входами второй группы устройства, первый и второй выходы разрешения работы блока приоритета обращения являются соответствующими выходами устройства, выход блока синхронизации является входом запуска устройства, выход разрешения регенерации блока приоритета обращения подключен к входу установки триггера.

20 Устройство по п. 1, о т л и- чающе еся тем, что блок приоритета обращения содержит триггеры с второго по пятый, элементы И с третьего по шестой и элементы ИЛИ, причем входы установки второго и третьего триггеров являются соответственно первым и вторым входами обращения блока приоритета обращения., входы сброса второго и третьего триггеров подключены к выходам соответственно первого и второго элементов ИЛИ, первые входы которых подключены к первому входу третьего элемента ИЛИ, выход которого является выходом разрешения регенерации блока приоритета обращения и подключен к входам сброса четвертого и пятого триггеров, входы установки которых подключены к выходам соответственно третьего и четвертого элементов И, первые и вторые входы которых соответственно объединены и являются соответственно входом регенерации и первым входом синхронизации блока приоритета обращения, прямой выход второго триггера подключен к третьему входу третьего элемента И и к первому входу четвертого элемента ИЛИ, второй вход которого подключен к выходу третьего триггера и к третьему входу четвертого элемента И, четвертый вход которого подключен к инверсному выходу второго триггера, выход ,первого элемента ИЛИ является выходом наличия обращения блока приоритета обращения, выходы четвертого и пятого триггеров являются соответственно первым и вторым выходами управления мультиплексором блока приоритета обращения и подключены к первым вхо-

дам соответственно пятого if шестого элементов И, вторые входы которых объединены и являются вторым входом синхронизации блока приоритета обра1 щения, выход пятого элемента И явля1 ется первым выходом разрешения рабо ты блока приоритета обращения и под ключей к вторым входам первого и третьего элементов ИЛИ и к первому

818546

входу пятого элемента ИЛИ, выход которого является выходом обращения блока приоритета обращения, выход шестого элемента И является вторым входом разрешения работы блока приорите- . та обращения и подключен к второму входу второго элемента ИЛИ, к третьему входу третьего элемента ИЛИ и к Ю второму входу пятого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое полупроводниковое запоминающее устройство | 1987 |

|

SU1439680A1 |

| Запоминающее устройство | 1986 |

|

SU1437915A1 |

| Запоминающее устройство | 1985 |

|

SU1256096A1 |

| Устройство управления динамической памятью | 1990 |

|

SU1735858A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Устройство управления динамической памятью | 1990 |

|

SU1777143A2 |

| УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ | 1992 |

|

RU2049363C1 |

| Устройство для регенерации информации динамической памяти | 1988 |

|

SU1635213A1 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение надежности устройства. Динамическое запоминающее устройство содержит блок 1 памяти, мультиплексор 2, блок 3 синхронизации, счетчик 4 адресов, блок 5 приоритета обращения, триггер 6, элементы И 7 и 8. В устройстве обеспечивается режим регенерации и режим обращения, причем регенерация осуществляется с частотой, величина которой выше частоты возможных обращений. В нем также обеспечены приоритетные режимы обслуживания запросов от нескольких потребителей. 1 з.п.ф-лы, 2 ил.

Bb/X элем.

НМ17

П

Фиг. 2

| Запоминающее устройство | 1976 |

|

SU705901A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| А.Ю | |||

| Гордонова | |||

| - М.: Радио и связь, 1981, с | |||

| Способ получения морфия из опия | 1922 |

|

SU127A1 |

| Автоматический замыкатель для пожарной сигнальной цепи | 1925 |

|

SU3019A1 |

Авторы

Даты

1989-05-23—Публикация

1987-04-13—Подача