20

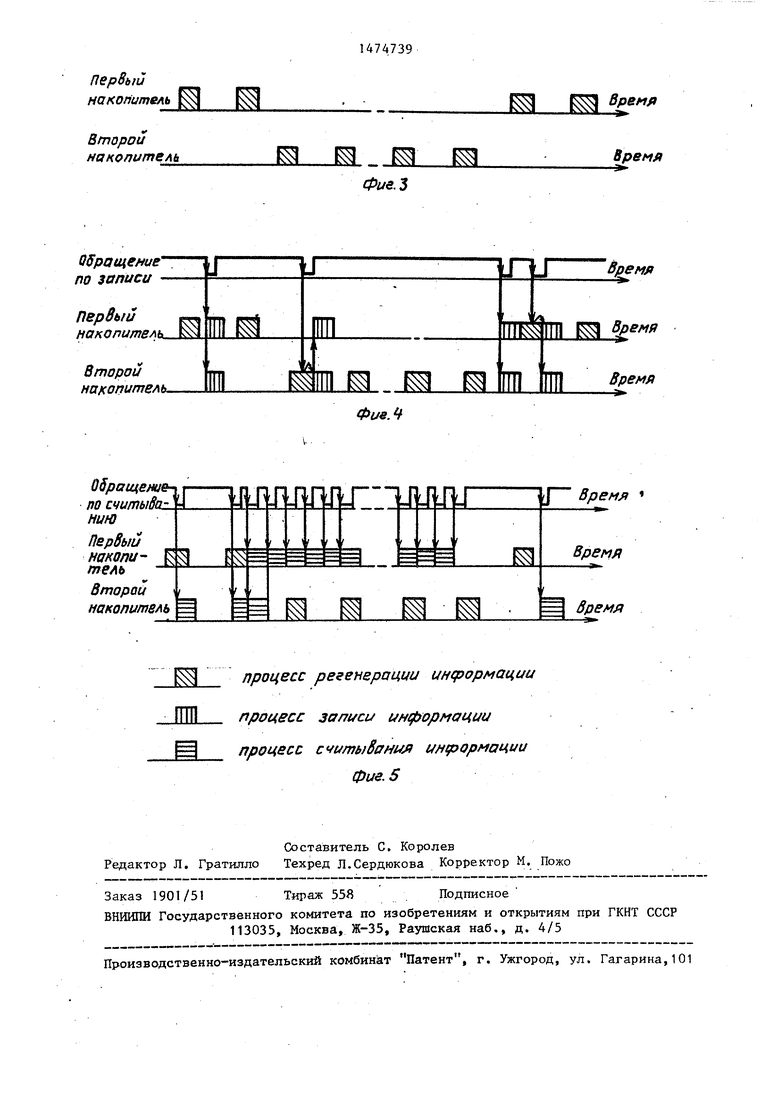

на фиг. 4 - то же, для случаев отсут-15 гической единицы. Причем состояния ствия обращения по записи; на фиг. 5 - то же, для случаев отсутствия обращения по считыванию.

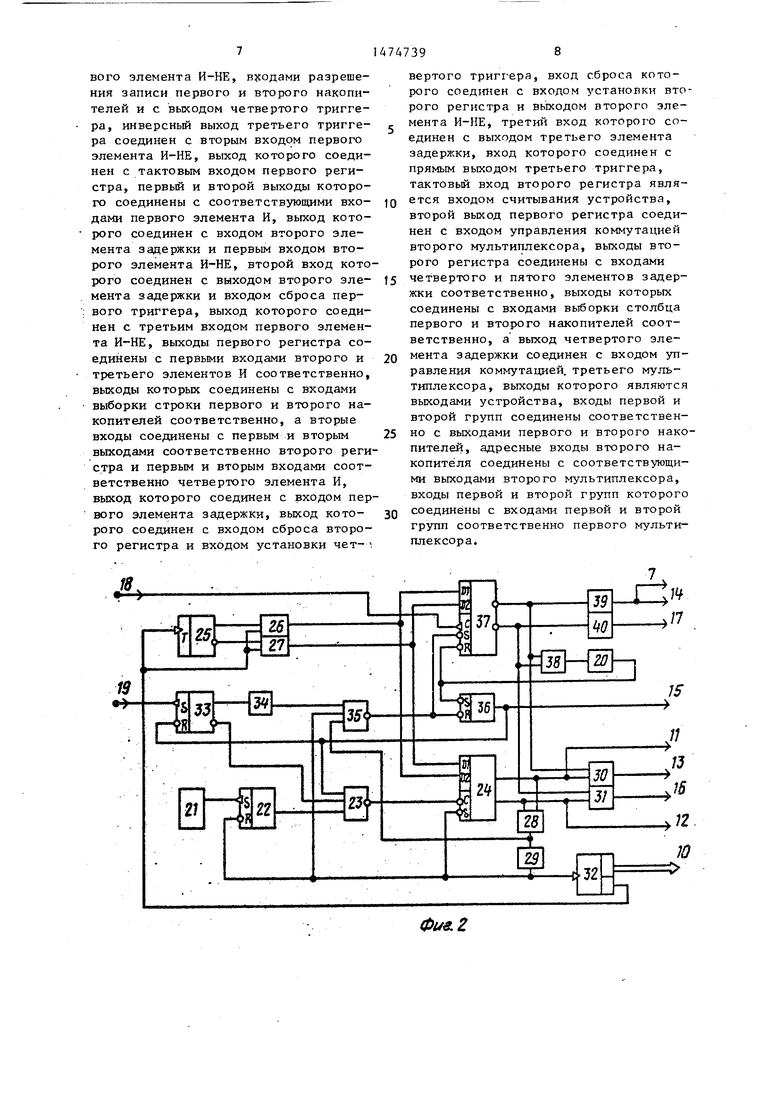

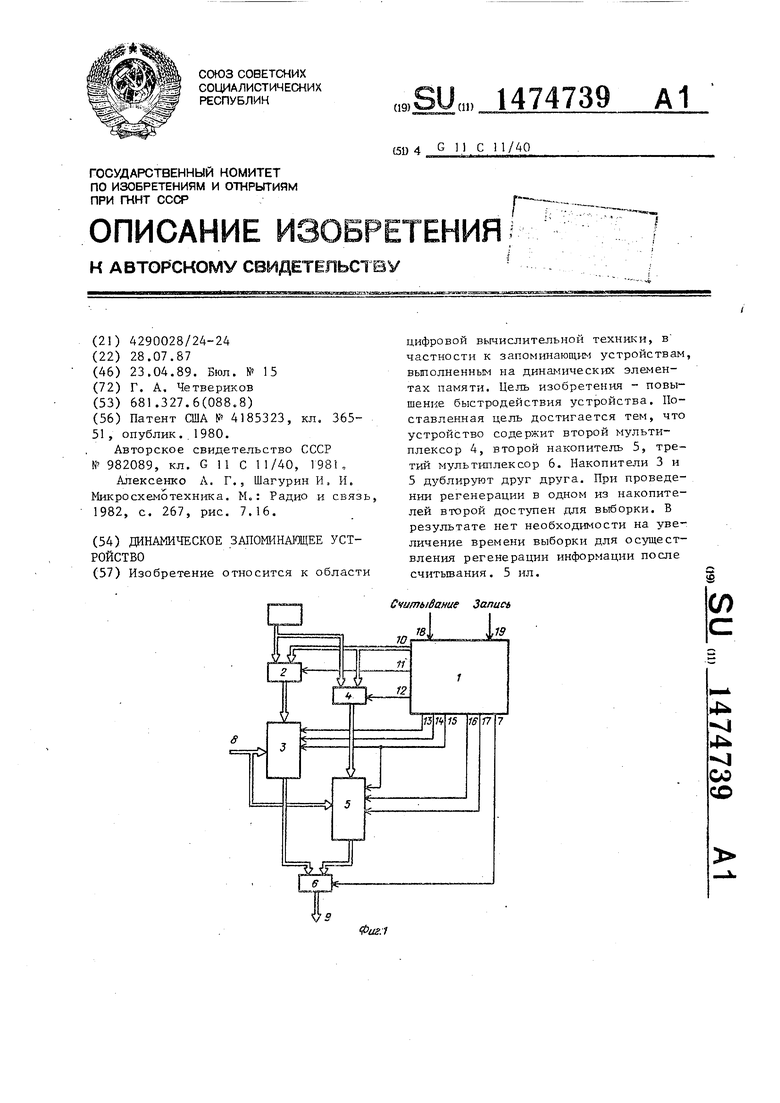

Устройство содержит блок 1 управления, первые мультиплексор 2 и накопитель 3, вторые мультиплексор 4 и накопитель 5, третий мультиплексор 6, выход 7 выбора накопителя блока 1, информационные входы 8, выходы 9, выходы 10 адреса регенерации блока 1, 25 первый и второй выходы 11 и 12 разрешения регенерации блока 1, первый и второй выходы 13 и 14 выборки блока 1, выход 15 признака записи блока 1, третий и четвертый выходы 16 и 17 30 выборки блока 1, входы 18 и 19 разрешения считывания и записи устройства

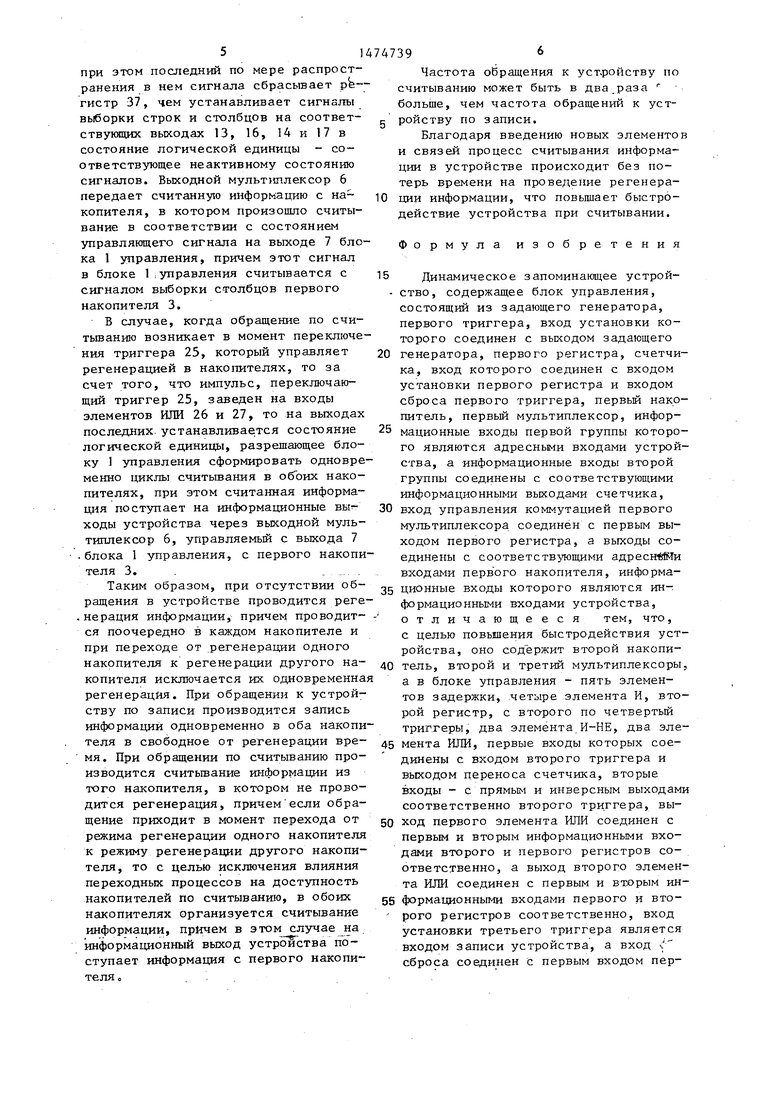

Блок 1 управления содержит первый элемент 20 задержки, задающий генератор 21, первьй триггер 22, первый 35 элемент И-НЕ 23, первый регистр 24, второй триггер 25, элементы ИЛИ 26 и 27, первый элемент И 28, второй элемент 29 задержки, второй и третий элементы И 30 и 31, счетчик 32, третий триггер 33, третий элемент 34 задержки, второй элемент И-НЕ 35, четвертый триггер 36, второй регистр 37, четвертый элемент И 38, четвертый и пятый элементы 39 и 40 задержки. 45

Устройство работает следующим образом.

В работе устройства можно выделить три режима работы: режим отсутствия обращений со стороны процессора, ре- 0 жим обращения со стороны процессора по записи, режим обращения Со стороны процессора по считыванию. При этом ситуация, когда процессор обращается

этих элементов обеспечиваются взаим ными связями и никаких воздействий по предварительной их установке не требуется.

Задающий генератор 21 вырабатыва ет последовательность импульсов. По каждому импульсу с задающего генера тора 21 блок 1 управления вырабалзы- вает на выходе 16 сигнал выборки строки первого накопителя 3, одновр менно с этим первый мультиплексор

2по управляющему сигналу с выхода блока 1 управления передает на адре ные входы первого накопителя 3 адре регенерации с выходов 10 блока 1 уп равления. Формирование сигнала выбо ки строк при регенерации осуществля ется в блоке 1 управления путем воз действия импульсов задающего генера тора 21 на цепочку элементов, состо щую из триггера 22, элемента И-НЕ 2 регистра 24, элемента И 28 и элемен 29 задержки, причем последний опред ляет длительность цикла регенерации

40 Накопитель, в котором должна проводиться регенерация, определяется со стоянием триггера 25, причем логиче кий ноль на его прямом выходе разре шает регенерацию в первом накопител

3и запрещает во втором накопителе

5, а логическая единица разрешает р генерацию во втором накопителе и запр щает в первом. По окончании каждого ци ла регенерации счетчик 32 по сигналу с выхода элемента 29 задержки прибавл ет к своему содержимому единицу, а при переходе содержимого счетчика 3 от всех логических единиц к состоян всех логических нулей на выходе пер

0

гической единицы. Причем состояния

5 0

5 5

0

этих элементов обеспечиваются взаимными связями и никаких воздействий по предварительной их установке не требуется.

Задающий генератор 21 вырабатывает последовательность импульсов. По каждому импульсу с задающего генератора 21 блок 1 управления вырабалзы- вает на выходе 16 сигнал выборки строки первого накопителя 3, одновременно с этим первый мультиплексор

2по управляющему сигналу с выхода 11 блока 1 управления передает на адресные входы первого накопителя 3 адрес регенерации с выходов 10 блока 1 управления. Формирование сигнала выборки строк при регенерации осуществляется в блоке 1 управления путем воздействия импульсов задающего генератора 21 на цепочку элементов, состоящую из триггера 22, элемента И-НЕ 23, регистра 24, элемента И 28 и элемента 29 задержки, причем последний определяет длительность цикла регенерации.

0 Накопитель, в котором должна проводиться регенерация, определяется состоянием триггера 25, причем логический ноль на его прямом выходе разрешает регенерацию в первом накопителе

3и запрещает во втором накопителе

5, а логическая единица разрешает ре- генерацию во втором накопителе и запрещает в первом. По окончании каждого цикла регенерации счетчик 32 по сигналу с выхода элемента 29 задержки прибавляет к своему содержимому единицу, а при переходе содержимого счетчика 32 от всех логических единиц к состоянию всех логических нулей на выходе пере

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое запоминающее устройство с восстановлением информации | 1989 |

|

SU1689990A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1088066A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

| УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ ИНФОРМАЦИИ ДИНАМИЧЕСКОЙ ПАМЯТИ | 1992 |

|

RU2049363C1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

Изобретение относится к области цифровой вычислительной техники, в частности к запоминающим устройствам, выполненным на динамических элементах памяти. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит второй мультиплексор 4, второй накопитель 5, третий мультиплексор 6. Накопители 3 и 5 дублируют друг друга. При проведении регенерации в одном из накопителей второй доступен для выборки. В результате нет необходимости на увеличение времени выборки для осуществления регенерации информации после считывания. 5 ил.

к устройству и по записи, и по считы- 55 носа формируется импульс, который пованию в пределах одного цикла работы устройства, считается запрещенной и соответствует неисправности процессора-.

ступает на счетньй вход триггера 25 и по длительности равен удвоенному времени переключения этого триггера, Одновременно этот импульс поступает

ступает на счетньй вход триггера 25 и по длительности равен удвоенному времени переключения этого триггера, Одновременно этот импульс поступает

на входы элементов ИЛИ 26 и 27 и на время переходных процессов в триггере 25 устанавливает их выходы в состояние логической единицы. Это не- , обходимо для того, чтобы в момент переключения триггера 25, т.е. перехода блока 1 управления от регенерации первого .накопителя 3 к регенерации второго накопителя 5, исключить на JQ выходах элементов ИЛИ 26 и 27 состояние логических нулей, разрешающих регенерацию в обоих накопителях 3 и 5 и запрещающих доступ по считыванию них После переключения триггера 15 25 блок 1 управления тем самым переодит к регенерации второго накопителя 5, при которой аналогично вырабатывается сигнал выборки строк ячеек памяти второго накопителя 5 с вы-- 20 ода блока 1 управления и аналогично происходит управление вторым мультиплексором. 4, который под воздействием управляющего сигнала с выхода 12 блока 1 управления передает с выхода 25 10.блока 1 управления на адресные входы второго накопителя 5 адрес регенерации. По переполнении счетчика 32 адресов регенерации блок 1 управения переключением триггера 25 пере-30 ходит обратно к регенерации первого накопителя 3 и этот процесс циклически повторяется на протяжении всей работы устройства.

При обращении к устройству по за- 35 писи триггер 33 запоминает это обращение и своим инверсным выходом временно запрещает запуск очередного цикла регенерации, с его прямого выхода заявки на запись через элемент 40 34 задержки поступает на вход элемента И-НЕ 35, который запрещает запись, если в накопителе не закончился предыдущий цикл регенерации, что определяется состоянием элемента И 28 и Д5 элементом 29 задержки, к которым подключены соответствующие входы элемента И-НЕ 35. В случае, если регенерация закончилась, то на выходе элемента И-НЕ 35 появляется сигнал, который„ обнуляет тригер 36, который выдает через выход 15 блока 1 управления в накопители сигнал записи, устанавливает инверсные выходы регистра 37 в состояние логического нуля, запрещает

55

запуск регенерации на время цикла за- писи и сбрасывает триггер 33. С инверсных выходов регистра 37 через элементы И 30 и 31 в накопители 3 и

, Q 5 0 5 0

5 0 5

5

5 поступают сигналы выборки строк ячеек памяти, которые с выходов 13 и 16 поступают одновременно соответственно в первый и второй накопители 3 и 5, а с элементов задержки 39 и 40 в накопители поступают сигналы выборки столбцов ячеек памяти через выходы 14 и 17 блока 1 управления соответственно в первый и второй накопители 3 и 5. При этом регистр 24 находится в таком состоянии, что сигналы с выходов 11 и 12 блока 1 управления, управляющие соответственно первым и вторым мультиплексорами 2 и 4, устанавливают последние в режим передачи на адресные входы накопителей адреса записи с адресных входов устройства. Указанная совокупность сигналов вызывает одновременно в накопителях 3 и 5 запись- информации с информационных входов устройства. При этом цикл записи определяется задержкой в элементе И 38 и элементе 20 задержки, причем последний по мере распространения сигнала в нем сбрасывает регистр 37 и устанавливает логическую единицу в триггер 36, которая указывает на окончание цикла записи и разрешает проведение регенерации и последующих обращений процессора.

При обращении к устройству по считыванию обращение с входа 18 устройства поступает на стробирующий вход регистра 37, в котором сразу же формируется сигнал-выборки строк, в элементе 39 или 40 задержки - сигнал выборки столбцов соответственно первого или второго накопителя 3 или 5, который в этот момент не занят регенерацией информации - это определяется состоянием выходов элементов ИЛИ 26 и 27, которые связаны с выходами триггера 25, который своим состоянием указывает в каком накопителе не проводится регенерация,и следовательно, доступен по считыванию, При этом регистр 24 состоянием своих выходов управляет мультиплексорами 2 и 4 так, что в соответствующий накопитель, где проводится регенерация, поступает адрес регенерации с выходов 10 блока 1 управления, а в накопитель свободный от регенерации, поступает адрес считывания с адресных входов устройства. Длительность цикла считывания определяется задержкой в элементе II 38 и элементе 20 задержки,

при этом последний по мере распространения в нем сигнала сбрасывает ре- истр 37, чем устанавливает сигналы ыборки строк и столбцов на соответствующих выходах 13, 16, 14 и 17 в состояние логической единицы - сответствующее неактивному состоянию сигналов. Выходной мультиплексор 6 ередает считанную информацию с накопителя, в котором произошло считывание в соответствии с состоянием управляющего сигнала на выходе 7 блоа 1 управления, причем этот сигнал в блоке 1 управления считывается с игналом выборки столбцов первого накопителя 3.

В случае, когда обращение по считыванию возникает в момент переключения триггера 25, который управляет регенерацией в накопителях, то за счет того, что импульс, переключающий триггер 25, заведен на входы элементов ИЛИ 26 и 27, то на выходах последних устанавливается состояние логической единицы, разрешающее блоку 1 управления сформировать одновременно циклы считывания в обЪих накопителях, при этом считанная информация поступает на информационные выходы устройства через выходной мультиплексор 6, управляемый с выхода 7

блока 1 управления, с первого накопителя 3.

Таким образом, при отсутствии обращения в устройстве проводится регене рация информации, причем проводит- - ся поочередно в каждом накопителе и при переходе от регенерации одного накопителя к регенерации другого накопителя исключается их одновременная регенерация. При обращении к устройству по записи производится запись информации одновременно в оба накопителя в свободное от регенерации время. При обращении по считыванию производится считывание информации из того накопителя, в котором не проводится регенерация, причем если обращение приходит в момент перехода от режима регенерации одного накопителя к режиму регенерации другого накопителя, то с целью исключения влияния переходных процессов на доступность накопителей по считыванию, в обоих накопителях организуется считывание информации, причем в этом случае на нформационный выход устройства поступает информация с первого накопителя.

Частота обращения к устройству по считыванию может быть в два раза л больше, чем частота обращений к уст- ройству по записи.

Благодаря введению новых элементов и связей процесс считывания информации в устройстве происходит без потерь времени на проведение регенера- ции информации, что повышает быстродействие устройства при считывании.

Формула изобретения

Динамическое запоминающее устройство, содержащее блок управления, состоящий из задающего генератора, первого триггера, вход установки которого соединен с выходом задающего генератора, первого регистра, счетчика, вход которого соединен с входом установки первого регистра и входом сброса первого триггера, первый накопитель, первьй мультиплексор, информационные входы первой группы которого являются адресными входами устройства, а информационные входы второй группы соединены с соответствующими информационными выходами счетчика,

вход управления коммутацией первого мультиплексора соединен с первым выходом первого регистра, а выходы соединены с соответствующими адрес№йм и входами первого накопителя, информационные входы которого являются информационными входами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит второй накопитель, второй и третий мультиплексоры, а в блоке управления - пять элементов задержки, четыре элемента И, второй регистр, с второго по четвертый триггеры, два элемента И-НЕ, два элемента ИЛИ, первые входы которых соединены с входом второго триггера и выходом переноса счетчика, вторые входы - с прямым и инверсным выходами соответственно второго триггера, выход первого элемента ИЛИ соединен с первым и вторым информационными входами второго и первого регистров соответственно, а выход второго элемента ИЛИ соединен с первым и вторым информационными входами первого и второго регистров соответственно, вход установки третьего триггера является входом записи устройства, а вход ч сброса соединен с первым входом первого элемента И-НЕ, входами разрешения записи первого и второго накопителей и с выходом четвертого триггера, инверсный выход третьего тригге- ра соединен с вторым входом первого элемента И-НЕ, выход которого соединен с тактовым входом первого регистра, первый и второй выходы которого соединены с соответствующими вхо- дами первого элемента И, выход которого соединен с входом второго элемента задержки и первым входом второго элемента И-НЕ, второй вход которого соединен с выходом второго эле- мента задержки и входом сброса первого триггера, выход которого соединен с третьим входом первого элемента И-НЕ, выходы первого регистра соединены с первыми входами второго и третьего элементов И соответственно, выходы которых соединены с входами выборки строки первого и второго накопителей соответственно, а вторые входы соединены с первым и вторым выходами соответственно второго регистра и первым и вторым входами соответственно четвертого элемента И, выход которого соединен с входом первого элемента задержки, выход кото- рого соединен с входом сброса второго регистра и входом установки четвертого триггера, вход сброса которого соединен с входом установки второго регистра и выходом второго элемента И-НЕ, третий вход которого соединен с выходом третьего элемента задержки, вход которого соединен с прямым выходом третьего триггера, тактовьй вход второго регистра является входом считывания устройства, второй выход первого регистра соединен с входом управления коммутацией второго мультиплексора, выходы второго регистра соединены с входами четвертого и пятого элементов задержки соответственно, выходы которых соединены с входами выборки столбца первого и второго накопителей соответственно, а выход четвертого элемента задержки соединен с входом управления коммутацией, третьего мультиплексора, выходы которого являются выходами устройства, входы первой и второй групп соединены соответственно с выходами первого и второго накопителей, адресные входы второго накопителя соединены с соответствующими выходами второго мультиплексора, входы первой и второй групп которого соединены с входами первой и второй групп соответственно первого мультиплексора.

Фиг. 2

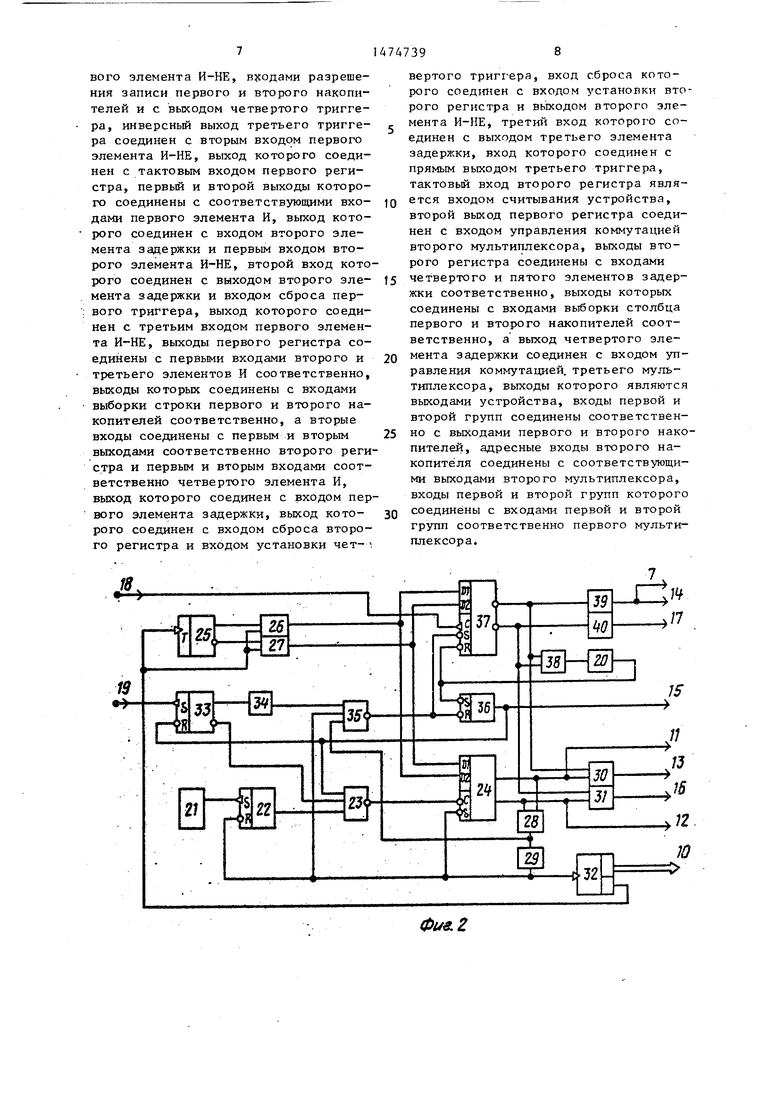

процесс регенерации информации

ПТП процесс записи информации процесс считыВания информации

ФиеЛ

| Патент США N 4185323, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Оперативное запоминающее устройство на динамических элементах памяти | 1981 |

|

SU982089A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Г., Шагурин И, И | |||

| Микросхеметехника | |||

| М.: Радио и связь, 1982, с | |||

| Тепловой измеритель силы тока | 1921 |

|

SU267A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1989-04-23—Публикация

1987-07-28—Подача