Изобретение относится к импульсно технике и может быть использовано в системах автоматической обработки данных.

Целью изобретения является повышение достоверности функционирования устройства за счет контроля блоков памяти в процессе формирования кодо- вьк последовательностей.

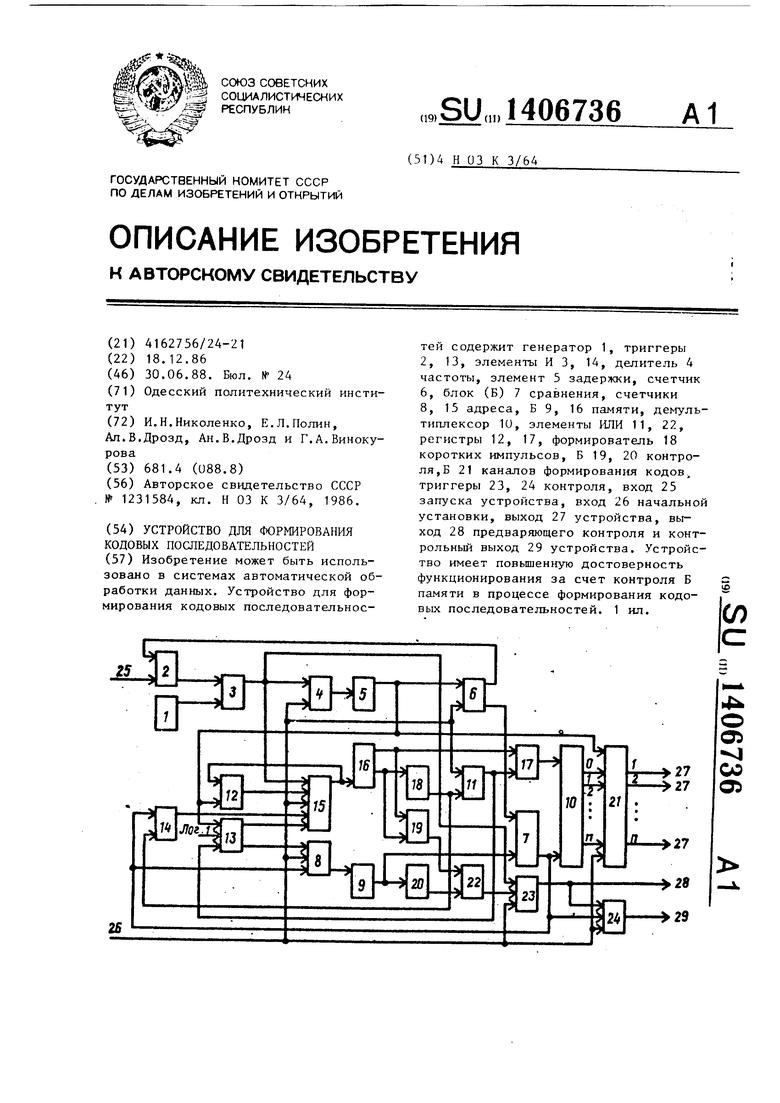

На чертеже представлена структурная схема предлагаемого устройства.

Устройство для формирования кодо- вых последовательностей содержит генератор 1, первый триггер 2, элемент ИЗ, делитель 4 частоты, элемент 5 задержки, счетчик 6 импульсов, блок 7 сравнения, первый счетчик 8 адреса блок 9 памяти, демультиплексор 10, элемент ИЛИ 11, регистр 12, второй триггер 13, дополнительный элемент И 14, второй счетчик 15 адреса, блок 16 памяти, регистр 17, формирователь 18 коротких импульсов, блоки 19, 20 контроля кодов по нечетности, блок 21 каналов формирования кодов, дополнительный элемент ИЛИ 22, триггеры 2 24 контроля, вход 25 запуска устройства, вход 26 начальной установки, выходы 27 устройства, выход 28 пред- варяющего контроля и контрольный выход 29 устройства, причем информационный вход триггера 13 подключен к уровню логической единицы, а синхро- вход объединен с синхровходом регистра 12 и подключен к выходу элемента 5 задержки, информационные входы регистра 12 соединены с выходами счетчика 15 адреса, а выходы соединены с информационными входами счетчика 15 адреса, вход сброса которого соединен с входом сброса счетчика 8 адреса, вход приема информации соедине с выходом элемента И 14, инверсный первый вход которого соединен с входом разрешения счета счетчика В адреса и выходом блока 7 сравнения, второй вход соединен с выходом формирователя 18, выходы и управляющий выход блока 16 памяти соединены с входами блока 19 контроля, выходы блока 9 памяти соединены с входами блока 20 контроля, выходы блоков 19, 20 контроля соединены с входами элемента ИЛИ 22, выход которого соединен с информационным входом триггера 23, синхровход которого соединен с выходом элемента ИЗ, R-вход объединен с R-входом триггера 24 и подклю

5

5 о 5 о 55

5

0

45

чен к входу 26 начапьной установки устройства, выход триггера 23 являet- ся выходом 28 предваряющего контроля устройства и соединен с синхровходом триггера 24, информационный вход которого соединен с выходом блока 7 сравнения, выход триггера 24 является контрольным выходом 29 устройства.

Блоки 19, 20 контроля вьтолнены на /сумматорах тго модулю два с инверсным выходом.

Триггер 24 для запоминания сигнала контроля выполнен на двух триггерах, первый из которых имеет входы общие с триггером 24, а выход соединен с синхровходом второго из триггеров, информационный вход которого соединен с уровнем логической единицы, вход сброса объединен с входом сброса первого Из триггеров, а выход является выходом триггера 24.

Устройство работает следующим образом.

Предварительно в блок 9 памяти записывается последовательность кодов - момента времени t (измеряемых в тактах работы устройства относительно момента его запуска), в которые необходимо изменить значение хотя бы одного из выходов 27 устройства. Запись осуществляется начиная с нулевого адреса, который записывается по адресной шине в порядке возрастания значений кодов t.

В блок 16 памяти записываются последовательно группы кодов. Каждая группа кодов взаимооднозначно соответствует одному коду момента времени t из блока 9 памяти и содержит коды номеров каналов (нри,что то же, самое, номеров выходов 27 устройства), которые изменяют свое состояние в соответствующем моменту времени t такте работы устройства. В группе ко ды перечисляются в произвольном порядке. Код номера канала содержит дополнительный разряд, принимающий в последнем коде каждой группы единичное значение и нулевое значение в других кодах. Этот признак окончания группы кодов считывается с управляющего выхода блока 16 памяти. Запись кодов группы в блок 16 памяти происходит, начиная с максимального значения адреса в сторону его убывания. Адрес на запись информации в блок 16 записывается по адресным шинам.

Пг рс д я.чпускпм ycTpiMirrna curFia- Jiop с входа 26 н;1члльно11 устаиогжи устройства сОрлсываются в нулевое состояние счетчики 8, 15 адреса, триггеры 23, 2Д контроля, Т-триггеры и D-триггеры блока 21 каналов формирования кодов, устанааливаются в единичное состояние триггеры делителя А частоты и счетчика 6, а через элемент Ш1И 11 сбрасываются в ноль также регистр 17 и триггер 13.

Импульс запуска, поступающий по входу 25 на вход установки триггера 2, устанавливает его в единичное состояние, разрешая прохождение импульсов с выхода генератора 1 через элемент И 3 на счетный вход счетчика 15 адреса, синхровход триггера 23 и через делитель 4 частоты на вход элемента 5 задержки, с выхода которого задержанные импульсы пониженной частоты, отмеряюпи1е такты работы устройства, одновременно пост тпают на синхровход блока 21, синхровходы триггера 13 и регистра 12 и счетный вход счетчика 6. При этом триггер 13 устанавливается в единичное значение путем приема постоянно поданного на информационный вход уровня логической единицы,

8регистр 12 через информационный вход записывается код состояния счетчика 15 адреса, а счетчик 6 по первому импульсу переходит в следующее нулевое состояние. Код с выходов счетчика 6 поступает на первые входы блока 7 сравнения. В это время блок

9памяти считывает по нулевому адресу поступающему с выходов первого счетчика 8 адреса, первый код момента времени t. Этот код времени поступает на вторые входы блока 7 сравнения, который уменьшает значение кода на единицу младшего разряда и сравнивает полученный результат с кодом счетчика 6. Сигнал с выхода блока 7 сравнения поступает на управляюи(ий вход демультигшексора 10, информационный вход триггера 24 и инверсный первый вход элемента И 14, разрешая при сравнении кодов работу демультиплексора

10и запрещая прохождение короткого импульса с выхода формирователя 18 через элемент И 14 на вход приема информации счетчика 15 адреса.

Триггер 13 при установке в единичное состояние разрешает сигналом с прямог о ны.хо/ьч изменение состояния счетчикя 13 ллреса под действием

0

5

5

0

5

0

5

0

5

поступаюии1Х на ci o Л1.1чит;жчций счст1п.|й вход синхросигналов. При этом смотчик 15 адреса формирует последовательность значенш адреса, по которым с выходов блока 16 памяти через регистр 17 считываются коды номеров каналов группы. Считанные коды поступают далее на адресный лход демультиплексора 10.

Одновременно со считыванием из блока 16 памяти последнего кода номера группы с управляющего выхода этого блока снимается единичный сигнал признака окончания группы. Этот сигнал поступает на вход формирователя 18, с выхода которого короткий импульс поступает через элемент ИЛИ 11 на вход сброса регистра 17 и на R- вход триггера 13, возвращая их в исходные нулевые состояния. Короткий импульс с выхода формирователя 18 поступает также на второй вход элемента И 14, обеспечивая при несравненш кодов восстановления исходного в такте состояния счетчика 15 путем приема кода, запомненного в регистре 12. Таким образом, при несравнении кодов блоком 7 счетчик 15 адреса в следующем такте повторяет последовательность формируемых адресов, а блок 16 памяти повторяет вьфаботку кодов гтзуп- пы.

При соответствии сравниваемых кодов демультиплексор 10 под действием поступающих на адресный вход кодов группы вырабатывает последовательно единичные значения на соответствующих выходах. Под действием единичных значений, поступаюш -1х на входы блока 21, соответствующие входные Т-триггеры блока 21 инвертируют свои значения, а выходные D-триггеры блока 21 принимают сигналы с выходов всех Т- триггеров и выдают их на вькоды 27 устройства по импульсам с делителя 4 частоты с наступлением нового такта, номер которого совпадает с номером такта на выходе счетчика 6. Таким образом происходит изменение сигналов на назначенных выходах 27 устройства в указанные моменты времени.

Одновременно в такте установления соответствия сравниваемых кодов сигнал с выхода блока 7 разрешает переход счетчика 8 адреса в следующее состояние под действием поступающего на его счетный вход сигнала с luinepc- ного выхода триггера 13 (при переходе триггера 13 в нулевое состояние под действием короткого импульса). По новому значению кода выхода счетчика 8 адреса из блока 9 памяти счи- тьшается код следующего момента времени t. Этот код, сравниваясь со значениями кода на выходах счетчика 6, отсчитывающего такты работы устройства, вновь определяет такт, предшествующий изменениям на выходах 27 устройства, и сигналом с выхода блока 7 сравнения разрешает подготовит (посредством демультиплексора 10 и Т- триггеров блока 21) изменение значений выходов 27 устройства.

При достижении счетчиком 6 максимального значения сигнал переполнения с выхода переноса поступает на вход сброса триггера 2 и переводит его в исходное нулевое состояние. При этом элемент И 3 перестает пропускать импульсы с выхода генератора 1 и устройство заканчивает свою работу.

Коды, записанные в блоки 9, 16 памяти, содержат также контрольные разряды, дополняющие эти коды до нечетного количества единиц. С выходов указанных блоков памяти коды поступают на входы блоков 19, 20 контрол Блоки 19, 20 контроля осуществляют контроль поступающих на их входы кодов по нечетности и формируют сигнал контроля К1 и К2, которые объединяются на элементе ИЛИ 22. С выхода элемента ИЛИ 22 объединенный сигнал контроля поступает на информационный вход триггера 23, в который принимается по синхросигналам с выхода элемента ИЗ. С выхода триггера 23 сигнал контроля поступает на выход 28 устройства, указывая на неправильное считывание кодов из блоков 9, 16 памяти не только в тактах их использования для изменения выходов 27 устройства - подготовительных тактах -, но также и на предшествующих им тактах, что предупреждает о возможной ошибке в дальнейшей работе устройства. С выхода триггера 23 сигнал контроля ностугЕает также на синхровход триггера 24, который принимает по этому сигналу значение сигнала с выхода блока 7 сравнения, подаваемого на информационный вход триггера 24. Таким образом триггер 24 принимает сигналы ошибки на подготовительных тактах, указ1 тая на неправильную

67366

работу устройства по его выходам 27. Сигнал контроля с выхода триггера 4 поступает на выход 29 устройства.

5

0

0

Формула изобретения

Устройство для формирования кодовых последовательностей, содержащее генератор, первый и второй триггеры, элементы И и ИЛИ, делитель частоты, элемент задержки, счетчик, блок сравнения, первый и второй счетчики адреса, первый и второй блоки памяти, демультиплексор, регистр, формирователь коротких импульсов и блок каналов формирования кодов, выход генератора соединен с первьм входом элемента И, второй вход которого соединен с выходом первого триггера, установочный вход которого является входом запуска устройства, выход элемента И соединен со счетным входом второго счетчика адреса и входом де5 лителя частоты, установочный вход которого соединен с установочным входом счетчика, входом сброса второго счетчика адреса и является входом начальной установки устройства, а выход делителя частоты соединен с входом элемента задержки, выход которого соединен с синхровходом блока каналов формирования кодов и счетным входом счетчика, выход переполнения которого соединен с R-входом первого триггера, а информационные выходы соединены с первыми входами блока сравнения, вторые входы которого соединены с выходами первого блока памяти, адресные входы которого соединены с выходами первого счетного адреса, вход сброса которого соединен с входом сброса блока каналов формирования кодов и первьм входом элемента ИЛИ, а счетный вход соединен с инверсным выходом второго триггера, прямой выход которого со.е- динен с входом разрешения счета второго счетчика адреса, выходы которого соединены с адресными входами второго блока памяти, управляющий выход которого соединен через формирователь коротких импульсов с вторым входом элемента ИЛИ, выход которого соединен с R-входом второго триггера и

входом сброса регистра, информационные входы которого соединены с выходами второго блока памяти, а выходы соединены с адресными входами демуль5

0

5

0

типлексора, управляющий вход которого соединен с выходом блока сравнения, а выходы соединены с информационными входами блока каналов формирования кодов, выходы которого являются выходами устройства, отличающееся тем, что, с целью повышения достоверности функционирования устройства, в него введены дополнитель- ные элементы И и ИЛИ, первый и второй блоки контроля, дополнительный регистр и первый и второй триггеры контроля, причем информационный вход второго триггера подключен к уровню логической единицы, а синхровход соединен с синхровходом дополнительного регистра и подключен к выходу элемента задержки, информационные входы дополнительного регистра соединены с выходами второго счетчика адреса, а выходы соединены с информационными входами второго счетчика адреса,вход сброса которого соединен с входом сброса первого счетчика адреса, а вход .приема информации соединен с выходом дополнительного элемента И, инверсный первый вход которого сое

динен с входом разрешения счета первого счетчика адреса и выходом блока сравнения, второй вход соединен с выходом формирователя коротких импульсов, выходы и управляющий выход второго блока памяти соединены с входами второго блока контроля, выходы первого блока памяти соединены с входами первого блока контроля, выходы первого и второго блоков контроля соединены с входами дополнительного элемента ИЛИ, выход которого соединен с информационным входом первого триггера контроля, синхровход которого соединен с выходом элемента И, R - вход соединен с R-входом второго триггера контроля и подключен к входу начальной установки устройства, выход первого триггера контроля является выходом предваряющего контроля устройства и соединен с синхровходом второго триггера контроля, информационный вход которого соединен с вы- ходом блока сравнения, а выход второго триггера контроля является контрольным выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования кодовых последовательностей | 1988 |

|

SU1554115A1 |

| Устройство для формирования кодовых последовательностей | 1986 |

|

SU1345322A1 |

| Устройство для формирования кодовых последовательностей | 1986 |

|

SU1439744A1 |

| Устройство для формирования кодовых последовательностей | 1988 |

|

SU1499438A2 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Устройство для регистрации неисправностей | 1986 |

|

SU1377858A1 |

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| Устройство для регистрации неисправностей | 1986 |

|

SU1429116A1 |

| Устройство для программируемой задержки информации | 1986 |

|

SU1394213A1 |

| Устройство для задержки цифровой информации | 1986 |

|

SU1383325A1 |

Изобретение может быть использовано в системах автоматической обработки данных. Устройство для формирования кодовых последовательностей содержит генератор 1, триггеры 2, 13, элементы ИЗ, 14, делитель 4 частоты, элемент 5 задержки, счетчик 6, блок (Б) 7 сравнения, счетчики 8, 15 адреса, Б 9, 16 памяти, демуль- типлексор 10, элементы ИЛИ 11, 22, регистры 12, 17, формирователь 18 коротких импульсов, Б 19, 20 контроля, Б 21 каналов формирования кодов триггеры 23, 24 контроля, вход 25 запуска устройства, вход 26 начальной установки, выход 27 устройства, выход 28 предваряющего контроля и контрольный выход 29 устройства. Устройство имеет повышенную достоверность функционирования за счет контроля Б памяти в процессе формирования кодовых последовательностей. 1 ил. (Л

| Устройство для формирования кодовых последовательностей | 1983 |

|

SU1231584A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-30—Публикация

1986-12-18—Подача