О5 4

а

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель температуры | 1986 |

|

SU1364910A1 |

| Амплитудно-фазовый анализатор гармоник | 1985 |

|

SU1272272A2 |

| Устройство для аналого-цифрового преобразования | 1987 |

|

SU1425828A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU930387A1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347027A1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛЫ ВРЕМЕНИ | 2014 |

|

RU2552605C1 |

| Генератор сигналов для формирования управляющих токов доменной памяти | 1989 |

|

SU1725255A1 |

| Масштабный преобразователь напряжения и его варианты | 1980 |

|

SU922780A1 |

| ВРЕМЯИМПУЛЬСНЫЙ КВАДРАТИЧНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1998 |

|

RU2149449C1 |

Изобретение относится к области технических средств коррекции систем автоматического управления и регулирования, в которых может быть использовано для компенсации инерционных свойств блоков неизменяемой части системы путем создания фазоопережа- ющих свойств сигнала управления, может быть также использовано в системах с нефкльтрующими свойствами и является усовершенствованием известного устройства по авт. св. №767700. Целью изобретения является расширение диапазона сигналов, корректируемых устройством. Поставленная цель достигается за счет того, что в устройстве анализизируется вид входного сигнала и определяется его признак. Если сигнал аналоговой, Ьн преобразуется в ступенчатьй сигнал, сравнивается с исходным сигналом, и полученная разность суммируется с исходным сигналом. Если сигнал ступенчатый, то он дважды преобразуется в ступенчатый сигнал под действием двух тактовых последовательностей, сдвинутых на такт одна относительно другой, новые ступенчатые сигналы сравниваются с исходным, полученные разности суммируются, интегрируются на протяжении каждого такта, а результаты интегрирования суммируются с исходным сигналом. 7 ил. с «3 (Л 4 4

гч

Изобретение относится к техническим средствам коррекции систем автоматического управления и регулирования,, в которых может быть использо- вано для компенсации инерционных свойств блоков неизменяемой части системы путем создания фазопередаю- щих свойств сигнала управления, а также может быть использовано в сие- темах с нефильтрующими свойствами.

Целью изобретения является расширение диапазона сигналов, корректируемых устройством.

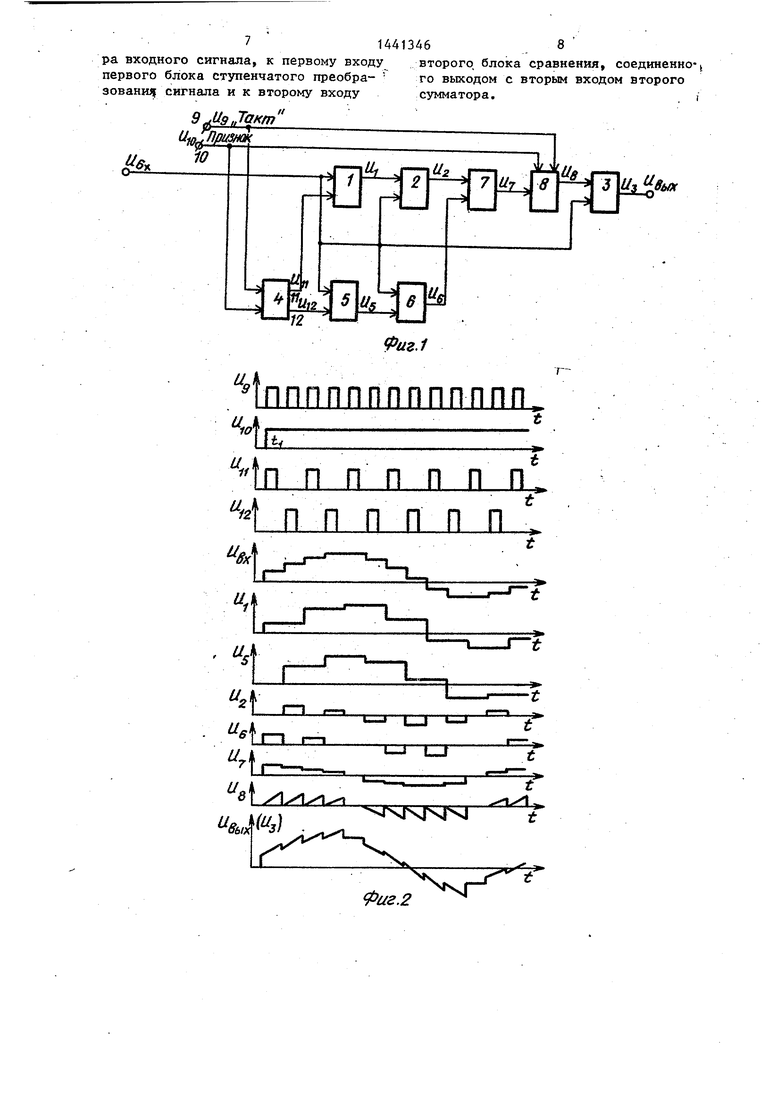

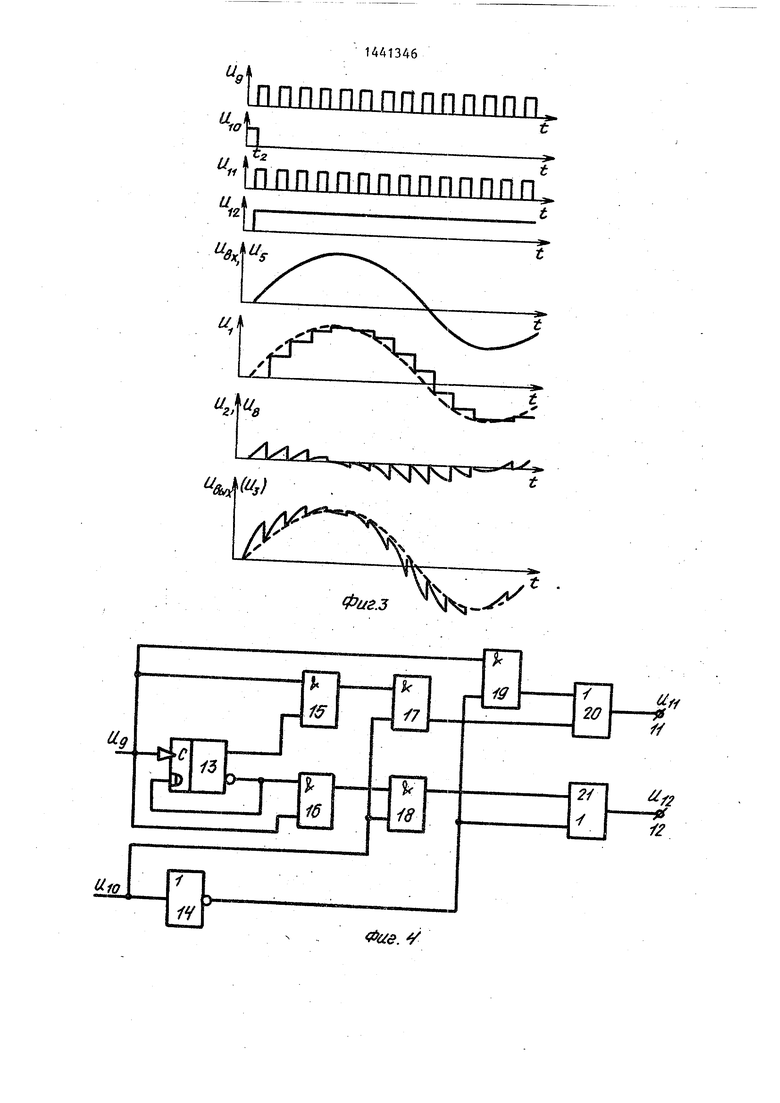

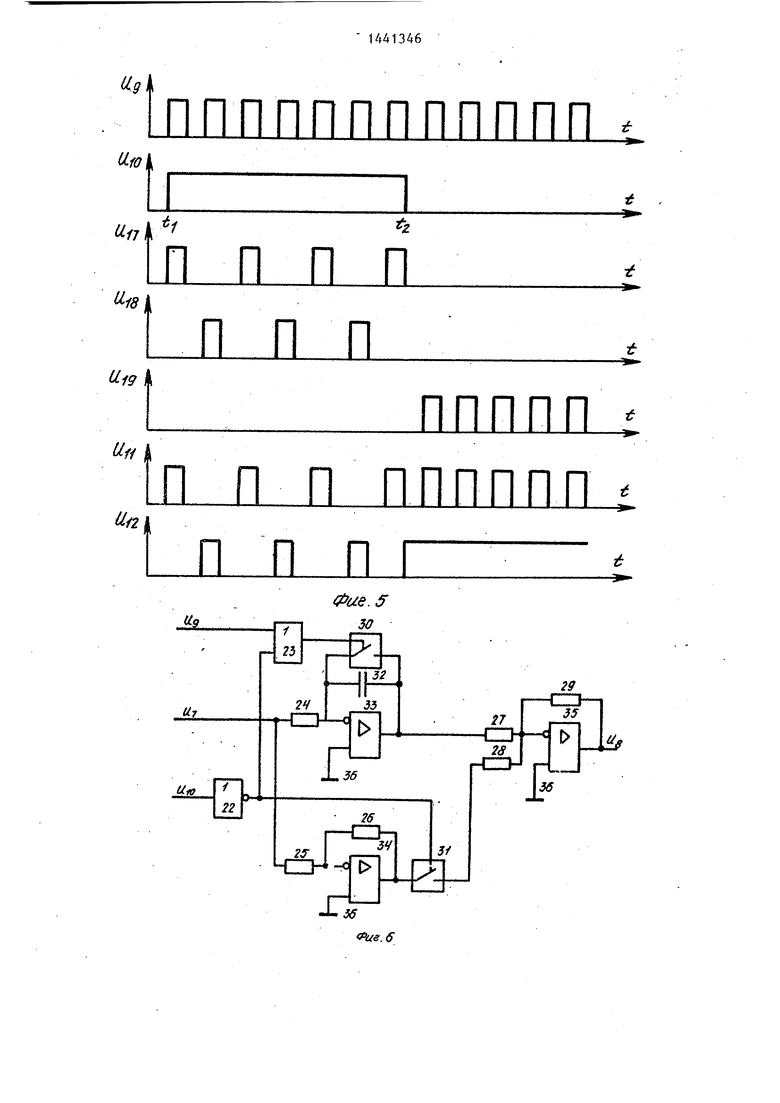

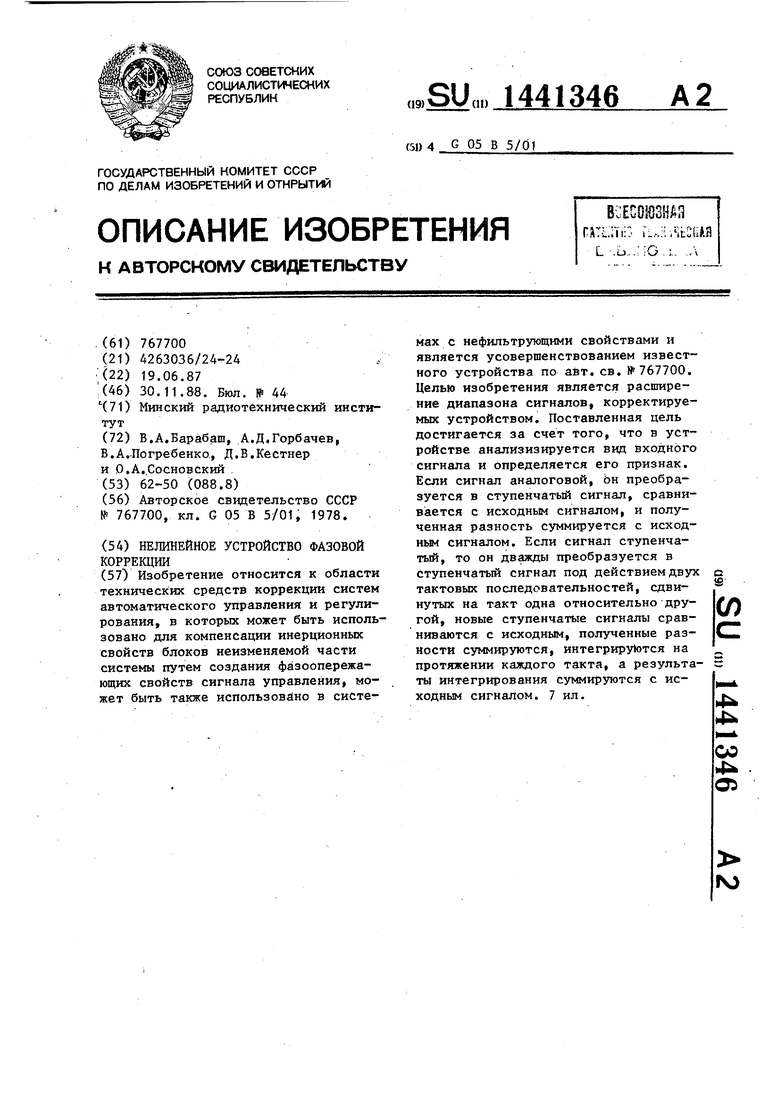

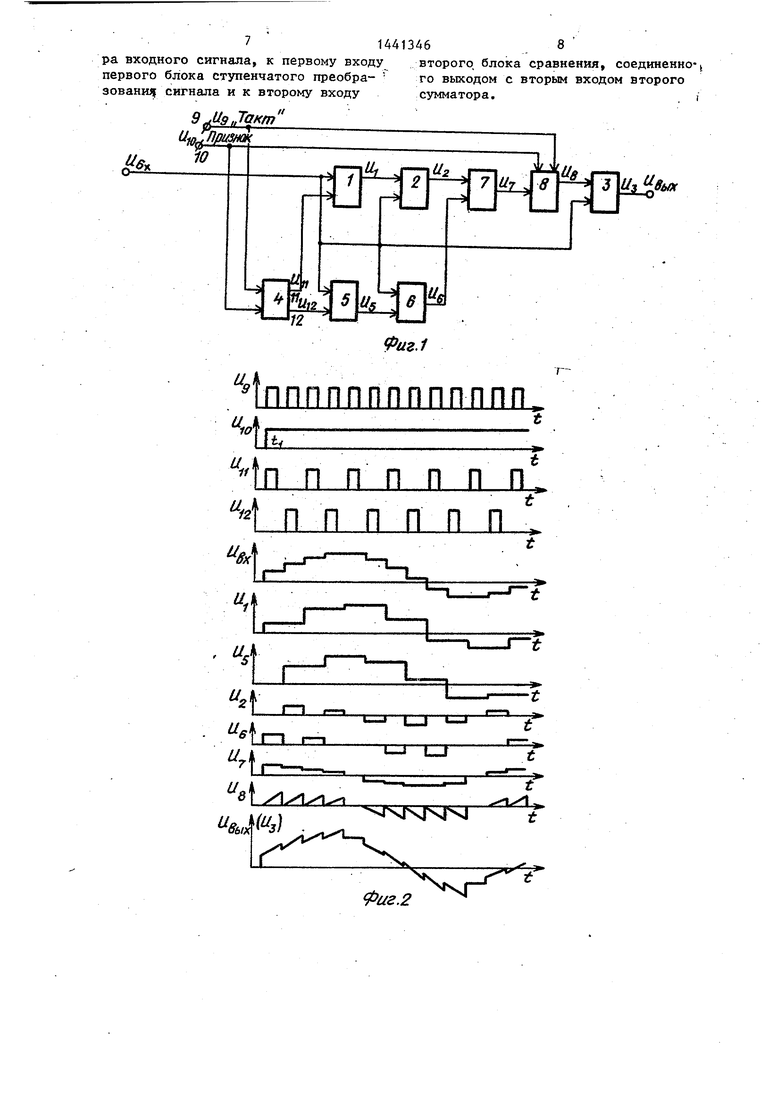

На фиг,1 представлена блок-схема описываемого устройства} на фиг,2 - временные диаграммы работы устройства при дискретном входном сигнале; на фиг.З - временные диаграммы работы устройства при непрерывном входном сигнале; на фиг.4 - принципиальная электрическая схема распределителя импульсов; на фиг.5- - временные диаграммы его работы; на фиг,6 - принципиальная схема управляемого инте- грала; на фиг. 7 - принципиальная электрическая схема блока ступенчатого преобразования сигнала.

Нелинейное устройство фазовой кор- рекции содержит первьй блок 1 ступенчатого преобразования сигнала, первый блок 2 сравнения, первьй сумматор 3, распределитель 4 импульсов, второй ; блок 5 ступенчатого преобразования сигнала, второй блок б сравнения, второй сумматор 7, управляемый интегратор 8, тактовый вход 9 и вход 10 признак входного устройства, первьй 11 и второй 12 выходы распределителя 4 импульсовJ делитель 13 час- тоты импульсов на два, элемент НЕ 14 элементы И 15 - 19, элементы ШШ 20, ,21, элемент НЕ 22, элемент ШШ 23, резисторы 24 - 29, ключи 30, 31, конденсатор 32, операционные усилители 33 - 35, общую шину 36, ключ 37, Конденсатор 38, резистор 39, операционный усилитель 40, Кроме того, на чертежах обозначены: U g, - входной сигнал устройства; U- - выходной сигнал i-ro блока i и,г9 Ur2 сигналы на первом и втором входах р;аспределите- ля импульсов; U - сигнал признаков типа входного сигнала Ujy который принимает значение логического нуля, если входной сигнал U g - не- прерывный, и значение логической единицы, если входной сигнал U. - дискретный.

-

0

Распределитель 4 и чпульсов (фиг.4) служит для формирования импульсных последовательностей U и U у, обеспечивающих правильное функционирование блоков 1 и 5 ступенчатого преобразования сигнала. На его вход посту- пшот импульсы иg тактовой частоты (фиг,5), Если сигнал признака и представляет собой логическую единицу (входной сигнал дискретный), то импульсы тактовой частоты делятся на два делителем 13 и через элементы И 15, 17 и элемент ИЛИ 20 поступают на выход 11 в виде сигнала U , Элемент И 19 закрыт сигналом признака и,„ через элемент НЕ 14, В этом же режиме И1« пульсы тактовой частоты, деленные на два делителем 13, через элементы И 16, 18 и элемент ИЛИ 21 поступают на выход 12 распределителя 4 импульсов. В результате на обоих выходах распределителя 4 будут сформированы две последовательности импульсов с частотой, деленной на два по отношеншо к тактовой частоте, причем на выходе 12 импульсы U,,,j смещены на такт по отношению к импуль- сам и,, на выходе 11 (фиг.З),

Когда сигнал признака U,p становится логическим нулем (аналоговый входной сигнал), то закрываются элементы И 17,- 18, а на выходе 11 появляются шпульсы и тактовой частоты- Выходной сигнал элемента НЕ 14 обеспечивает через элемент РШИ 21 появление единичного импульса U на выходе 12 распределителя 4 импульсов (фиг,5).

Интегратор 8 (фиг.б) служит для формирования фазоопережающих добавок в режиме работы, когда входной сигнал Uax дискретный, В режиме работы, когда входной сигнал Ug - аналоговый, интегратор 8 представляет собой усилитель с коэффициентом усиления, равным единице. Если признак сигнала U - единичный (дискретный входной сигнал), то через элемент НЕ 22 ключ 31 разомкнут, а через элемент ИЛИ 23 на ключ 30 поступают импульсы т актовой частоты Ug, Каждьй импульс тактовой частоты замыкает ключ 30 и тем самым сбрасывает в нуль, интегратор 8, собранный на операционном усилителе 33, резисторе 24, конденсаторе 32, В период между так- овымн импульсами Ug интегратор 8 осуществляет интегрирование напряжения и,, Через суммирующий усилитель, собранный на операционном усилителе 35, резисторах 27 - 29, на выходе интегратора 8 формируется выходной сигнал Ug, представляющий собой на каждом малом промежутке времени линейно нарастающее напряжение. Скорость изменения этого напряжения определяется амплитудным значением сиг- ю 1 ступенчатого преобразования сигнала, служит для хранения дискретного

нала Uy, Амплитудное значение линейно изменяющегося напряжения U g задается соотношением резисторов 29, 27. Второй вход суммирующего усилителя,

определяемый резистором 28, отключен t5 форму, второй блок 5 ступенчатого ключом 31,преобразования сигнала переходит в

Если признак сигнала U, имеет ну- режим работы повторителя напряжения, левой логический уровень (аналоговый Это рб еспечи6ается тем, что в режиме входной сигнал), то через элементы работы с аналоговым входным сигналом НЕ 22, ИЛИ 23 замьпсается ключ 30. Ия-2о Ug, с распределителя 4 импульсов про- тегратор 8 блокируется, что зквива- ходит сигнал и, логической едини- лентно заземлению входа через резис- тор 27 суммирующего усилителя, собранного на операционном усипителе 35

и резисторах 27 - 29. Замкнутый ключ .29 выше образом, то на выходе операци- 31 через инвертор с единичным коэф- онного усилителя 40 будет повторяться фициентом усиления, собранный на операционном усилителе 34, резисторах

значения Uj на малом промежутке времени, если входной сигнал U - дискретный, если Up имеет аналоговую

цы. Ключ 37 постоянно замкнут, и так как величина конденсатора 38 и резистора 39 выбирается описанным

напряжение U, ,

В качестве второго блока 6 срав- нения можно применить устройство 30 сравнения на операционном усилителе.

25, 26, подключает вход U, к второму входу суммирующего усилителя через резистор 28, По этому входу суммирующий усилитель имеет единичный коэффициент усиления, что обеспечивается выбором резисторов 28, 29, ОперациВ качестве второго блока 6 сра нения можно применить устройство 30 сравнения на операционном усилител

Рассмотрим работу устройства в целом с момента времени t (фиг,2 с которого входной сигнал U име

л fо f Ч f J J л Vy ,Lf . ЪлГЖ ъ нллл-лонныи усилитель 34 и резисторы-25, 26 д„скретную форму представления, В

служат для согласования полярностей напряжения. Таким образом, в режиме работы с аналоговьм сигналом на выходе интегратора 8 будет напряжение . Ug , равное входному напряжению 15-,, Первьй блок 1 ступенчатого преобразования сигнала (фиг,7) служит для преобразования входного сигнала U j в дискретный (ступенчатый) сигнал, если и g - аналоговый сигнал, и для хранения дискретного значения U g на мгшом промежутке времени, если U у - дискретный сигнал. Согласно описанному ниже алгоритму работы при дискретном и аналоговом входном сигналах на первьй блок 1 ступенчатого преобразования сигнала поступают импульсы и„ от распределителя 4 импульсов, Каждый импульс U, замыкает ключ 37, На конденсаторе 38 фиксируется значение и gx и через повторитель напряжения, собранньй на операционном усилителе 40, в течение времени между тактовыми импульсами напряжение Ц ,

10

пр

этом случае сигнал признака U нимает уровень логической единицы Согласно приведенному выше описани ; распределитель 4 импульсов формиру

40; в этом случае две последовательнос импульсов и 1, и и , , сдвинутые одн относительно другой на один такт, частотой, уменьшенной в два раза по отношению к тактовой частоте, П

45 вый блок 1 ступенчатого преобразов ния сигнала фиксирует значение вхо ного дискретного сигнала U gx по ка дому из импульсов и„ , а второй блок 5 ступенчатого преобразовани

50 сигнала фиксирует значение входно дискретного сигнала Uj. по каждому из импульсов и 1- , На выходах указа ных блоков формируются сигналы U, Uy соответственно, В первом блоке

55 сравнения происходит вычитание сиг ла и, из входного ступенчатого сиг ла и j, На выходе первого блока 2 сравнения формируется разностньй с нал и, характеризующий скорость и

, 1441346

фиксируется ,на его вькоде. Величина конденсатора 38 и резистора 39 выбирается такой, чтобы время заряда конденсатора 38 было значительно меньше периода следования тактовых импульсов U,Y наибольшей частоты.

Второй блок 5 ступенчатого преобразования сигнала, как и первый блок

значения Uj на малом промежутке времени, если входной сигнал U - дискретный, если Up имеет аналоговую

режим работы повторителя напряжения Это рб еспечи6ается тем, что в режим работы с аналоговым входным сигнало Ug, с распределителя 4 импульсов пр ходит сигнал и, логической едини-

выше образом, то на выходе операци- онного усилителя 40 будет повторять

цы. Ключ 37 постоянно замкнут, и так как величина конденсатора 38 и резистора 39 выбирается описанным

.29 выше образом, то на выходе операци- онного усилителя 40 будет повторяться

напряжение U, ,

В качестве второго блока 6 срав- нения можно применить устройство 30 сравнения на операционном усилителе.

Рассмотрим работу устройства в целом с момента времени t (фиг,2), с которого входной сигнал U имеет

f J J л Vy ,Lf . ЪлГЖ ъ нллл-лд„скретную форму представления, В

10

при- ,11

этом случае сигнал признака U нимает уровень логической единицы Согласно приведенному выше описанию ; распределитель 4 импульсов формирует

0; в этом случае две последовательности импульсов и 1, и и , , сдвинутые одна относительно другой на один такт, с частотой, уменьшенной в два раза по отношению к тактовой частоте, Пер5 вый блок 1 ступенчатого преобразова- ния сигнала фиксирует значение входного дискретного сигнала U gx по ках.-.- дому из импульсов и„ , а второй блок 5 ступенчатого преобразования

0 сигнала фиксирует значение входного дискретного сигнала Uj. по каждому из импульсов и 1- , На выходах указанных блоков формируются сигналы U, и Uy соответственно, В первом блоке 2

5 сравнения происходит вычитание сигнала и, из входного ступенчатого сигнала и j, На выходе первого блока 2 сравнения формируется разностньй сигнал и, характеризующий скорость изменения входного дискретного сигнала UB,, за время такта импульсов U , ,

На выходе второго блока 6 сранне- ния аналогичным образом получается разностный сигнал U, характеризующий скорость изменения входного сигнала за время такта и, ,

Оба разностных сигнала U и U суммируются иа втором сумматоре 7, формируя сигнал U, характеризующий скорость изменения входного дискрет кого сигнала и ex на каждом такте mi- пульсов тактовой частоты U.

Как было показано Bbnjje, интегратор 8 при дискретном входном сигнале Ug в каждом такте импульсов Ug выра батывает линейно изменяющееся напряжение Ug, скорость изменения которого; преобразования сигнала, второго блока зависит от уровня сигнала Uy. Сигнал -20 сравнений;, второго сумматора и управ- Uj поступает на первый сумматор 3, | ляемого Ш1тегратора - выгодно отли- где суммируется с входным напряжением, чает пзредлагаемое нелинейное устройство фазовой коррекц1-ш от известного, так как позволяет вносить положитель- 25 ный фазовый сдвиг выходного сигнала по отношению к входному как для аналогового, так и дискретного входного сигнала, то есть расширить диапазон корректирз тащйх сигналов.

30

. -формула изобретения

Нелриейное устройство фазовой коррекции по авт. ев, 767700, о т л и-:

чающееся тем что, с целью

Ugx . В результате ка выходе сумматора 3 будет сформирован выходной сигнал: и. Поскольку сигнал Ug на каждом такте Ug несет информацию о скорости изменения входного дискретного сигнала Ug то выходной дискретный сигнал UjCU gy) нелинейного устройства фазовой коррекции будет иметь положительный фазовый сдвиг по отношению к входному дискретному сигналу

UBX. . .

Рассмотрим теперь работу устройства для аналоговой формы входного сигнала .З). Пусть с некоторого моме нта времени t 5 сигнал Ugj становится аналоговым. В этом случае сигнал признака U to принимает уровень логического нуля,

35

расширения диапазона сигналов, корректируемых устройством, в нем дополнительно .установлены распределитель импульсов, второй блок ступенчатого

ному вьше принципу работы распределителя 4 импульсов последний формирует в этом режиме на выходе U i, i-ш пульсы с частотой, равной тактовой

Согласно описан- преобразования сигнала, второй блок

сравнения сигнала второй сумматор и интегратор9 причем выход первого блока сравнения подключен к первому входу первого сзпуматора через после- частоте, а на выходе U вырабатыва- довательно соединенные второй сумма-,

тор и интеграто), тактовый вход и

ется уровень логической единицы,

Тактовые импульсы U,, поступают на первый блок 1 ступ енчатого преобразования сигнала, которьй работает в этом режиме, как в прототипе. Уровень логической единицы U, переводит второй блок 5 ступенчатого преобразования сигнала в режим повторителя напряжения , В результате на оба входа второго блока б сравнения поступают одинаковые напряжения него выходной сигнал и равен нулю. Вы- Гходной сигнал l} второго сумматора 7 в этом случае равен входному сиг

50

55

вход признак входного сигнала устройства подключены соответственно к первому и второму управляющим входам интегратора и -к первому и второму входам распределителя импульсов, соединенного первым входом с вторым входом первого блока ступенчатого преобразователя сигнала, а вторым выходом - с первым входом второго блока ступенчатого преобразователя сигнала, выходом подключенного к первому входу второго блока сравнения, а вторым входом - к входу анализатоналу и, которьпй вырабатывается как разностный сигнал между и. и U в первом блоке 2 сравнения. Интегратор 8 в стгучае, когда сигнал U. признака равен логическому нулю, переходит в повторителя, как было показано в описании работы интегратора 8. Выходной сигнал его Uj в этом случае равен входном-у U или, что то же самое, Uj. В результате на первом сумматоре происходит суммирование сигна

лов U2 и входного сигнала U

8х

как

в нелинейном устройстве-прототипе 15 фазовой коррекции.

Таким образом, использование новых элементов - распределителя импульсов, второго блока ступенчатого

чающееся тем что, с целью

35

расширения диапазона сигналов, корректируемых устройством, в нем дополнительно .установлены распределитель импульсов, второй блок ступенчатого

преобразования сигнала, второй блок

0

5

вход признак входного сигнала устройства подключены соответственно к первому и второму управляющим входам интегратора и -к первому и второму входам распределителя импульсов, соединенного первым входом с вторым входом первого блока ступенчатого преобразователя сигнала, а вторым выходом - с первым входом второго блока ступенчатого преобразователя сигнала, выходом подключенного к первому входу второго блока сравнения, а вторым входом - к входу анализато714413468

pa входного сигнала, к первому входу второго, блока сравнения, соединенно-,

первого блока ступенчатого преобра- зовани сигнала и к второму входу

го выходом с вторым входом второго сумматора.i

d UsJanm

9

Фиг.1

А

1ППППППППППППП,

о,,

rfn п п п п п п

А п п п п

ч

t t

4

//,

ил

gj

U го выходом с вторым входом второго сумматора.i

7

t t

.-T-XL

Фиг.2

Ugl

пппппппппппппп

и.

ю

пппппппппппппп

и

Фиг.з

V-.-v

U.gi

пппппппппппп

U.

n П П П

(i8 U.ig

Ufi

rLfl П ППППИЛ

П П П г

ППППП

Фие. 7

| Нелинейное устройство фазовой коррекции | 1978 |

|

SU767700A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-11-30—Публикация

1987-06-19—Подача