J%

4iik 4

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ ТАБЛИЧНО-АЛГОРИТМИЧЕСКИМ МЕТОДОМ | 1996 |

|

RU2136041C1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1361547A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Цифровой генератор гармонических функций | 1983 |

|

SU1156044A1 |

| Устройство для вычисления синуса и косинуса угла табличным методом | 1986 |

|

SU1348830A1 |

| Устройство для вычисления функций синуса и косинуса | 1980 |

|

SU922734A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1339554A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Функциональный преобразователь | 1988 |

|

SU1541629A1 |

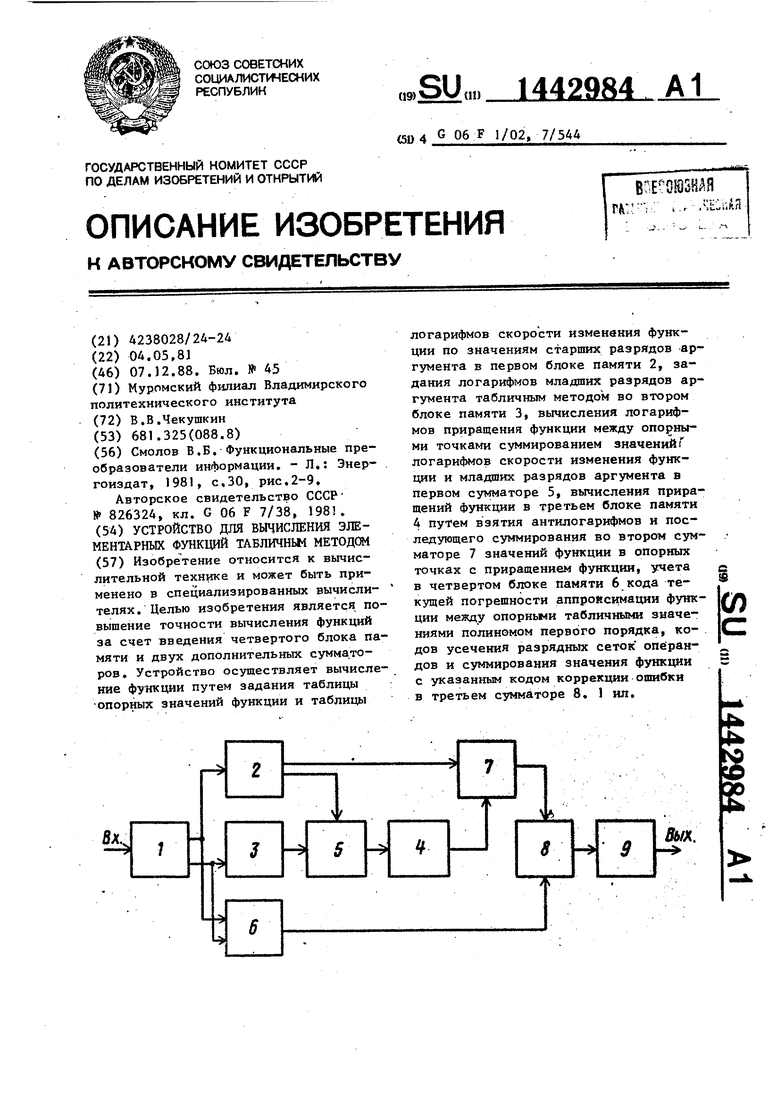

Изобретение относится к вычислительной и может быть применено в специализированных вычислителях. Целью изобретения является повышение точности вычисления функций за счет введения четвертого блока памяти и двух дополнительных сумматоров. Устройство осуществляет вычисление функции путем задания таблицы опорных значений функции и таблицы логарифмов скорости изменения функции по значениям старших разрядов аргумента в первом блоке памяти 2, задания логарифмов младших разрядов аргумента табличным методом во втором блоке памяти 3, вычисления логарифмов приращения функции между опорными точками суммированием значеиийГ логари( скорости изменения функции и младших разрядов аргумента в первом сумматоре 5, вычисления приращений функции в третьем блоке памяти 4 путем взятия антилогарифмов и последующего суммирования во втором сумматоре 7 значений функции в опорных точках с приращением функции, учета в четвертом блоке памяти 6 кода текущей погрешности аппроксимации функции между опорньми табличными значениями полиномом первого порядка, кодов усечения разрядных сеток операндов и суммирования значения функции с указанным кодом коррекции ошибки в третьем сумматоре 8. 1 ил. i (Л

ex

8

Вых.

Изобретение относится к вычислительной технике и может быть применено в специализированных вычислителях .

На чертеже представлена блок-схема предлагаемого устройства.

Целью изобретения является повы- шение точности.

Устройство содержит регистр 1 ар- гумента, первь й 2,.второй 3 и третий 4 блоки памяти, первый.сумматор 5, четвертый блок 6 памяти, второй 7 и третий 8 сумматоры и регистр 9 функ

.дни.

Устройство работает следующим образом.

Входной параллельный код угла fJ с регистра J аргумента разбивается на группы старших и младших /лц разрядов. Все старшие разряды кода подаются на вход первого блока 2 памяти, а на первый вход четвертого блока 6 памяти подаются лишь несколько старших разрядов. На втором выхо- де первого блока/2 памяти формируется код функции sin Р; в опорных точках J. Код функции задается в таблице с симметричным округлением. Таким образом, точность зада- ния функции sin jb в опорных точках

.--1/2-2 - .

На первом выходе первого блока 2 памяти формируется логарифм скорости изменения функции в опорных точка.х 1пК-. Таблица значений логарифма строится с учетом полученньгх значений погрешностей функции sinp;.

Таким образом, эти погрешности в значительной степени компенсируют в конечном счете друг друга,

На вход второго блока 3 памяти подаются все младшие разряды кода р Блок 3 памяти осуществляет вычисление логарифма аргумента с г дополнительными разрядами. На выходе первого сумматора 5 имеют логарифм приращения функции. Этот логарифм трети блок 4 памяти переводит в действительное приращение Функции также с г дополнительными разрядами. Непосредственно этот блок дает ошибку 1 ( 2

ходе второго сумматора 7 имеют значение функции sin fi с г дсшолнитель- ными разрядами. Значение погрешности

2 в приращении функции. На вы

аппроксимации функции полиномом первого порядка определяется следующим выражением:

(3з) (.) (i-pj) (p-|ij )-sin|i,

(I)

где j - номер опорной точки.

С учетом пересчета в радианную меру угла максимальное значение ошибки аппроксимации . « 1Г(

А - ..iA«.«.

макс 32

Четвертый блок 6 памяти осуществляет приближенное формирование суммарного кода коррекции ошибки аппроксимации в соответствии с (1) и кода коррекции ошибки урезания г дополнительных разрядов в третьем сумматоре 8, Значение последней ошибки постоянно и равно 1/2 « 2 . В четвертом блоке 6 памяти производится анализ значений только первых разрядов

кодов . и РМЛ

Третий сумматор 8 осуществляет суммирование значения функции с г дополнительными разрядами и значения кода коррекции ошибки.

Результирующая ошибка вычисления функции

1/2-2- ,5li5. Формула иэобре. тения.

Q

t

0

5

Устройство для вычисления элементарных функций табличным методом, содержащее регистр аргумента, три блока памяти, первый сумматор и регистр функции, причем вход аргумента устройства соединен с информационными входами регистра аргумента,, выходы старших и младших разрядов которого соединены с адресньми входами соответственно первого и второго блоков памяти, первь й выход первого и выход второго блбков памяти соединены с входами соответственно первого и второго слагаемых первого сумматора, выход которого соединен с адресным .входом третьего блока памяти, отличающееся тем# что, с целью повышения точности, в него дополнительно введены второй и третий сумматоры и четвертый блок памяти, причём вьисоды младших разрядов регистра аргумента соединены с первой

14Д2984

группой адресных входов четвертогоматора, выход которого Ьоединен с блока памяти, вторая группа адресныхвходом первого слагаемого третьего входов которого соединена с выходамисумматора, вход второго слагаемого соответствующих старших разрядов ре- которого соединен с выходом четверто- гистра аргумента, второй выход пер-го блока памяти, выход которого соевого блока памяти и выход третьегодинен с информационными входами ре- блока памяти соединены с входами пер-гистра функции, выход которого яв- вого и второго слагаемых второго сум-ляется выходом результата устройства.

| Смолов В.Б | |||

| Функциональные преобразователи информации, - Л,: Энер- гоиздат, 1981, с,30, рис.2-9 | |||

| 1979 |

|

SU826324A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-07—Публикация

1981-05-04—Подача