113

Изобретение относится к вычисли- тельной технике и может быть использовано в специализированных вычислителях, ориентированных на табличную обработку информации.

Цель изобретения - упрощение преобразователя и повьшёние его быстродействия.

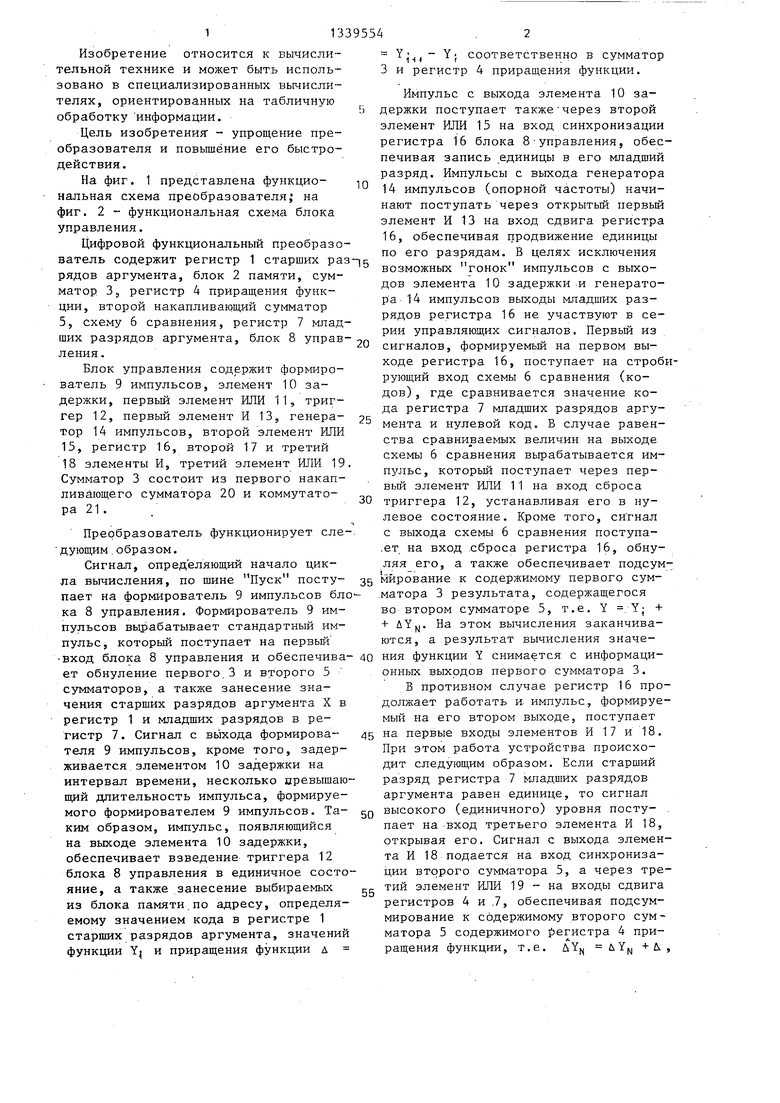

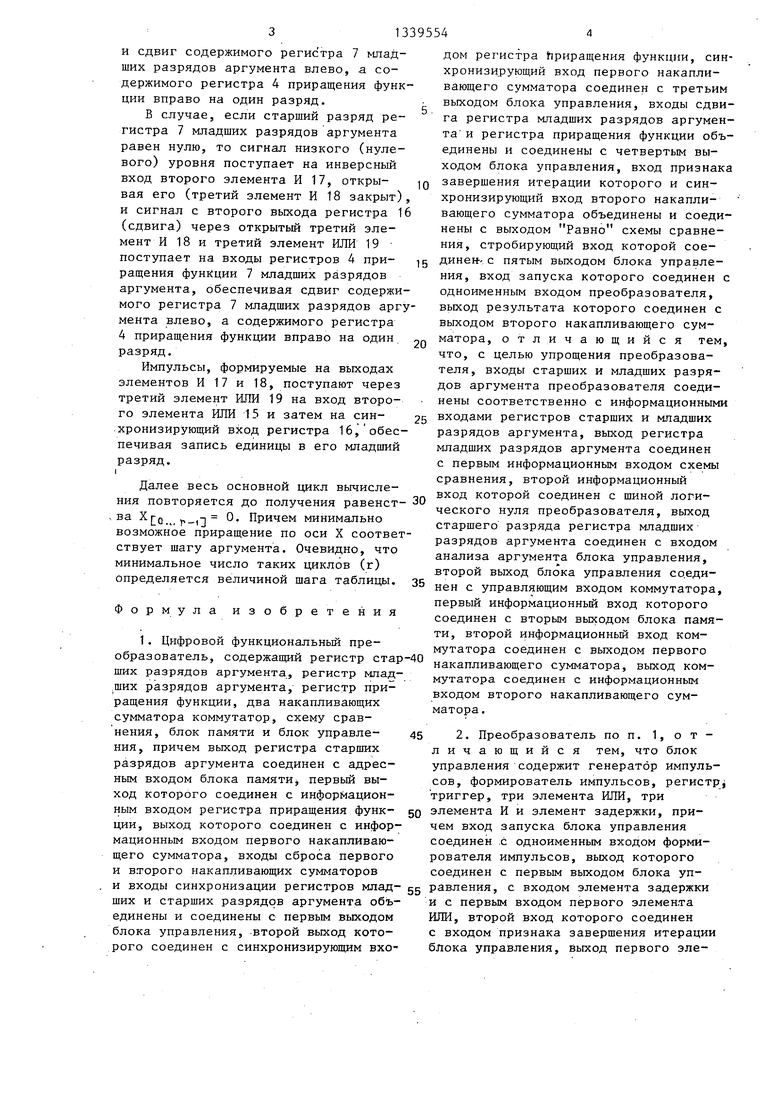

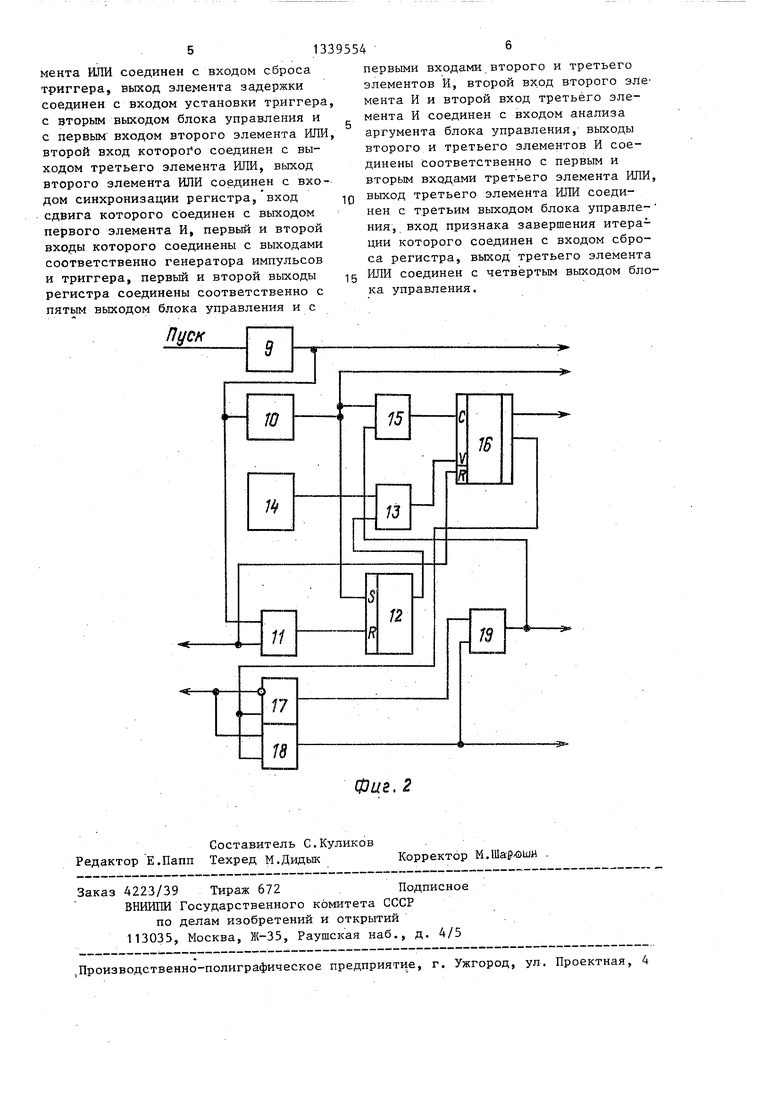

На фиг. 1 представлена функцио- нальная схема преобразователя; на фиг. 2 - функциональная схема блока управления.

Цифровой функциональный преобразователь содержит регистр 1 старших pas рядов аргумента, блок 2 памяти, сумматор 3

э регистр 4 приращения функции, второй накапливающий сумматор 5, схему 6 сравнения, регистр 7 младших разрядов аргумента, блок 8 управ- ления.

Блок управления содержит формирователь 9 импульсов, элемент 10 задержки, первый элемент ИЛИ 11, триггер 12, первый элемент И 13, генератор 14 импульсов, второй элемент ИЛИ 15, регистр 16, второй 17 и третий 18 элементы И, третий элемент ИЛИ 19 Сумматор 3 состоит из первого накапливающего сумматора 20 и коммутатора 21 .

Импульс с выхода элемента 10 задержки поступает также через второй элемент ИЛИ 15 на вход синхронизации регистра 16 блока 8управления, обеспечивая запись .единицы в его младший разряд. Импульсы с выхода генератора 14 импульсов (опорной частоты) начинают поступать через открытый первьй элемент И 13 на вход сдвига регистра 16, обеспечивая продвижение единицы по его разрядам. В целях исключения возможных гонок импульсов с выходов элемента 10 задержки-и генератора 14 импульсов выходы младших разрядов регистра 16 не участвуют в серии управляющих сигналов. Первый из сигналов, формируемый на первом выходе регистра 16, поступает на строби рующий вход схемы 6 сравнения (кодов) , где сравнивается значение кода регистра 7 младших разрядов аргумента и нулевой код. В случае равенства сравниваемых величин на выходе схемы 6 сравнения вырабатывается им- пз льс, который поступает через первый элемент ИЛИ 11 на вход сброса триггера 12, устанавливая его в нулевое состояние. Кроме того, сигнал с выхода схемы 6 сравнения поступа- .ет на вход сброса регистра 16, обнуляя его, а также обеспечивает подсумПреобразователь функционирует сле- дующим,образом.

Сигнал, определяющий начало цикла вычисления, по шине Пуск посту- 35 мйрование к содержимому первого сум- пает на фop шpoвaтeль 9 импульсов бло .матора 3 результата, содержащегося ка 8 управления. Формирователь 9 им- во втором сумматоре 5, т.е. Y . YJ + пульсов вырабатывает стандартный им- + АУц. На этом вычисления заканчива- пульс, которьш поступает на первый ются, а результат вычисления значе- вход блока 8 управления и обеспечива- 40 ния функции Y снимается с информациет обнуление первого,3 и второго 5 сумматоров, а также занесение знаВ противном случае регистр 16 продолжает работать и импульс, формируемый на его втором выходе, поступает 45 на первые входы элементов И 17 и 18. Лри этом работа устройства происходит следующим образом. Если старший разряд регистра 7 младших разрядов аргумента равен единице, то сигнал

чения старших разрядов аргумента X в регистр 1 и младших разрядов в регистр 7. Сигнал с вьЬсода формирователя 9 импульсов, кроме того, задерживается элементом 10 задержки на интервал времени, несколько оревышаю- щий длительность импульса, формируемого формирователем 9 импульсов. Та- 50 высокого (единичного) уровня посту- ким образом, импульс, появляющийся лает на вход третьего элемента И 18,

открывая его. Сигнал с выхода элемента И 18 подается на вход синхронизации второго сумматора 5, а через третий элемент ИЛИ 19 - на входы сдвига регистров 4 и .7, обеспечивая подсум- мирование к содержимому второго сумматора 5 содержимого регистра 4 прина выходе элемента 10 задержки, обеспечивает взведение триггера 12 блока 8 управления в единичное состояние, а также занесение выбираемых из блока памяти по адресу, определяемому значением кода в регистре 1 старших разрядов аргумента, значений функции Y и приращения функции д

55

ращения функции, т.е.

UY bY,

+ i

- YI соответственно в сумматор 3 и регистр 4 приращения функции.

Импульс с выхода элемента 10 задержки поступает также через второй элемент ИЛИ 15 на вход синхронизации регистра 16 блока 8управления, обеспечивая запись .единицы в его младший разряд. Импульсы с выхода генератора 14 импульсов (опорной частоты) начинают поступать через открытый первьй элемент И 13 на вход сдвига регистра 16, обеспечивая продвижение единицы по его разрядам. В целях исключения возможных гонок импульсов с выходов элемента 10 задержки-и генератора 14 импульсов выходы младших разрядов регистра 16 не участвуют в серии управляющих сигналов. Первый из сигналов, формируемый на первом выходе регистра 16, поступает на строби- рующий вход схемы 6 сравнения (кодов) , где сравнивается значение кода регистра 7 младших разрядов аргумента и нулевой код. В случае равенства сравниваемых величин на выходе схемы 6 сравнения вырабатывается им- пз льс, который поступает через первый элемент ИЛИ 11 на вход сброса триггера 12, устанавливая его в нулевое состояние. Кроме того, сигнал с выхода схемы 6 сравнения поступа- .ет на вход сброса регистра 16, обнуляя его, а также обеспечивает подсуммйрование к содержимому первого сум- .матора 3 результата, содержащегося во втором сумматоре 5, т.е. Y . YJ + + АУц. На этом вычисления заканчива- ются, а результат вычисления значе- ния функции Y снимается с информационных выходов первого сумматора 3.

В противном случае регистр 16 продолжает работать и импульс, формируемый на его втором выходе, поступает на первые входы элементов И 17 и 18. Лри этом работа устройства происходит следующим образом. Если старший разряд регистра 7 младших разрядов аргумента равен единице, то сигнал

высокого (единичного) уровня посту- лает на вход третьего элемента И 18,

ращения функции, т.е.

UY bY,

+ i

и сдвиг содержимого регис тра 7 младших разрядов аргумента влево, а содержимого регистра 4 приращения функции вправо на один разряд.

В случае, если старший разряд регистра 7 младших разрядов аргумента равен нулю, то сигнал низкого (нулевого) уровня поступает на инверсный вход второго элемента И 17, откры- вая его (третий элемент И 18 закрыт) и сигнал с второго выхода регистра 1 (сдвига) через открытый третий элемент И 18 и третий элемент ИЛИ 19 поступает на входы регистров 4 при- ращения функции 7 младших разрядов аргумента, обеспечивая сдвиг содержимого регистра 7 младших разрядов аргмента влево, а содержимого регистра 4 приращения функции вправо на один разряд.

Импульсы, формируемые на выходах элементов И 17 и 18, поступают через третий элемент ИЛИ 19 на вход второго элемента ИЛИ 15 и затем на син- хронизирующий вход регистра 16, обеспечивая запись единицы в его младший

разряд.

I

Далее весь основной цикл вычисления повторяется до получения равенст- , ва 0.., f,,- О- Причем минимально возможное приращение по оси X соответствует шагу аргумента. Очевидно, что минимальное число таких циклов (г) определяется величиной шага таблицы.

Формула изобретения

1. Цифровой функциональный преобразователь, содержащий регистр стар шик разрядов аргумента, регистр млад- ,ших разрядов аргумента, регистр приращения функции, два накапливающих сумматора коммутатор, схему сравнения, блок памяти и блок управле- ния, причем выход регистра старших разрядов аргумента соединен с адресным входом блока памяти первый выход которого соединен с информационным входом регистра приращения функ- ции, выход которого соединен с инфор- мационньм входом первого накапливающего сумматора, входы сброса первого и второго накапливающих сумматоров и входы синхронизации регистров млад- ших и старших разрядов аргумента объединены и соединены с первым выходом блока управления, второй выход которого соединен с синхронизирующим вхо0

Q g

5

0 5

0 5

дом регистра Ьриращения функции, синхронизирующий вход первого накапливающего сумматора соединен с третьим выходом блока управления, входы сдвига регистра младших разрядов аргумента и регистра приращения функции объединены и соединены с четвертым выходом блока управления, вход признака завершения итерации которого и синхронизирующий вход второго накапливающего сумматора объединены и соединены с выходом Равно схемы сравнения, стробирующий вход которой соединен-- с пятым выходом блока управления, вход запуска которого соединен с одноименным входом преобразователя, выход результата которого соединен с выходом второго накапливающего сумматора, отличающийся тем, что, с целью упрощения преобразователя, входы старших и младших разрядов аргумента преобразователя соединены соответственно с информационными входами регистров старших и младших разрядов аргумента, выход регистра младших разрядов аргумента соединен с первым информационным входом схемы сравнения, второй информационный вход которой соединен с шиной логического нуля преобразователя, выход старшего разряда регистра младших разрядов аргумента соединен с входом анализа аргумента блока управления, второй выход блока управления со.еди- нен с управляющим входом коммутатора, первый информационньй вход которого соединен с вторым выходом блока памяти, второй информационный вход коммутатора соединен с выходом первого накапливающего сумматора, выход коммутатора соединен с информационным входом второго накапливающего сумматора.

2. Лреобразователь по п. 1, отличающийся тем, что блок управления содержит генератор импульсов, формирователь импульсов, регистру триггер, три элемента ИЛИ, три элемента И и элемент задержки, причем вход запуска блока управления соединен с одноименным входом формирователя импульсов, выход которого соединен с первым выходом блока управления, с входом элемента задержки и с первым входом первого элемента ИЛИ, второй вход которого соединен с входом признака завершения итерации блока управления, выход первого эле5133

мента ИЛИ соединен с входом сброса триггера, выход элемента задержки соединен с входом установки триггера, с вторым выходом блока управления и с первым входом второго элемента ИЛИ, второй вход которог о соединен с выходом третьего элемента ИЛИ, выход второго элемента ИЛИ соединен с входом синхронизации регистра, вход сдвига которого соединен с выходом первого элемента И, первый и второй входы которого соединены с выходами соответственно генератора импульсов и триггера, первьй и второй выходы регистра соединены соответственно с пятым выходом блока управления и с

первыми входами второго и третьего элементов И, второй вход второго эЛе мента И и второй вход третьего элемента И соединен с входом анализа аргумента блока управления, выходы второго и третьего элементов И соединены соответственно с первым и вторым вхсщами третьего элемента ИЛИ, выход третьего элемента ИЛИ соединен с третьим выходом блока управле- ния, вход признака завершения итерации которого соединен с входом сброса регистра, вькод третьего элемента ИЛИ соединен с четвёртым выходом блока управления.

flycff

Составитель С.Куликов Редактор Е.Папп Техред М.ДидыкКорректор М.Шархэши

.,«.«...«.-,«.,e.i.e.--.-.- в--.--.«---.-----«-- ------------ « - ---- --- :--- - -

Заказ 4223/39 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Раушская наб., д. 4/5

.Производственно-полиграфическое предприяти е, г. Ужгород, ул. Проектная, 4

фц2, 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1988 |

|

SU1541629A1 |

| Функциональный преобразователь | 1985 |

|

SU1251103A1 |

| Функциональный преобразователь | 1991 |

|

SU1807498A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1273944A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Устройство для извлечения квадратного корня | 1988 |

|

SU1569827A1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1188750A1 |

| Вычислитель функций синуса и косинуса | 1976 |

|

SU628491A1 |

Изобретение относится к области вычислительной техники и может быть использовано в специализированных вычислителях, ориентированных на табличную обработку информации. Целью изобретения является упрГощение преобразователя и повышение его быстродействия. Цифровой функциональный преобразователь содержит регистр 1 старших рязрядов аргумента, блок 2 памяти, первый накапливающий сумматор 3, регистр 4 приращения функции, второй накапливающий сумматор 5, схему 6 сравнения, регистр 7 младщих разрядов аргумента, блок 8 управления. Процесс вычисления основан на табличном способе вычисления. Опорное значение функции выбирается на основе старших разрядов аргумента, а с приращение - на основе младших разрядов. 1 з.п.ф-лы, 2 ил. СЛ ,0 00 00 ;О сл ел

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Функциональный преобразователь | 1985 |

|

SU1251103A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-23—Публикация

1986-04-16—Подача