4

о со о со

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля полупроводниковой памяти.

Целью изобретения является повышение достоверности контроля.

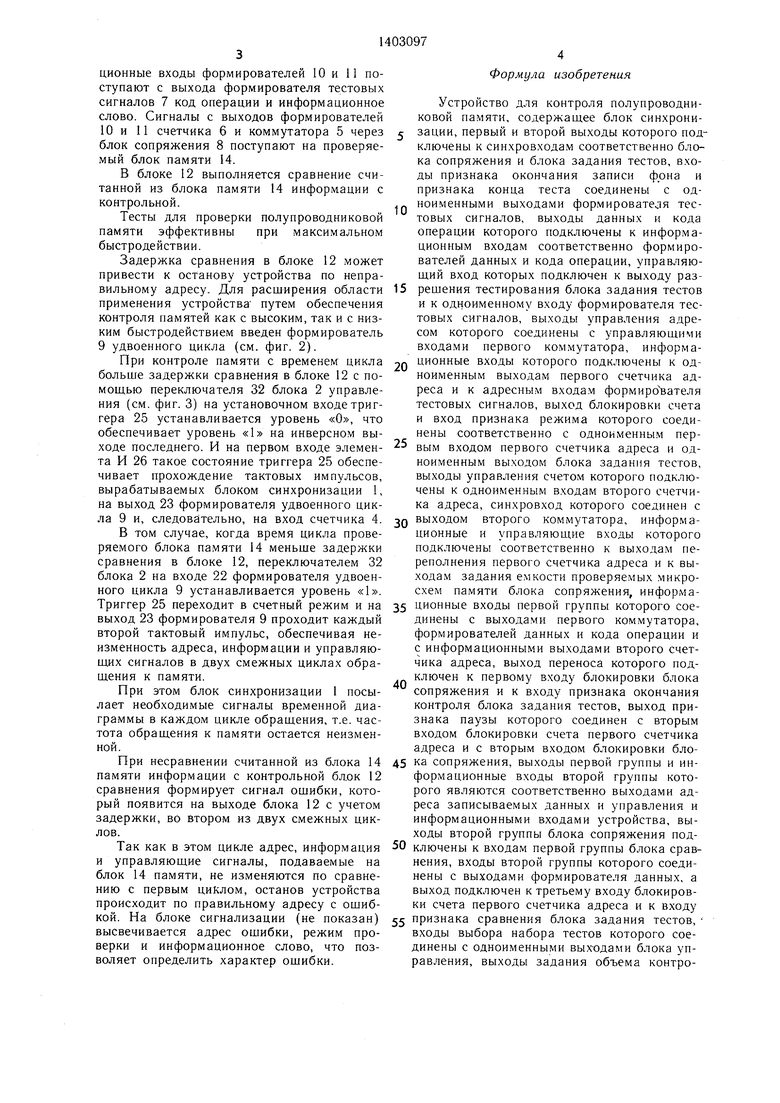

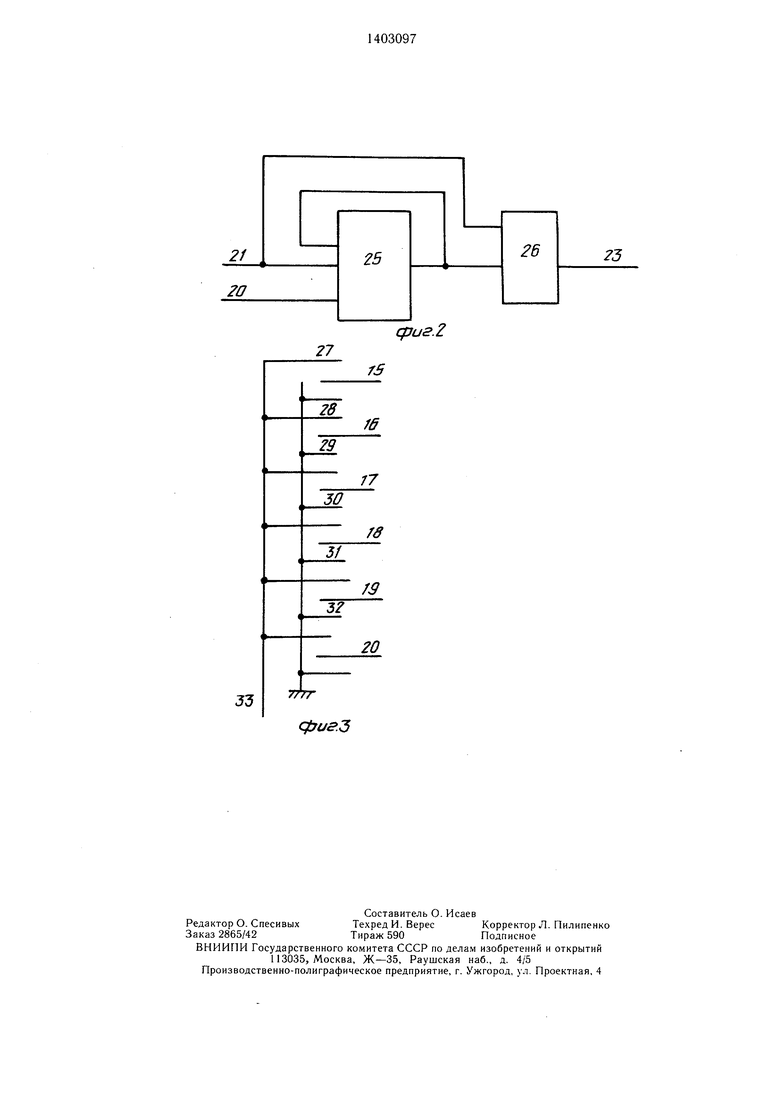

На фиг. 1 представлена структурная схема устройства для контроля полупроводниковой памяти; на фиг. 2 - схема формирователя удвоенного цикла; на фиг. 3 - схема блока управления.

Устройство (фиг. 1) содержит блок синхронизации 1, блок 2 управления, блок 3 задания тестов, первый счетчик 4 адреса, первый коммутатор 5, второй счетчик 6 адноса, соответствующие емкости применяемых в блоке 14 микросхем памяти.

Управление счетчиком 6 осуществляется через коммутатор 13, на информационные входы которого поступают сигналы переносов с выходов счетчика 4, а на управляющий вход - сигналы с выхода блока 8 сопряжения, которые разрешают передачу сигнала переноса на выход коммутатора 13.

По выходам 17, 18 блока 2 управления 10 задается объем проверяемой памяти путем исключения части разрядов счетчика 6.

При исключении из счетного режима всех разрядов счетчика 6 обращение осуществляется к одной микросхеме памяти, опререса, формирователь 7 тестовых сигналов, j деляемой состоянием выходов 17, 18 бло- блок 8 сопряжения, формирователь 9 удво-ка 2.

По четвертому и пятому входам задается режим работы счетчика 6 в зависимости от формируемого теста.

При заполнении счетчика 6 вырабатываполупроводниковой памяти, выходы 15-20 20 ется сигнал переноса, который поступает блока управления 2, входы 21, 22 и выход на четвертый вход блока 3 задания тестов,

где участвует в формировании сигнала «Конец проверки.

По выходу 19 блока 2 задается необходи- 25 мый набор тестов для проверки блока 14. Сигнал с четвертого выхода блока задания тестов, поступая на вход формирователя тестовых сигналов 7 и управляющие входы формирователей 10, 11, разрешает формирование тестовых последовательностей выУстройство работает следующим обра- 30 бранного теста. По сигналу «Конец зом.теста, поступающему с выхода формироваПри включении питания устанавливаются в исходное нулевое состояние счетчики 4 и 6, блок 3 задания тестов, формирователь 7 тестовых сигналов, блок 12 сравнения и триггер 25 (на инверсном выходе устанавливается уровень «1) блока 2 управления. По выходу 15 блока 2 устанавливается: частота обращения к проверяемому блоку 14 памяти, по выходу 17 и 18 - объем проверяемого устройства, по выходу 19, 20 - режим 40 записи в память фоновой информации. Для проверки.этого по сигналу «Конец теста блок 3 заПо сигналу «Пуск с выхода 16 блока 2 дания тестов разрещает запись фона. Сиг- управления включается блок синхрониза-нал переноса на пятом входе блока 3 пере- ции 1, по выходу которого поступает счет- водит последний в состояние, соответствую- ный сигнал с периодом равным циклу обра- дг щее разрешению выполнения собственно

ениого цикла, формирователь данных 10, формирователь кода операции И, блок 12 сравнения, второй коммутатор 13. На фиг. 1 также показаны контролируемый блок 14

23 формирователя удвоенного цикла 9, выходы 24 блока 8 сопряжения. Формирователь 9 удвоенного цикла (фиг. 2) содержит триггер 25 и элемент И 26.

Блок 2 управления (фиг. 3) содержит переключатели 27-32, выходы подвижных контактов которых являются выходами 15- 20 блока 2 управления. Вход 33 предназначен для подключения к уровню «1.

35

теля тестовых сигналов 7, блок 3 задания тестов разрешает формирование следуюше- го выбранного теста. Сигнал с пятого выхода блока 3 задания тестов блокирует прохождение счетного сигнала на входе счетчика 4 и обращение к блоку памяти 14 на входе блока 8 сопряжения на время поиска очередного выбранного теста.

Выполнение каждого теста начинается с

тестовой ггрограммы.

щения.

Проверяемый полупроводниковый блок памяти 14 может быть выполнен на микросхемах различной емкости. В связи с этим адрес блока памяти 14 формируется

тестовой ггрограммы.

На управляющие входы коммутатора 5 поступают сигналы с выхода формирователя тестовых сигналов 7, причем в зависимости от алгоритма выполняемого теста продвумя счетчиками: 4, формирующим адрес 50 ходит прямой или инверсный адрес, посту- микросхем, и 6, определяющим номер мик-пающий на информационные входы коммутатора 5 с первого выхода счетчика 4, либо

росхемы. Причем разрядность счетчика 4 определяется максимальной емкостью микросхем памяти, а счетчика 6 - емкостью проверяемой памяти. Счетчик 4 изменяет свое состояние по счетному сигналу, поступающему с выхода 23 формирователя 9 удвоенного цикла, от нулевого до максимального, вырабатывая при этом сигналы пере55

фоновый или тестовый адрес, поступающий на входы коммутатора 5 с выхода формирователя тестовых сигналов 7.

В зависимости от алгоритма выполнения теста с выхода формирователя тестовых сигналов 7 поступает сигнал, блокирующий счетный сигнал в счетчике 4. На информаранного теста. По сигналу «Конец теста, поступающему с выхода формировазаписи в память фоновой информации. Для этого по сигналу «Конец теста блок 3 за

теля тестовых сигналов 7, блок 3 задания тестов разрешает формирование следуюше- го выбранного теста. Сигнал с пятого выхода блока 3 задания тестов блокирует прохождение счетного сигнала на входе счетчика 4 и обращение к блоку памяти 14 на входе блока 8 сопряжения на время поиска очередного выбранного теста.

Выполнение каждого теста начинается с

дания тестов разрещает запись фона. Сиг- нал переноса на пятом входе блока 3 пере- водит последний в состояние, соответствую- щее разрешению выполнения собственно

тестовой ггрограммы.

На управляющие входы коммутатора 5 поступают сигналы с выхода формирователя тестовых сигналов 7, причем в зависимости от алгоритма выполняемого теста про

фоновый или тестовый адрес, поступающий на входы коммутатора 5 с выхода формирователя тестовых сигналов 7.

В зависимости от алгоритма выполнения теста с выхода формирователя тестовых сигналов 7 поступает сигнал, блокирующий счетный сигнал в счетчике 4. На информационные входы формирователей 10 и 11 поступают с выхода формирователя тестовых сигналов 7 код операции и информационное слово. Сигналы с выходов формирователей 10 и II счетчика 6 и коммутатора 5 через блок сопряжения 8 поступают на проверяемый блок памяти 14.

В блоке 12 выполняется сравнение считанной из блока памяти 14 информации с контрольной.

Тесты для проверки полупроводниковой памяти эффективны при максимальном быстродействии.

Задержка сравнения в блоке 12 может привести к останову устройства по неправильному адресу. Для расширения области применения устройства путем обеспечения контроля памятей как с высоким, так и с низким быстродействием введен формирователь 9 удвоенного цикла (см. фиг. 2).

При контроле памяти с временем цикла больше задержки сравнения в блоке 12 с по- мош,ью переключателя 32 блока 2 управления (см. фиг. 3) на установочном входе триггера 25 устанавливается уровень «О, что обеспечивает уровень «1 на инверсном выходе последнего. И на первом входе элемента И 26 такое состояние триггера 25 обеспечивает прохождение тактовых импульсов, вырабатываемых блоком синхронизации 1, на выход 23 формирователя удвоенного цикла 9 и, следовательно, на вход счетчика 4.

В том случае, когда время цикла проверяемого блока памяти 14 меньше задержки сравнения в блоке 12, переключателем 32 блока 2 на входе 22 формирователя удвоенного цикла 9 устанавливается уровень «1. Триггер 25 переходит в счетный режим и на выход 23 формирователя 9 проходит каждый второй тактовый импульс, обеспечивая неизменность адреса, информации и управляющих сигналов в двух смежных циклах обращения к памяти.

При этом блок синхронизации 1 посылает необходимые сигналы временной диаграммы в каждом цикле обращения, т.е. частота обращения к памяти остается неизменной.

При несравнении считанной из блока 14 памяти информации с контрольной блок 12 сравнения формирует сигнал ощибки, который появится на выходе блока 12 с учетом задержки, во втором из двух смежных циклов.

Так как в этом цикле адрес, информация и управляющие сигналы, подаваемые на блок 14 памяти, не изменяются по сравнению с первым циклом, останов устройства происходит по правильному адресу с ощиб- кой. На блоке сигнализации (не показан) высвечивается адрес ошибки, режим проверки и информационное слово, что позволяет определить характер ошибки.

0

5

0

5

0

5

0

5

0

5

Формула изобретения

Устройство для контроля полупроводниковой памяти, содержащее блок синхронизации, первый и второй выходы которого подключены к синхровходам соответственно блока сопряжения и блока задания тестов, входы признака окончания записи фона и признака конца теста соединены с одноименными выходами формировате ля тестовых сигналов, выходы данных и кода операции которого подключены к информационным входам соответственно формирователей данных и кода операции, управляющий вход которых подключен к выходу разрешения тестирования блока задания тестов и к одноименному входу формирователя тестовых сигналов, выходы управления адресом которого соединены с управляющими входа.ми первого коммутатора, информационные входы которого подключены к одноименным выходам первого счетчика адреса и к адресным входам формиро вателя тестовых сигналов, выход блокировки счета и вход признака режима которого соединены соответственно с одноименным первым входом первого счетчика адреса и одноименным выходом блока задания тестов, выходы управления счетом которого подключены к одноименным входам второго счетчика адреса, синхровход которого соединен с выходом второго коммутатора, информационные и управляющие входы которого подключены соответственно к выходам переполнения первого счетчика адреса и к выходам задания емкости проверяемых микросхем па.мяти блока сопряжения, информационные входы первой группы которого соединены с выходами первого коммутатора, формирователей данных и кода операции и с информационными выходами второго счетчика адреса, выход переноса которого подключен к первому входу блокировки блока сопряжения и к входу признака окончания контроля блока задания тестов, выход признака паузы которого соединен с вторым входом блокировки счета первого счетчика адреса и с вторым входом блокировки блока сопряжения, выходы первой группы и информационные входы второй группы которого являются соответственно выходами адреса записываемых данных и управления н информационными входами устройства, выходы второй группы блока сопряжения подключены к входам первой группы блока сравнения, входы второй группы которого соединены с выходами формирователя данных, а выход подключен к третьему входу блокировки счета первого счетчика адреса и к входу признака сравнения блока задания тестов, входы выбора набора тестов которого соединены с одноименными выходами блока управления, выходы задания объема контролируемой памяти которого подключены к установочным входам второго счетчика адреса, выход пуска и синхровыход блока управления соединены с одноименными входами блока синхронизации, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введен формирователь удвоенного цикла, синхровход и выход которого подключены соответственно к второму синхровыходу блока синхронизации и синхровходу первого счетчика адреса, управляющий вход формирователя удвоенного цикла соединен с выходом управления длительностью цикла блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1051585A1 |

| Устройство для контроля памяти | 1982 |

|

SU1061174A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля блоков памяти | 1991 |

|

SU1833920A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для тестового контроля блоков памяти | 1988 |

|

SU1541678A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля полупроводниковой памяти. Целью изобретения является повышение достоверности контроля. Устройство содержит блок синхронизации, блок управления, блок задания тестов, первый и второй счетчики адреса, первый и второй коммутаторы, формирователь тестовых сигналов, блок сопряжения, формирователь удвоенного цикла, формирователи данных и кода операции, блок сравнения. Повышение достоверности контроля достигается за счет исключения останова по неверному адресу при контроле памяти, время цикла которой меньше времени задержки в блоке сравнения. 3 ил.

дуие

21

28

53

777Г

фие.:5

25

25

23

ери г. 2

f6

| Устройство для контроля полупроводниковой оперативной памяти | 1982 |

|

SU1051586A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1051585A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1988-06-15—Публикация

1986-07-28—Подача