4s

Фиг.1

Изобретение относится к вычисли- ;. тельной технике, а точнее к запоминающим устройствам с коррекцией ошибок, и может быть использовано при создании устройств памяти в интегральном исполнении.

Целью изобретения является повы- шение надежности запоминающего устройства.10

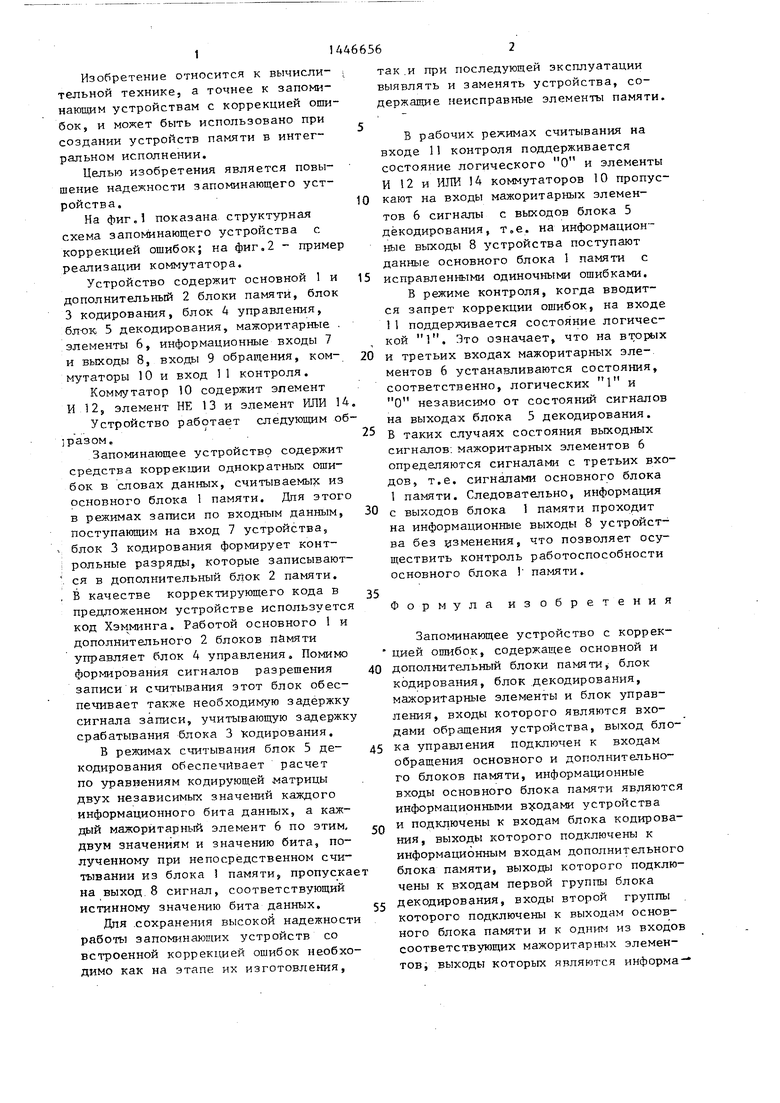

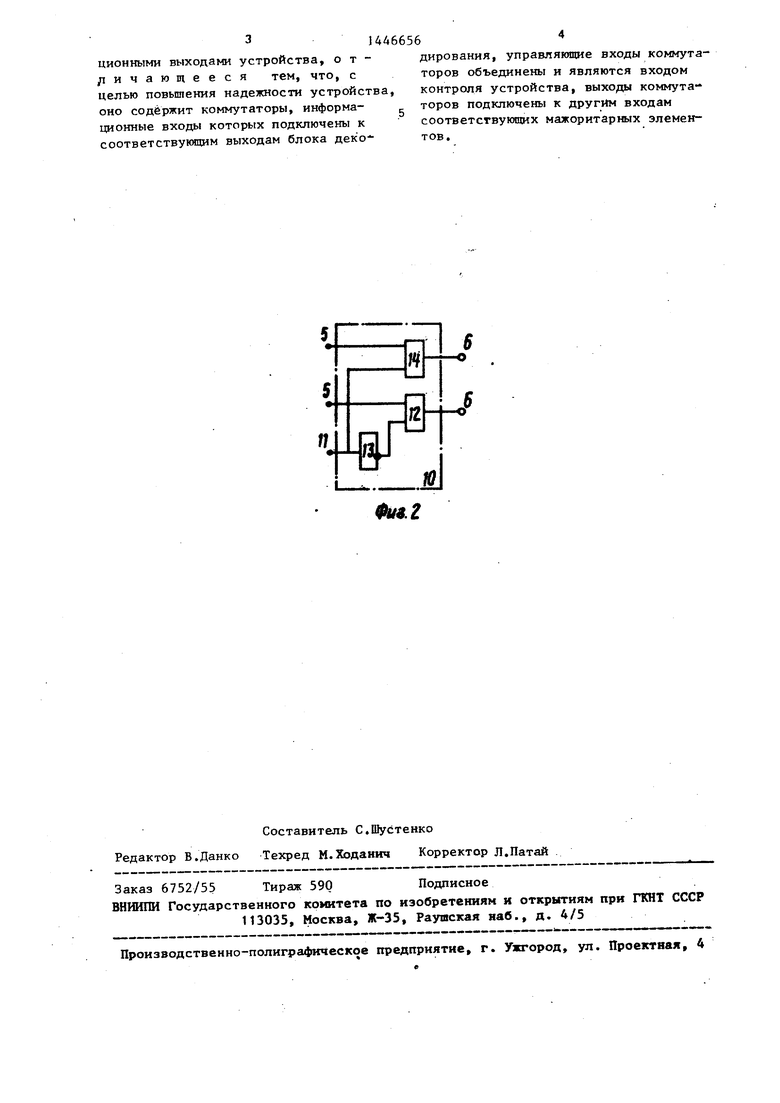

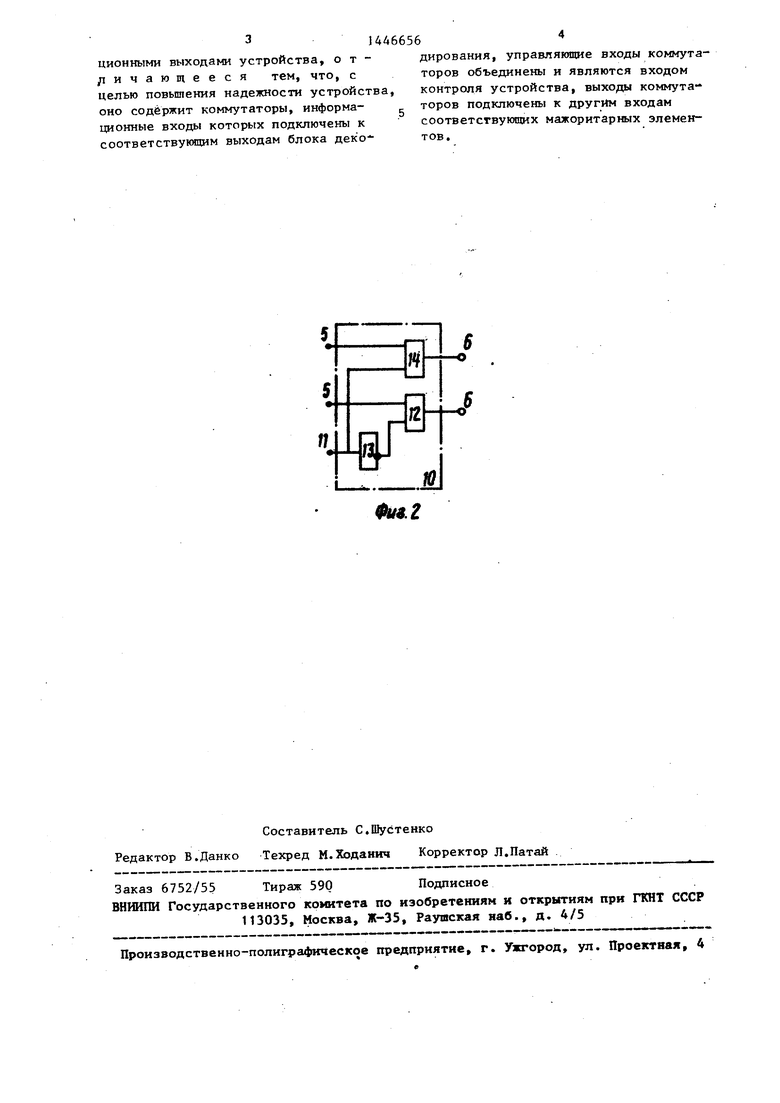

На фиг,1 показана структурная схема запотнающего устройства с коррекцией ошибок; на фиг.2 - пример реализации коммутатора.

Устройство содержит основной 1 и 15 дополнительный 2 блоки памяти, блок 3 кодирования, блок 4 управления, бл-ок 5 декодирования, мажоритарные . элементы 6, информационные входы 7 и выходы 8, входы 9 обращения, ком- 20 мутаторы 10 и вход 11 контроля.

Коммутатор 10 содержит элемент И 12, элемент НЕ 13 и элемент ИЛИ 14.

Устройство работает следующим об- pasoM,25

Запоминающее устройство содержит средства коррекции однократных ошибок в словах данных, считываемых из основного блока 1 памяти. Для этого в режимах записи по входным данным, 30 поступающим на вход 7 устройства, блок 3 кодирования формирует конт- рольные разряды, которые записывают- ся в дополнительный блок 2 памяти. В качестве корректирующего кода в 5 предложенном устройстве используется код Хэм минга. Работой основного 1 и дополнительного 2 блоков памяти управляет блок 4 управления. Помимо формирования сигналов разрешения 40 записи и считывания этот блок обеспечивает также необходимую задержку сигнала записи, учитывающую задержку срабатывания блока 3 йодирования.

В режимах считывания блок 5 де- 45 кодирования обеспечивает расчет по уравнениям кодирующей матрицы двух независимых значений каждого информационного бита данных, а каждый мажоритарный элемент 6 по этим.

двум значениям и значению бита, полученному при непосредственном считывании из блока 1 памяти, пропускае на выход.8 сигнал, соответствующий истинному значению бита данных.

Для .сохранения высокой надежности работы запоминающих устройств со встроенной коррекцией ошибок необходимо как на этапе их изготовления.

0

5

0 5 0

5

0

5

так.и при последующей эксплуатации выявлять и заменять устройства, содержащие неисправные элементы памяти.

В рабочих режимах считывания на входе 11 контроля поддерживается состояние логического О и элементы И 12 и ИЛИ 14 коммутаторов 10 пропускают на входы мажоритарных элементов 6 сигналы с выходов блока 5 декодирования, т.е. на информационные выходы 8 устройства поступают данные основного блока 1 памяти с исправленными одиночными ошибками.

В режиме контроля, когда вводится запрет коррекции ошибок, на входе 11 поддерживается состояние логической . Это означает, что на вторых и третьих входах мажоритарных элементов 6 устанавливаются состояния, соответственно, логических 1 и О независимо от состояний сигналов на выходах блока 5 декодирования. В таких случаях состояния выходных сигналов; мажоритарных элементов 6 определяются сигналами с третьих входов, т.е. сигналами основного блока 1 памяти. Следовательно, информация с выходов блока 1 памяти проходит на информационные выходы 8 устройства без изменения, что позволяет осуществить контроль работоспособности основного блока памяти.

Формула изобретения

Запоминающее устройство с коррекцией ошибок, содержащее основной и дополнит«шьный блоки памяти блок кодирования, блок .декодирования, мажоритарные элементы и блок управления, входы которого являются входами обращения устройства, выход блока управления подключен к входам обращения основного и дополнительного блоков памяти, информационные входы основного блока памяти являются информационными вводами устройства и подключены к входам блока кодирования, выходы которого подключены к информационным входам дополнительного блока памяти, выходы которого подключены к входам первой группы блока декодирования, входы второй группы . которого подключены к выходам основного блока памяти и к одним из входов соответствующих мажоритарных элементов i выходы которых являются информа-

ционными выходами устройства, о т - ;1ичаю1дееся тем, что, с целью повышения надежности устройства, оно содержит коммутаторы, информационные входы которых подключены к соответствующим выходам блока дек одирования, управляющие входы коммутаторов объединены и являются входом контроля устройства, выходы коммута- торов подключены к другим входам соответствующих мажоритарных элементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядное оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539843A1 |

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство с коррекцией однократных ошибок | 1983 |

|

SU1137540A2 |

| Оперативное запоминающее устройство с коррекцией ошибок по методу мажоритарного декодирования | 1986 |

|

SU1410105A1 |

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Устройство для коррекции ошибок | 1987 |

|

SU1541677A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

Изобретение относится к вычислительной технике, а точнее к запоминающим устройствам с коррекцией ошибок, и может быть использовано при создании устройств памяти в интегральном исполнении. Цель изобретения - повьшение надежности. Устройство содержит основной 1 и дополнительный 2 блоки памяти, блок 3 кодирования, блок 4 управления, блок 5 декодирования, мажоритарные элементы 7 6, информагтионные входы 7, икформа- ционные выходы 8, входы 9 обращения, - коммутаторы 10 и вход 11 контроля. При записи данных в блок 1 памяти одновременно форьтнруются блоком 3 контрольные коды, записываемые в блок 2 памяти. При считывании кодов из блоков 1 и 2 памяти в блоке 5 вычисляется- по двум различным формулам два значения каждого разряда информационного слова, которые поступают через соответствующие коммутаторы 10 на входы соответствующих мажоритарных элементов 6, на третьи входы которых поступает непосредственно считанный из блока 1 разряд слова На выходах 8 элементов 6 формируется информационное слово. В режиме контроля блока 1 на вход 11 подается разрешающий сигнал, блокирующий ра боту коммутаторов. На выходы элементов 6 поступает информационное слово, непосредственно считанное из блока 1, 2 ил. to

Фм.2

| Хан О | |||

| Быстродействующие ЗУБЕ со встроенными схемами исправления ошибок | |||

| - Электроника, 1984, № 18 | |||

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1988-12-23—Публикация

1987-05-22—Подача