cpus.i

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных арифметических устройствах для деления двоичных чисел с фиксированной запятой.

Цель изобретения - расширение ,- области применения путем обеспечения возможности выполнения деления над целочисленными операндами с произвольным значением.

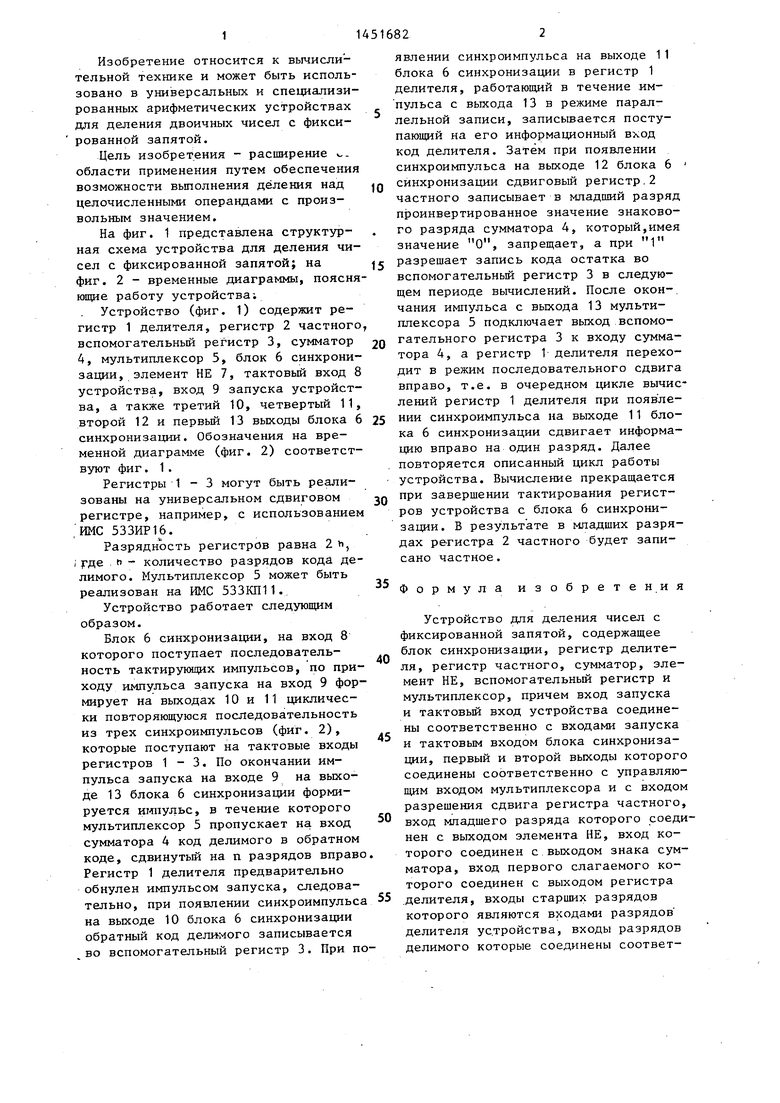

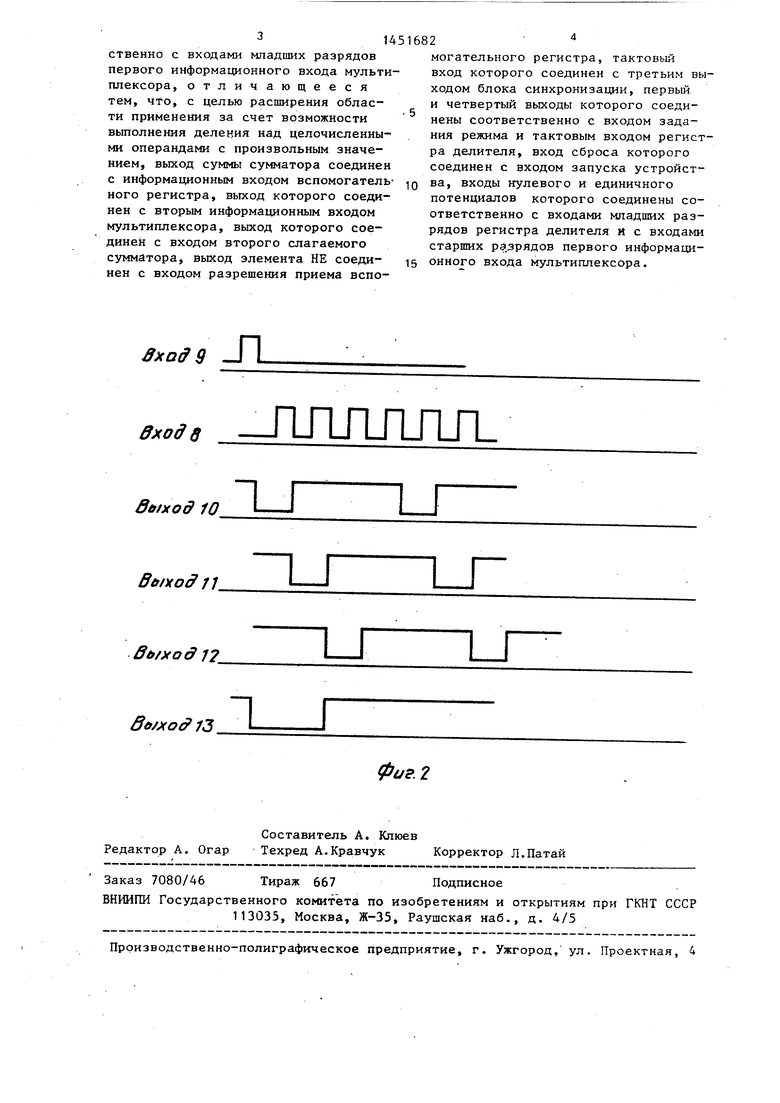

На фиг. 1 представлена структурная схема устройства для деления чисел с фиксированной запятой; на фиг. 2 - временные диаграммы, поясняющие работу устройства;

Устройство (фиг. 1) содержит регистр 1 делителя, регистр 2 частного вспомогательньй регистр 3, сумматор 4, мультиплексор 5, блок 6 синхронизации, элемент НЕ 7, тактовьш вход 8 устройства, вход 9 запуска устройства, а также третий 10, четвертый 11, второй 12 и первьй 13 выходы блока 6 синхронизации. Обозначения на временной диаграмме (фиг. 2) соответствуют фиг. 1.

Регистры 1-3 могут быть реализованы на универсальном сдвиговом регистре, например, с использованием ;ИМС 533ИР16.

Разрядность регистров равна 2 , i ря с - количество разрядов кода делимого. Мультиплексор 5 может быть реализован на ИМС 533КП11.

Устройство работает следующим образом.

Блок 6 синхронизации, на вход 8 которого поступает последовательность тактирукйдих импульсов, по приходу импульса запуска на вход 9 формирует на выходах 10 и 11 циклически повторяющуюся последовательность из трех синхроимпульсов (фиг. 2), которые поступают на тактовые входы регистров 1 - 3. По окончании импульса запуска на входе 9 на выходе 13 блока 6 синхронизации формируется импульс, в течение которого мультиплексор 5 пропускает на вход сумматора 4 код делимого в обратном коде, сдвинутый на п разрядов вправ Регистр 1 делителя предварительно обнулен импульсом запуска, следовательно, при появлении синхроимпульс на выходе 10 блока 6 синхронизации обратный код делимого записывается во вспомогательный регистр 3. При п

Q

5

0 5

о

55

5

40

45

явлении синхроимпульса на выходе 11 блока 6 синхронизации в регистр 1 делителя, работающий в течение им- пульса с выхода 13 в режиме параллельной записи, записывается поступающий на его информационный вход код делителя. Затем при появлении синхроимпульса на выходе 12 блока 6 синхронизации сдвиговый регистр.2 частного записывает в младший разряд проинвертированное значение знакового разряда сумматора 4, который,имея значение О, запрещает, а при 1 разрешает запись кода остатка во вспомогательньй регистр 3 в следующем периоде вычислений. После окон-, чания импульса с выхода 13 мультиплексора 5 подключает выход вспомогательного регистра 3 к входу сумматора 4, а регистр 1 делителя переходит в режим последовательного сдвига вправо, т.е. в очередном цикле вычислений регистр 1 делителя при появлении синхроимпульса на выходе 11 блока 6 синхронизации сдвигает информацию вправо на один разряд. Далее повторяется описанный цикл работы устройства. Вычисление прекращается при завершении тактирования регистров устройства с блока 6 синхронизации. В результате в младших разрядах регистра 2 частного будет записано частное.

Формула изобретения

Устройство для деления чисел с фиксированной запятой, содержащее блок синхронизации, регистр делителя, регистр частного, сумматор, элемент НЕ, вспомогательньй регистр и мультиплексор, причем вход запуска и тактовьй вход устройства соединены соответственно с входами запуска и тактовым входом блока синхронизации, первый и второй выходы которого соединены соответственно с управляющим входом мультиплексора и с входом разрешения сдвига регистра частного, вход младшего разряда которого соединен с выходом элемента НЕ, вход которого соединен с выходом знака сумматора, вход первого слагаемого которого соединен с выходом регистра .делителя, входы старших разрядов которого являются входами разрядов делителя устройства, входы разрядов делимого которые соединены соответ3 4

ственно с входами младших разрядов первого информационного входа мультиплексора, отличающееся тем, что, с целью расширения области применения за счет возможности вьтолнения деления над целочисленными операндами с произвольным значением, выход суммы сумматора соединен с информационным входом вспомогательного регистра, выход которого соединен с вторым информационным входом мультиплексора, выход которого соединен с входом второго слагаемого сумматора, выход элемента НЕ соединен с входом разрешения приема вспо2

могательного регистра, тактовый вход которого соединен с третьим выходом блока синхронизации, первый и четвертый выходы которого соединены соответственно с входом задания режима и тактовым входом регистра делителя, вход сброса которого соединен с входом запуска устройства, входы нулевого и единичного

потенциалов которого соединены соответственно с входами младших разрядов регистра делителя и с входами старших рз.зрядов первого информационного входа мультиплексора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

Изобретение относится к области вычислительной техники и позволяет выполнять операцию деления над операндами с произвольным-значением и получать частное с определенной разрядностью целой и дробной частей. Целью изобретения является расширение области применения за счет возможности выполнения деления над целочисленными операндами с произвольным значением. Поставленная цель достигается тем, что устройство для деления чисел с фиксированной запятой, содержащее регистр 1 делителя, регистр 2 частотного, вспомогательный регистр 3, сумматор 4, мультиплексор 5, блок 6 синхронизад15И и элемент НЕ 7, имеет новую организацию связей. 2 ил.

Вжод д

п

a.os, -ПЛПЛЛЛ.

во1жод 10

LJ

11

)(od f2

U

Во/жо 13

Г

| Устройство для деления двоичных чисел | 1985 |

|

SU1283753A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1166698, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-15—Публикация

1986-12-22—Подача