1

Изобретение относится к импульс- ной технике и предназначено для использования р измерительных устройствах.

Цель изобретения - повьш1ение точности формирования сигналов произвольной формы за счет применения переменного шага квантования по времени. .

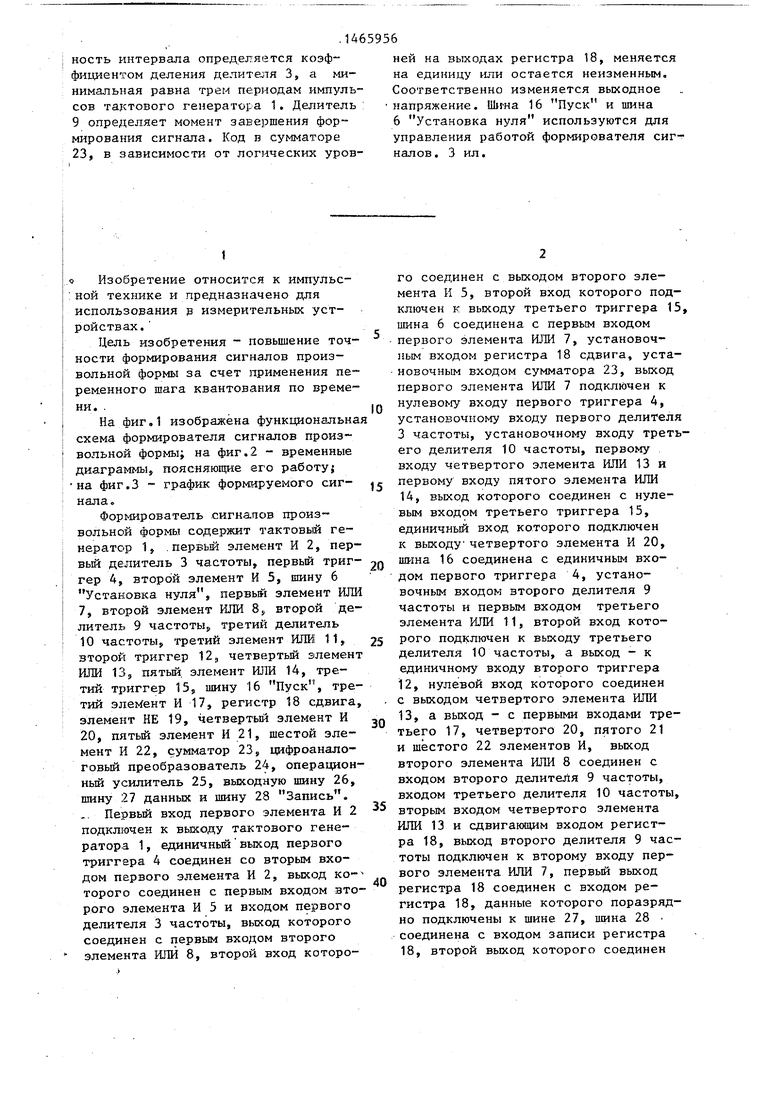

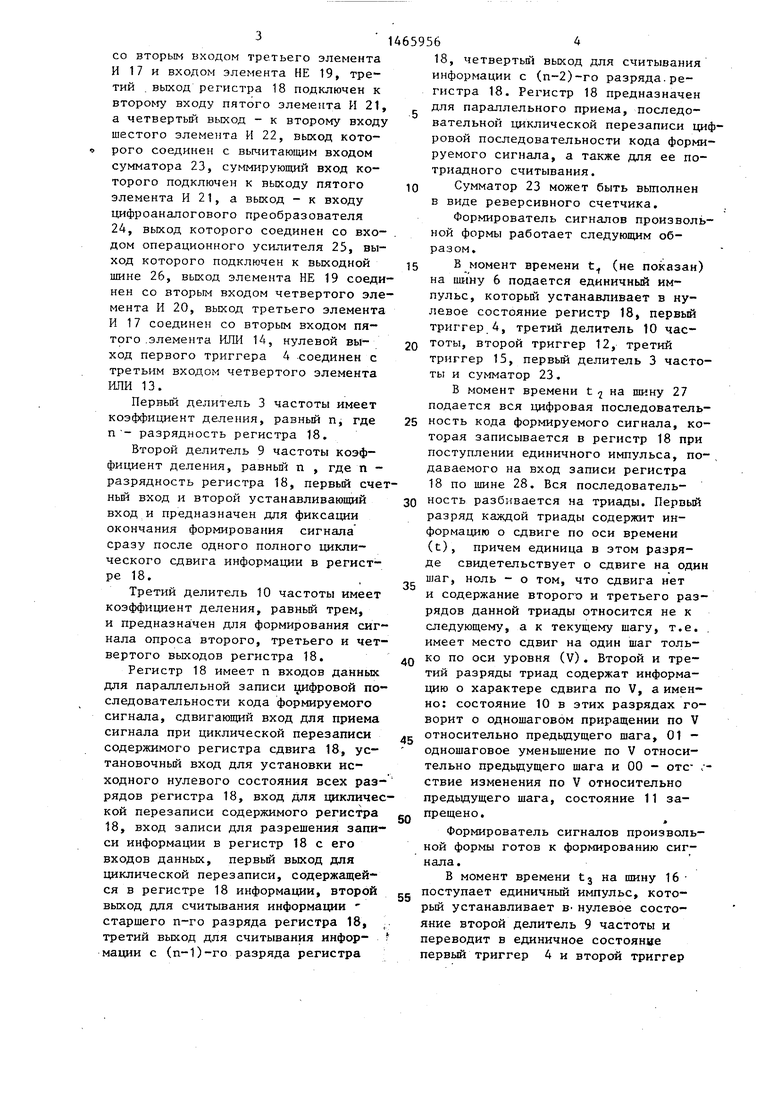

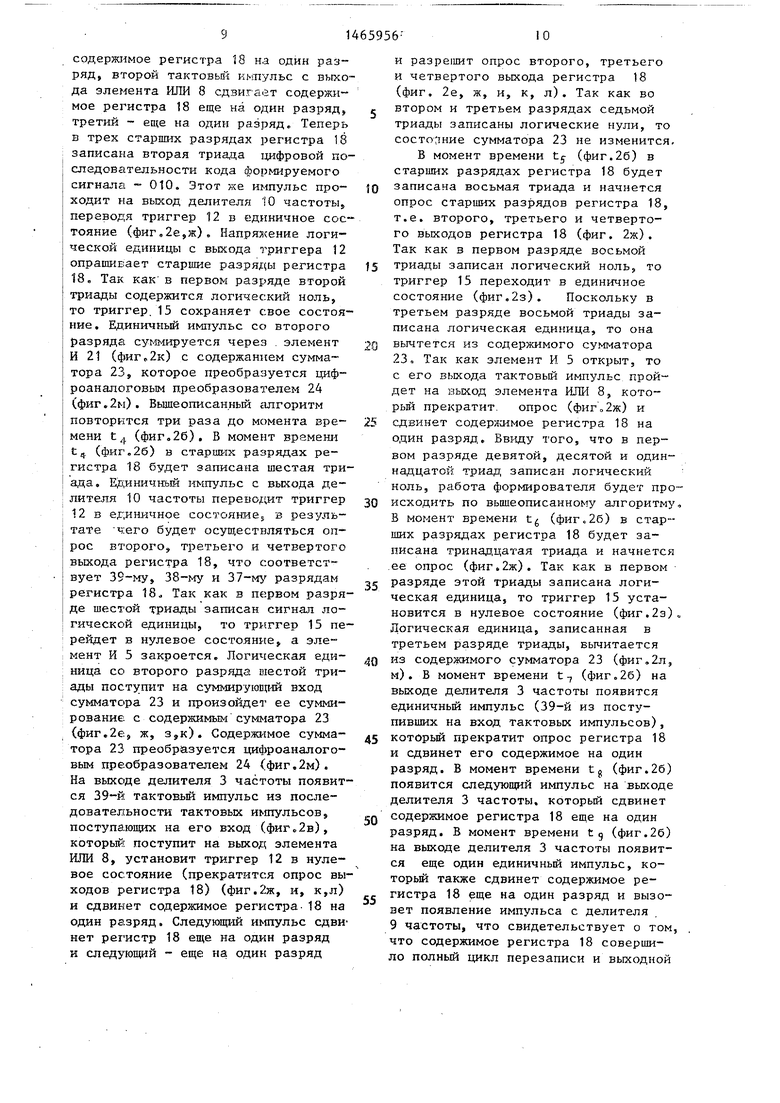

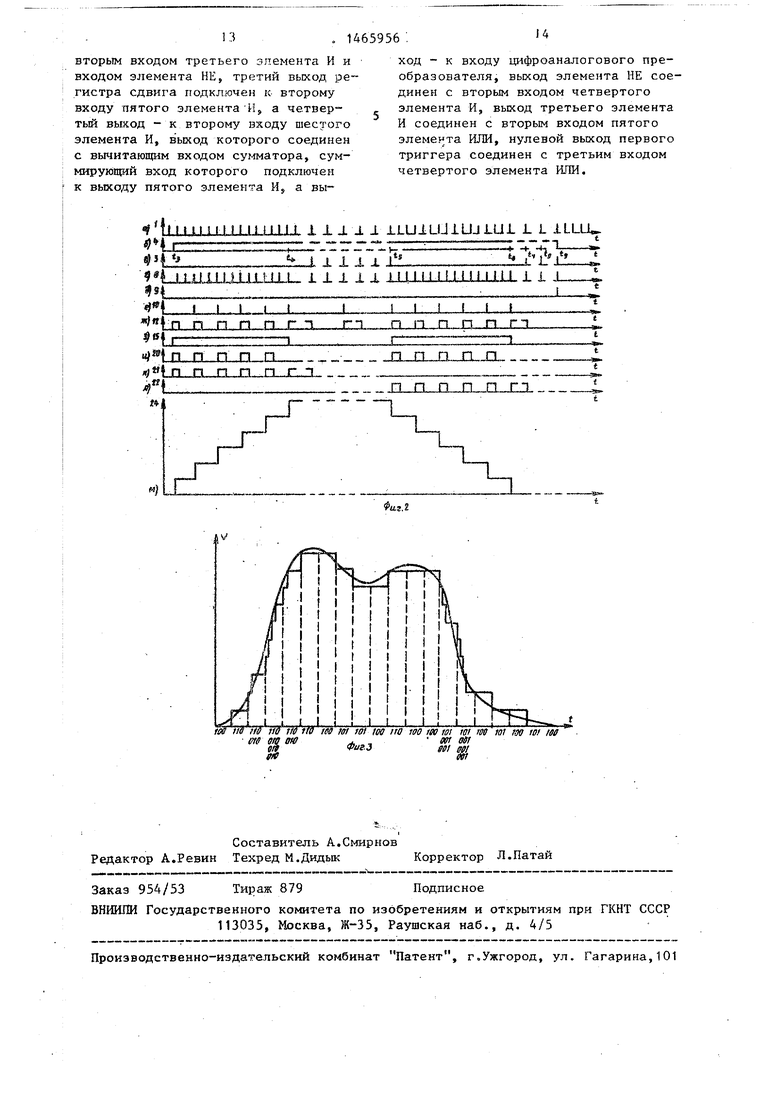

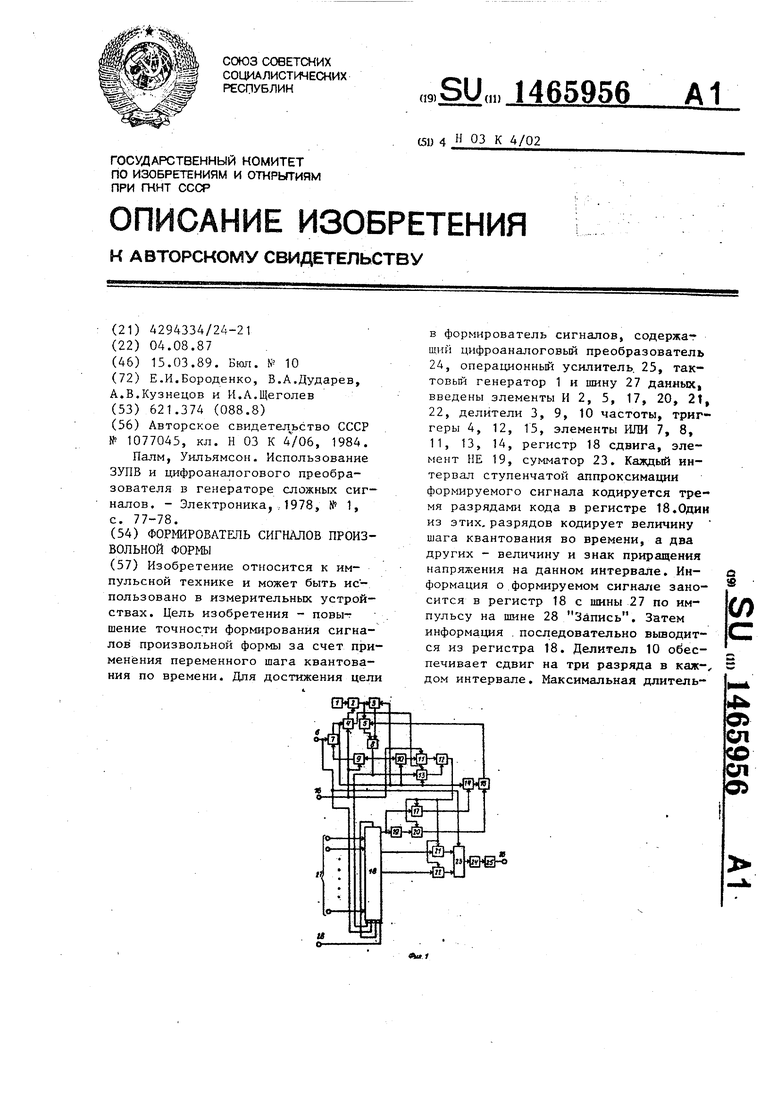

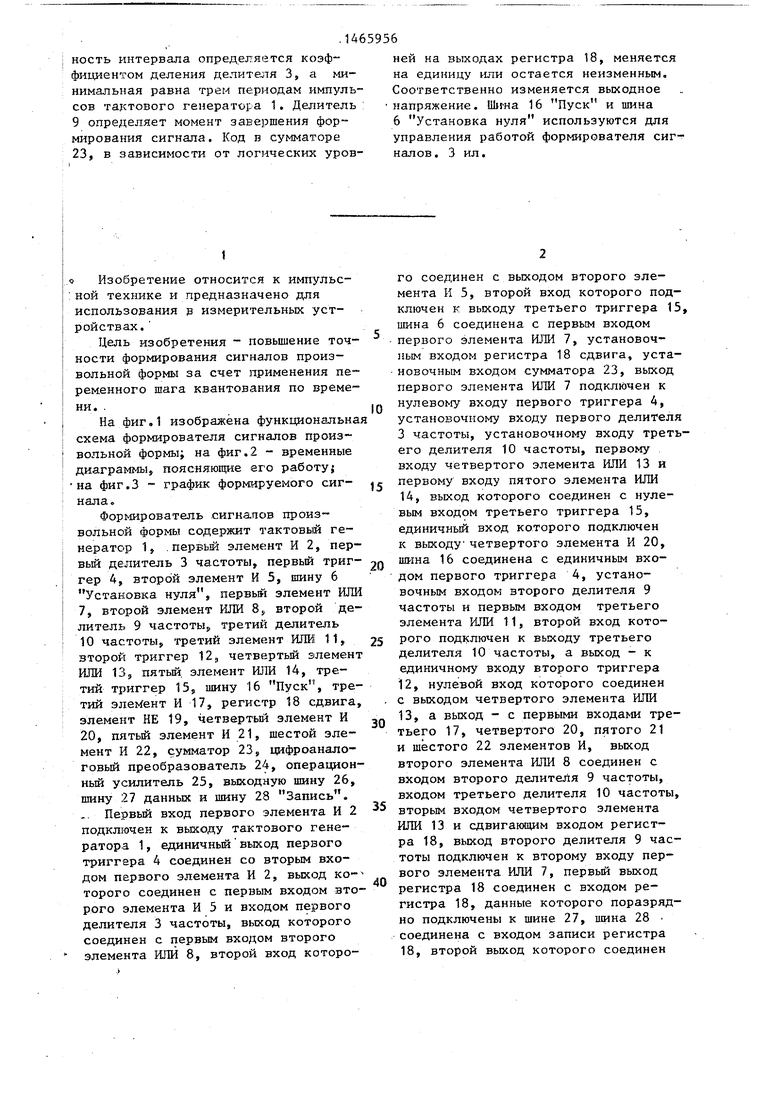

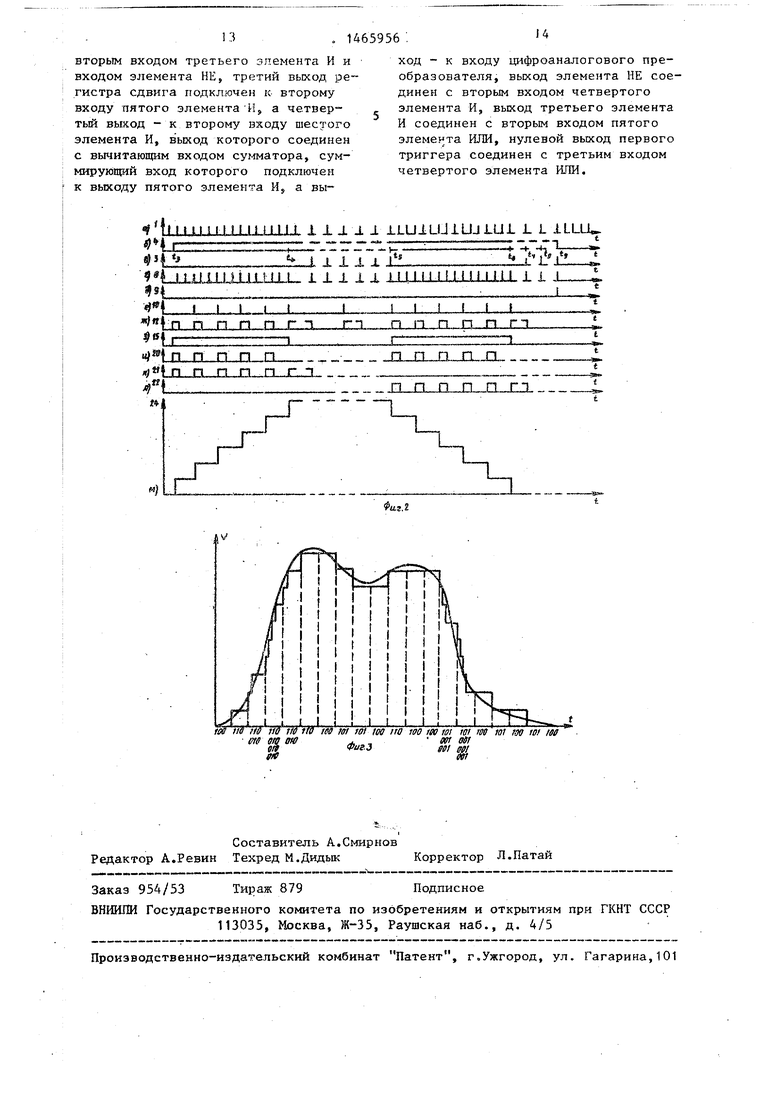

На фиг.1 изображена функциональная схема формирователя сигналов произ вольной формы; на фиг.2 - временные диаграммь, поясняющие его работу j на фиг.З - график формируемого сигнала.

Формирователь сигнапов произ™ вольной формы содержит тактовый генератор 1, .первый элемент И 2, пер- вьй делитель 3 частоты, первый триггер 4, второй элемент И 5, шину 6 Установка нуля, первьй элемент ИЛИ 7, второй элемент ИЛИ 8„ второй делитель 9 частоты, третий делитель 10 частоты, третий элемент ИЛИ 11, второй триггер 12э четвертьй элемент ИЛИ 13, пятьй элемент ИЛИ 14, третий триггер 15, шину 16 Пуск, третий элемент И 17, регистр 18 сдвига, элемент НЕ 19, четвертьй элемент И 20, пятьй элемент И 21, шестой элемент И 22, сумматор 23, цифроанало- говьй преобразователь 24, операцион- ньй усилитель 25, выходную шину 26, шину 27 данных и шину 28 Запись.

Первьй вход первого элемента И 2 подключен к выходу тактового генератора 1, единичньй выход первого триггера 4 соединен со вторым входом первого элемента И 2, выход ко- торого соединен с первым входом второго элемента И 5 и входом первого делителя 3 частоты, выход которого соединен с первым входом второго элемента ШШ 8, второй вход которо

0

5

0

5

0

го соединен с выходом второго элемента И 5, второй вход которого подключен к выходу третьего триггера 15, шина 6 соединена с первым входом первого элемента ИЛИ 7, установочным входом регистра 18 сдвига, установочным входом сумматора 23, выход первого элемента ИЛИ 7 подключен к нулевому входу первого триггера 4, установочному входу первого делителя 3 частоты, установочному входу третьего делителя 10 частоты, первому входу четвертого элемента ИЛИ 13 и первому входу пятого элемента ИЛИ 14, выход которого соединен с нулевым входом третьего триггера 15, единичньй вход которого подключен к выходу четвертого элемента И 20, шина 16 соединена с единичным входом первого триггера 4, установочным входом второго делителя 9 частоты и первым входом третьего элемента ИЛИ 11, второй вход которого подключен к выходу третьего делителя 10 частоты, а выход - к единичному входу второго триггера

12,нулевой вход которого соединен с выходом четвертого элемента ИЛИ

13,а выход - с первыми входами третьего 17, четвертого 20, пятого 21

и шестого 22 элементов И, выход второго элемента ИЛИ 8 соединен с входом второго делителя 9 частоты, входом третьего делителя 10 частоты, вторым входом четвертого элемента ИЛИ 13 и сдвигаюпщм входом регистра 18, выход второго делителя 9 частоты подключен к второму входу первого элемента ИЛИ 7, первьй выход регистра 18 соединен с входом регистра 18, данные которого поразрядно подключены к шине 27, шина 28 соединена с входом записи регистра 18, второй выход которого соединен

со вторым входом третьего элемента И 17 и входом элемента НЕ 19, третий . выход регистра 18 подключен к второму входу пятого элемента И 21 а четвертый выход - к второму входу шестого элемента И 22, выход которого соединен с вычитающим входом сумматора 23, суммирующий вход которого подключен к выходу пятого элемента И 21, а выход - к входу цифроаналогового преобразователя 24, выход которого соединен со входом операционного усилителя 25, выход которого подключен к выходной шине 26, выход элемента НЕ 19 соединен со вторым входом четвертого элемента И 20, выход третьего элемента И 17 соединен со вторым входом пятого .элемента ИЛИ 14, нулевой выход первого триггера 4 соединен с третьим входом четвертого элемента ИЛИ 13.

Первый делитель 3 частоты имеет коэффициент деления, равный п, где п - разрядность регистра 18,

Второй делитель 9 частоты коэф- фии(иент деления, paBHbDi п , где п - разрядность регистра 18, первьй сче ньй вход и второй устанавливаюпщй вход и предназначен для фиксации окончания формирования сигнала сразу после одного полного циклического сдвига информации в регистре 18.

Третий делитель 10 частоты имеет коэффициент деления, равньш трем, и предназна:чен для формирования сигнала опроса второго, третьего и четвертого выходов регистра 18.

Регистр 18 имеет п входов данных для параллельной записи цифровой последовательности кода формируемого сигнала, сдвигающий вход для приема сигнала при циклической перезаписи содержимого регистра сдвига 18, установочный вход для установки исходного нулевого состояния всех разрядов регистра 18, вход для циклической перезаписи содержимого регистра 18, вход записи для разрешения записи информации в регистр 18 с его входов данных, первьй выход для циклической перезаписи, содержащейся в регистре 18 информации, второй выход для считывания информации старшего п-го разряда регистра 18, третий выход для считывания инфор- мации с (п-1)-го разряда регистра

14659564

18, четвертьБ выход для считывания информации с (п-2)-го разряда.регистра 18. Регистр 18 предназначен для параллельного приема, последовательной циклической перезаписи цифровой последовательности кода формируемого сигнала, а также для ее по- триадного считывания. 10 Сумматор 23 может быть вьтолнен в виде реверсивного счетчика.

Формирователь сигналов произвольной формы работает следующим образом.

В момент времени t (не показан) на шину 6 подается единичный импульс, который устанавливает в нулевое состояние регистр 18, первый триггер 4, третий делитель 10 частоты, второй триггер 12, третий

триггер 15, первьй делитель 3 частоты и сумматор 23.

5

В момент времени t на шину 27 подается вся цифровая последователь- 25 ность кода формируемого сигнала, которая записывается в регистр 18 при поступлении единичного импульса, подаваемого на вход записи регистра 18 по шине 28. Вся последователь- 0 ность разбивается на триады. Первьй разряд каждой триады содержит информацию о сдвиге по оси времени (t), причем единица в этом разряде свидетельствует о сдвиге на один шаг, ноль - о том, что сдвига нет и содержание второго и третьего разрядов данной триады относится не к следующему, а к текущему шагу, т.е. имеет место сдвиг на один шаг толь- Q ко по оси уровня (V). Второй и третий разряды триад содержат информацию о характере сдвига по V, а именно: состояние 10 в этих разрядах говорит о одношаговом приращении по V относительно предьщущего шага, 01 - одношаговое уменьшение по V относительно предьщущего шага и 00 - отс- ;- ствие изменения по V относительно предыдущего шага, состояние 11 запрещено.

Формирователь сигналов произвольной формы готов к формированию сигнала.

В момент времени t3 на шину 16 g поступает единичньй импульс, кото- рьй устанавливает В нулевое состояние второй делитель 9 частоты и переводит в единичное состояние первьй триггер 4 и второй триггер

5

0

12 (через третий элеме.нт ИЛИ 1 ТУ, Напряжение логической едиииць с выхода второго триггера 12 поступает на первые входы тре тьего 17,чет- вертого 20J пятого 21 и шестого 22 1элементов И, Если на третьем выходе ррегистра 18 присутствует напряжение Логической единицы, то оно через рткрытьш пятый элемент И 21 посту- ает на суммирующий вход сумматора J23 и суммируется в нем. Если на чет- |вертом выходе регистра 18 присутст- |вует напряжение логической едини- jubij то оно через шестой элемент И 122 поступает на вычитаюш5гй вход сум- матора 23 и вычитается из его содер- имого. Присутствие напряжения ло- Гической единицы на третьем и чет- Ьертом входах регистра 1,8 одновре- |менно невозможно Если на втором вы- |ходе регистра 18 присутствует напря- ,Ыние логического нуля, то оно, ин- |вертируясь элементом НЕ 19, поступа- |ет через открытый четвертьй элемент |и 20 на единичный вход третьего триг jrepa 15„ переводя его в единичное |состояние. Напряжение логической |единицы с выхода третьего триггера 15 поступает на второй вход второго |элемента И 5, открывая его. Если ;на втором выходе регистра 18 при- |сутствует напряженке логической еди |Ш1цы, то третий триггер 15 не изме- няет своего состояния, в результате Чего второй элемент И 5 остается закрытым.

Напр;1жение логической единицы с единичного выхода первого триггера 4 поступает на второй вход перво- го элемента И 2, разрешая тем самым прохождение тактовых импульсов с выхода тактового генератора 1.Тактовые И1 тульсы поступают на счет- ньй вход первого делителя 3 частоты и на первый вход второго элемента И 5, ЕС.ПИ на втором входе второго элемента И 5 присутствует напряжение логического нуля, т,,е. на втором выходе регистра 18 присутствует нагфяжение логической единицы, то второй элемент И 5 не пропускает тактовые импульсы на свой выход. Импульс на выходе первого делителя 3 частоты формируется при подсчете им тактовых импульсов. Этот импульс, пройдя через второй элемент . ИЛИ 8, поступит на входы второго 9 и треть ° его 10 делителей частоты, через чет

вертый элемент ИЛИ 13, установит в нулевое состояние второй триггер 12 и циклически сдвинет на один разряд содержимое регистра 18. Так повторяется три раза. После поступления третьего импульса на первьй счетный вход делителя 10 частоты на его выходе появится единичный импульс, ко- торьй через третий элемент ИЛИ 11 переводит второй триггер 12 в единичное состояние. Напряжение логической единицы с выхода второго триггера 12 поступает на первые входы третьего 17, четвертого 20, пятого 21 и шестого 22 элементов И. Напряжение логической единицы с третьего или четвертого выходов регистра 18 поступит на суммирующий или вычитающий входы сумматора 23, суммируясь или вычитаясь с его содержимым, которое в свою очередь поступает на вход цифроаналогового преобразователя 24, преобразующего содержимое сумматора 23 в напряжение ступенчатой формы, поступающее на вход операционного усилителя 25, которьй формирует из него аналоговьй сигнал, выдаваемьй на выходную шину 26. Если на втором выходе регистра 18 присутствует напряжение логической единицы, то работа формирователя сигналов произвольной формы далее повторяется по вышеописанному алгоритму. Если на втором выходе регистра 18 присутствует напряжение логического нуля, то оно инвертируется элементом НЕ 19 и через открытьй четвертьй элемент И 20 переводит третий триггер 15 в единичное состояние. Напряжение логической единицы с выхода третьего триггера 15 поступает на второй вход второго элемента И 5, открывая его. Тактовые импульсы с выхода первого элемента И 2, проходя через второй элемент И 5, поступают на выход второго элемента ИЛИ 8 и подаются на входы второго 9 и третьего 10 делителей частоты. ПервЬй импульс переводит второй триггер 12 в нулевое состояние. Тактовые импульсы с выхода второго элемента ИЛИ 8 сдвигают содержимое регистра 18. Когда содержимое регистра будет сдвинуто на три разряда, то на выходе третьего делителя 10 частоты появится импульс, которьй переведет второй триггер 12 в единичное состояние. Напряжение логической единицы на выходе триггера 12 откроет третий 17, четвертый 20, пятый 21 и шестой 22 элементы И. Содержимое второго и третьего разряда регистра 18 будет суммироваться или вычитаться в сумматоре 23, изменяя или оставляя без изменения его содержимое .

Если на втором выходе регистра 18 присутствует напряжение логического нуля, то работа формирователя происходит по вышеописанному алго- ритму до появления при опросе второго выхода напряжения логической еди(шцы.

Работа формирователя будет осуществляться до появления на выходе второго делителя 9 частоты импульса, которьй будет свидетельствовать о том, что формируемьй сигнал полностью синтезирован, т.е. содержимое регистра 18 совершило один цикл перезаписи. Этот импульс через первый элемент ИЛИ 7 поступает на нулевой вход первого триггера 4, переводя его в нулевое состояние, а на его единичном выходе появится напряжение логического нуля, которое поступит на второй вход первого элемента И 2, запрещая тем самым прохождение тактовых импульсов на его выход. На этом работа формирователя сигналов заканчивается.

При необходимости сформировать следующий сигнал на шину 16 поступает единичный импульс и формирователь сигналов начинает работать по вьш1е- описанному алгоритму.

Рассмотрим конкретный пример работы формирователя сигналов произвольной формы (фиг.2).

В момент времени t, (не показан) на шину 6 подается единичный импульс которьй устанавливает в нулевое состояние блоки 18, 4, 10,12, 15, 3 и 23.

В момент времени t (не показан) на шину 27 в параллельном виде подается 39-разрядная цифровая последовательность кода формируемого сигнала вида: 010 010 010 010 010 110 100 001 001 001 001 001 101. Подается единичный импульс на шину 28 и информация записывается в блок 18 по триадам:

010 - первая триада (записывается в старшие разряды регистра 18);

0

5

0

5

0

5

0

5

0

5

010 - вторая триада; 010 - третья триада; 010 - четвертая триада 010 - пятая триада; 110 - шестая триада;

100- седьмая триада; 001 - восьмая триада; 001 - девятая триада; 001 - десятая триада;

001 - одиннадцатая триада; 001 - двенадцатая триада;

101- тринадцатая триада (записывается в младшие разряды регистра 18).

Формирователь сигналов произвольной формы готов к формированию сигнала. В момент времени tj (фиг.26) на шину 16 поступает импульс, устанавливающий в нулевое состояние делитель 9 частоты и переводяпщй в единичное состояние триггер 4 и триггер 12. На выходе триггера 12 появляется напряжение логической единицы (фиг.2ж), которое открьшает элемента И 17, 20, 21 и 22. Так как первьй разряд первой триады содержит логический ноль, то на выходе элемента И 20 появится напряжение логической единицы (фиг.2и), которое переведет в единичное состояние триггер 15 (фиг.2з). Так как во втором разряде первой триады записана логическая единица, то на выходе элемента И 21 появится напряжение логической единицы (фиг.2к), которое поступит на. суммирующий вход сумматора 23. Содержимое сумматора 23 поступит на вход цифро- аналогового преобразователя 24, на выходе которого будет присутствовать сигнал, пропорциональньй содержимому сумматора 23, т.е. единице, (фиг.2м).

Напряжение логической единицы с выхода триггера 4 разрешит прохождение через элемент И 2 тактовых импульсов с тактового генератора 1. Так как на втором входе элемента И 5 присутствует напряжение логической единицы с триггера 13, то на выход элемента ИЛИ 8 будут поступать тактовые импульсы (фиг. 2г), Первьй тактовый импульс с выхода элемента ИЛИ 8 установит триггер 12 в нулевое состояние и опрос 39-го, 38-го и 37-го разрядов регистра 18 прекращается (фиг.2г, ж, и, к). Этот же тактовьй импульс сдвигает

содержимое регистра 18 на один разряд, второй ТаКТОВЬВ импульс с элемента ИЛИ 8 сдвигает содержи- мое регистра 18 еще на один разряд, третий - еще на один разряд. Теперь в трех старших разрядах регистра 18 записана вторая триа,ца цифровой последовательности кода формируемого сигнала 010. Этот же импульс проходит на выход делителя 10 частоты переводя триггер 12 в единичное состояние (фиг,2е,ж). Напряжение логической единицы с выхода триггера 12 опрашивает старшие разряды регистра 18, Так как в первом разряде второй триады содержится логический ноль, то триггер. 15 сохраняет свое состояние, Единичньй импульс со второго разряда су№-1ируется через . элемент И 21 (фиг„2к) с содержанием сумматора 23, которое преобразуется циф- роаналоговым преобразователем 24 (фиг.2м). Вышеописанный гшгоритм повторится три раза до момента времени t (фиг,26). В момент времени t (фиг,26) в старших разрядах регистра 18 будет записана шестая триада, Е;);иничный импульс с выхода делителя 10 частоты переводит триггер 12 в единичное состояние; в результате 4QTO будет осуществляться опрос второго., третьего и четвертого выхода регистра 18, что соответст вует 39-му, 38-му и 37-му разрядам регистра 18 о Так как в п€:рвом разряде шестой триады записан сигнал логической единицы, то Tpiirrep 15 перейдет в нулевое состояние, а элемент И 5 закроется. Логическая единица со второго разряда шестой триады поступит на суммируюпщй вход сумматора 23 и произойдет ее суммирование с содержимым сумматора 23 (фиг,26, ж, з,к). Содержимое сумматора 23 преобразуется цифроаналого- вым преобразователем 24 (фиг,2м). На выходе делителя 3 частоты появится 39-и тактовьй импульс из последовательности тактовых импульсов, поступающих на его вход (фиг«2в), которьй поступит на выход элемента ИЛИ 8, установит триггер 12 в нулевое состояние (прекратится опрос выходов регистра 18) (фиг,2ж, и, к,л) и сдвинет содержимое регистра-18 на один разряд, Следующий импульс сдвн нет регистр 18 еще на один разряд к следующий - еще на один разряд

и разрешит опрос второго, третьего И четвертого выхода регистра 18 (фиг. 2е, ж, и, к, л). Так как во с втором и третьем разрядах седьмой триады записаны логические нули, то состояние сумматора 23 не изменится.

В момент времени tj (фиг.26) в старших разрядах регистра 18 будет

0 записана восьмая триада и начнется опрос старших разрядов регистра 18, т.е. второго, третьего и четвертого выходов регистра 18 (фиг. 2ж). Так как в первом разряде восьмой

5 триады записан логический ноль, то триггер 15 переходит в единичное состояние (фиг.2з). Поскольку в третьем разряде восьмой триады записана логическая единица, то она

0 вычтется из содержимого сумматора 23. Так как элемент И 5 открыт, то с его выхода тактовьй импульс пройдет на выход элемента ИЛИ 8, которьй прекратит. опрос (фиг о2ж) и

5 сдвинет содерлсимое регистра 18 на один разряд. Ввиду того, что в первом разряде девятой, десятой и одиннадцатой триад записан логический ноль, работа формирователя будет про0 исходить по вышеописанному алгоритму,

8момент времени t (фиг.26) в старших разрядах регистра 18 будет записана тринадцатая триада и начнется ее опрос (фиг.2ж). Так как в первом

2 разряде этой триады записана логическая единица, то триггер 15 установится в нулевое состояние (фиг.2з), Догическая единица, записанная в третьем разряде триады, вычитается

0 из содержимого сумматора 23 (фиг,2л, м) , В момент времени t-, (фиг.26) на выходе делителя 3 частоты появится единичньй импульс (39-й из поступивших на вход тактовых импульсов),

5 которьй прекратит опрос регистра 18 и сдвинет его содержимое на один разряд, В момент времени tg (фиг.26) появится следующий импульс на выходе делителя 3 частоты, которьй сдвинет

Q содержимое регистра 18 еще на один разряд, В момент времени tg (фиг.2б) на выходе делителя 3 частоты появится еще один единичньй импульс, которьй также сдвинет содержимое ре гистра 18 еще на один разряд и вызовет появление импульса с делителя

9частоты, что свидетельствует о том, что содержимое регистра 18 совершило полньй цикл перезаписи и выходной

1465956

игнал сформирован. Триггер 4 также

g м 10 п 15 с 20 ш п г в 25 ч г д д в 30 и в вх ны ду со го вт вх вх 40 тр к ну хо вы 45 че то со ча ча 50 эл ре ли вх вы 55 вх ны к не га

перейдет в нулевое состояние, напряжение логического нуля с его выхода (фиг.26) закроет элемент И 2, а напряжение логической единицы с его нулевого выхода запретит дальнейший опрос разрядов регистра 18. На этом работа формирователя сигналов по формированию сигнала по его цифровому коду заканчивается. Для вторичного и более формирования этого сигнала вышеописанный алгоритм повт торяется нужное количество раз при подаче сигнала на шину 16. Разрядность регистра 18 и коэффициенты деления делителей 3 и 9 частоты могут быть кратны числу три и должны быть равны или больше длины цифровой последовательности кода формируемого сигнала. Если длина последовательности меньше разрядности регистра 18, то она добавляется триадами вида 100, которые не влияют на форму импульса, а влияют только не. момент его появления. Они добавляются впереди, если необходимо сформировать импульс с определенной временной задержкой.

На фиг.З приведен еще один пример формирования сигнала, причем значения кодовых триад указаны под осью эремени.

Предлагаемый формирователь сигналов обеспечивает формирование сигнала произвольной формы с переменным шагом квантования по времени.

Формула изобретения

Формирователь сигналов произвольной формы, содержащий последовательно соединенные цифроаналоговый преобразователь, операционный усилитель и выходную шину, а также тактовый генератор и шину данных, о т- личающийся тем, что, с целью повьш1ения точности формирования сигналов произвольной формы за счет использования переменного шага квантования по времени, в него введены первьй элемент И, первый делитель частоты, первый триггер, второй элемент И, шина Установка нуля, первый элемент ИЛИ, второй элемент ИЛИ, второй делитель частоты, третий делитель частоты, третий элемент ИЛИ, второй триггер четвертый элемент ИЛИ, пятьй эле12

мент 1иш, третий триггер, шина Пуск, третий элемент И, регистр сдвига, элемент НЕ, четвертый эле- g мент И, пятый элемент И, шестой элемент И, сумматор данных, шина Запись, причем первьй вход первого элемента И подключен к выходу тактового генератора,единичньй выход 0 первого триггера соединен с вторым входом первого элемента И, выход которого соединен с первым входом второго элемента И и входом первого делителя частоты, выход которого 5 соединен с первым входом второго элемента ШШ, второй вход которого соединен с выходом второго эле- MCiira И, второй вход которого подключен к выходу третьего триггера, 0 шина Установка нуля соединена с первым входом первого элемента ИЛИ, установочным входом регистра сдвига и установочньЕм входом сумматора, выход первого элемента ИЛИ подклю- 5 чей к нулевому входу первого триггера, установочному входу первого делителя частоты, установочному входу третьего делителя частоты, первому входу четвертого элемента ИЛИ 0 и первому входу пятого элемента ИЛИ, выход которого соединен с нулевым входом третьего триггера, единичный вход которого подключен к выходу четвертого элемента И, шина Пуск соединена с eдиничн Iм входом первого триггера, установочным входом второго делителя частоты и первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу. 0 третьего делителя частоты, а выход - к единичному входу BTOpoi o триггера, нулевой вход которого соединен с выходом четвертого элемента ИЖ, а выход - с первыми входами третьего, 5 четвертого, пятого и шестого элементов И, выход второго элемента ИЛИ соединен с входом второго делителя частоты, входом третьего делителя частоты, вторым входом четвертого . 0 элемента ИЛИ и сдвигающим входчм регистра сдвига, выход второго делителя частоты подключен к второму входу первого элемента ИЛИ, первьй выход регистра сдвига соединен с 5 входом регистра сдвига, входы данных которого поразрядно подключены к шине данных, шина Запись соединена с входом записи регистра сдвига, второй выход которого соединен с

вторым входом третьего элемента И и входом элемента НЕ, третий выход регистра сдвига подключен к- второму входу пятого элемента Hj а четвер- тьй выход - к второму входу шестого элемента И, вькод которого соединен с вычитающим входом сумматора, суммирующий вход которого подключен к выходу пятого элемента И а выход - к входу цифроаналогового преобразователя, выход элемента НЕ соединен с вторым входом четвертого элемента И, выход третьего элемента И соединен с вторьм входом пятого элемента ИЛИ, нулевой выход первого триггера соединен с третьим входом четвертого элемента ИПИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля сигналов произвольной формы | 1986 |

|

SU1406527A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1451857A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU1084901A1 |

| Устройство для возведения в степень | 1987 |

|

SU1499338A1 |

| Устройство для деления в избыточном коде | 1984 |

|

SU1280612A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Генератор псевдослучайных чисел | 1984 |

|

SU1239844A1 |

| Устройство для вычисления кубического корня | 1980 |

|

SU1084786A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

Изобретение относится к импульсной технике и может быть использовано в измерительных устройствах. Цель изобретения - повы- шение точности формирования сигналов произвольной формы за счет применения переменного шага квантования по времени. Для достижения цели в формирователь сигналов, содержат ший цифроаналоговый преобразователь 24, операционный усилитель, 25, так- товьй генератор 1 и шину 27 данных, введены элементы И 2, 5, 17, 20, 21, 22, делители 3, 9, 10 частоты, триггеры 4, 12, 15, элементы ИЛИ 7, 8, 11, 13, 14, регистр 18 сдвига, элемент НЕ 19, сумматор 23. Каждый интервал ступенчатой аппроксимации формируемого сигнала кодируется тре- мя разрядами кода в регистре 18.Один из этих, разрядов кодирует величину шага квантования во времени, а два других - величину и знак приращения напряжения на данном интервале. Информация о формируемом сигнале заносится в регистр 18 с шины 27 по импульсу на шине 28 Запись. Затем информация . последовательно выводится из регистра 18. Делитель 10 обеспечивает сдвиг на три разряда в каж-, дом интервале. Максимальная длительО) с

«)

йя № ffertff iw fto те tst wi too no wo leo roi rat

ets ere o№ , act eif

eSФагЗset ffgt

rFk.t

101 rao WI lee

| Формирователь трапецеидальных импульсов | 1982 |

|

SU1077045A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Палм, Уильямсои | |||

| Использование ЗУПВ и цифроаналогового преобразователя в генераторе сложных сигналов | |||

| - Электроника, | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Спускная труба при плотине | 0 |

|

SU77A1 |

Авторы

Даты

1989-03-15—Публикация

1987-08-04—Подача