Изобретение относится к технике измерений и может быть использовано для автоматического контроля сигналов произвольной формы в сложных системах контроля и управления технологическими процессами.

Целью изобретения является повышение достоверности контроля.

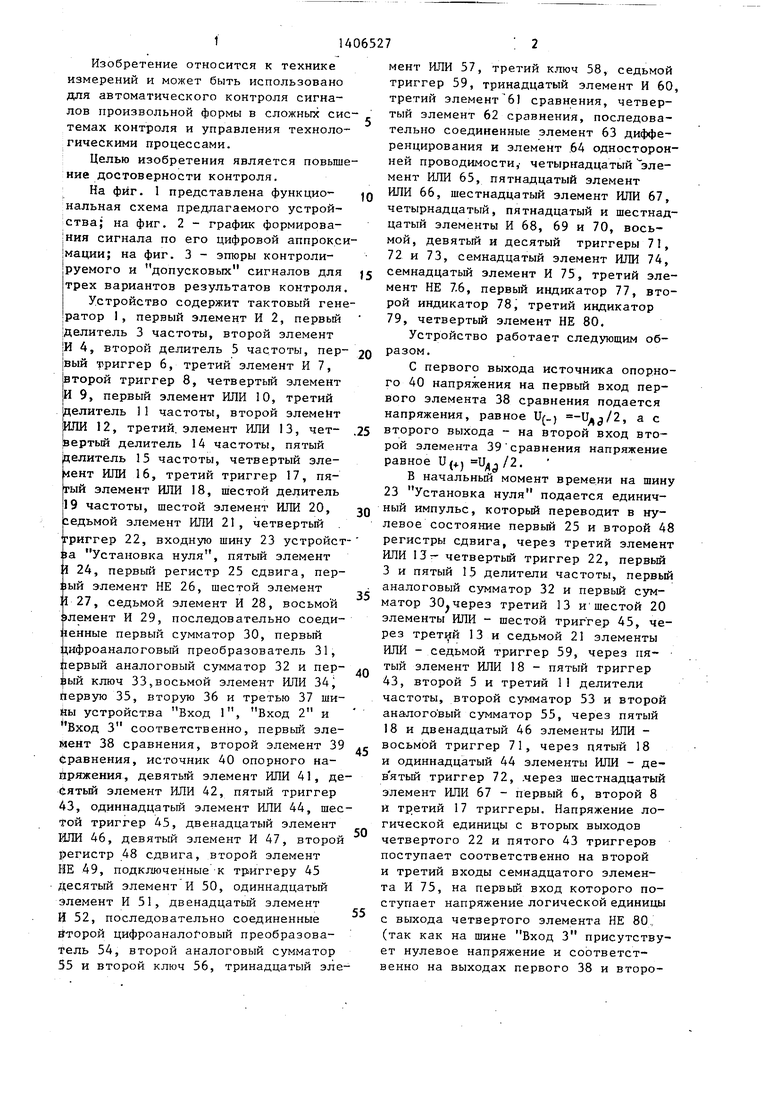

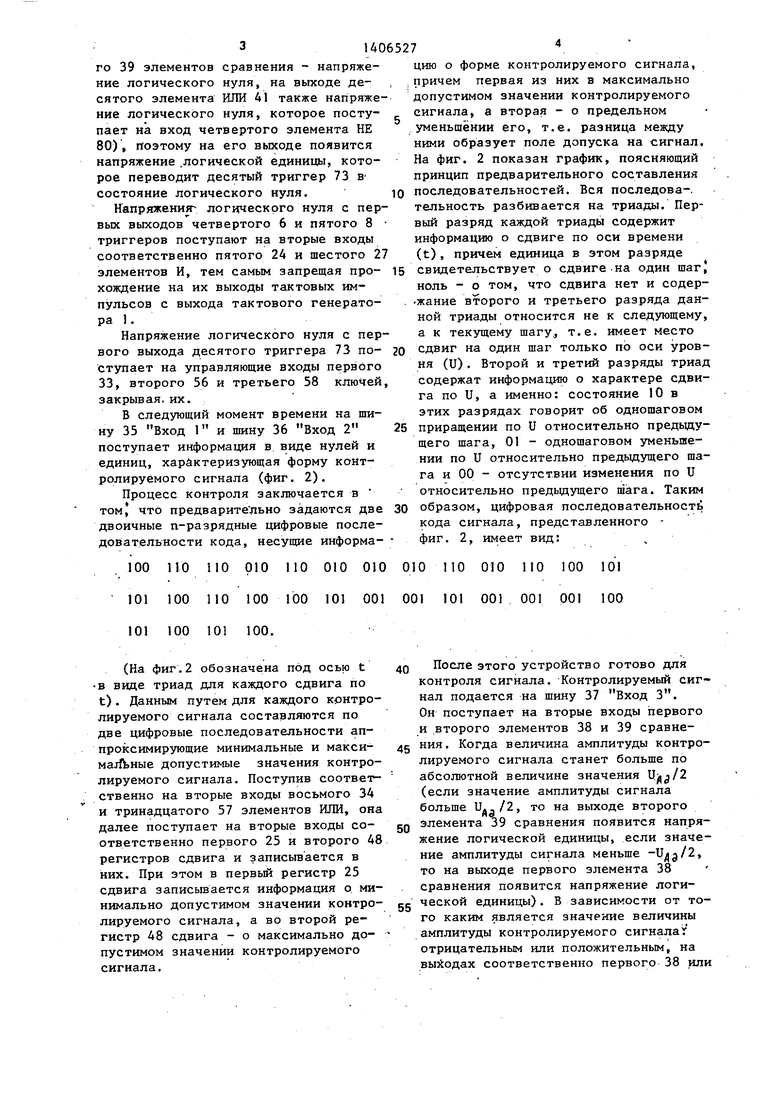

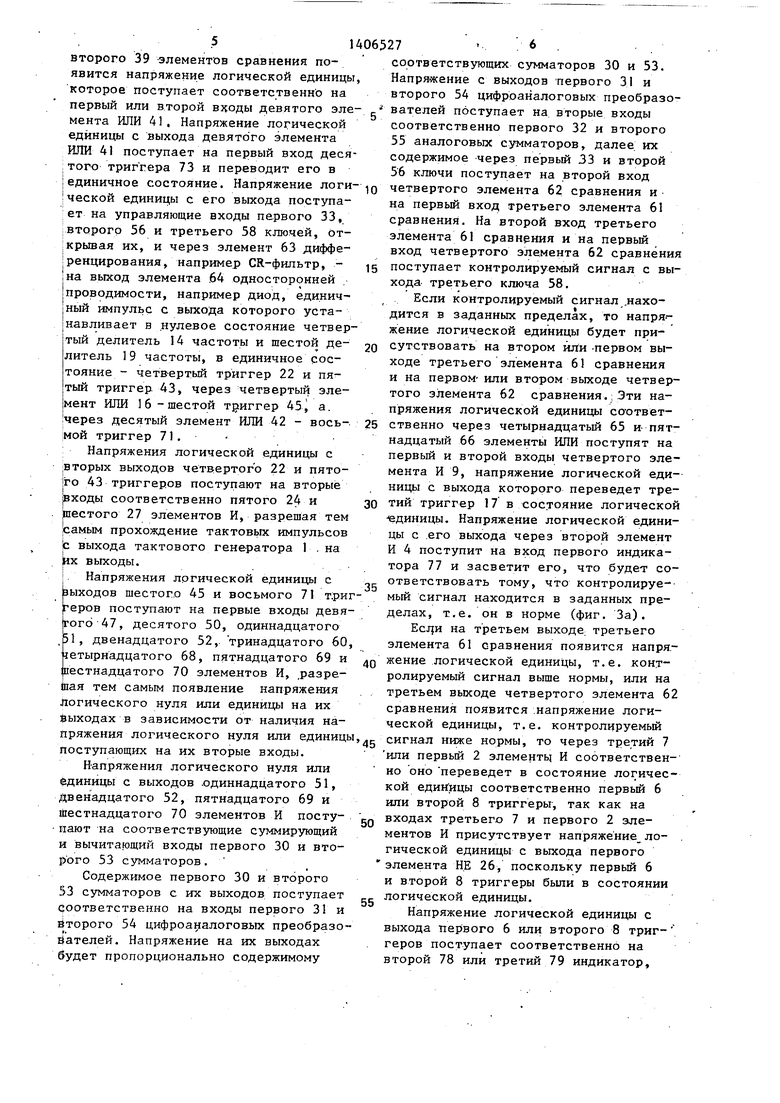

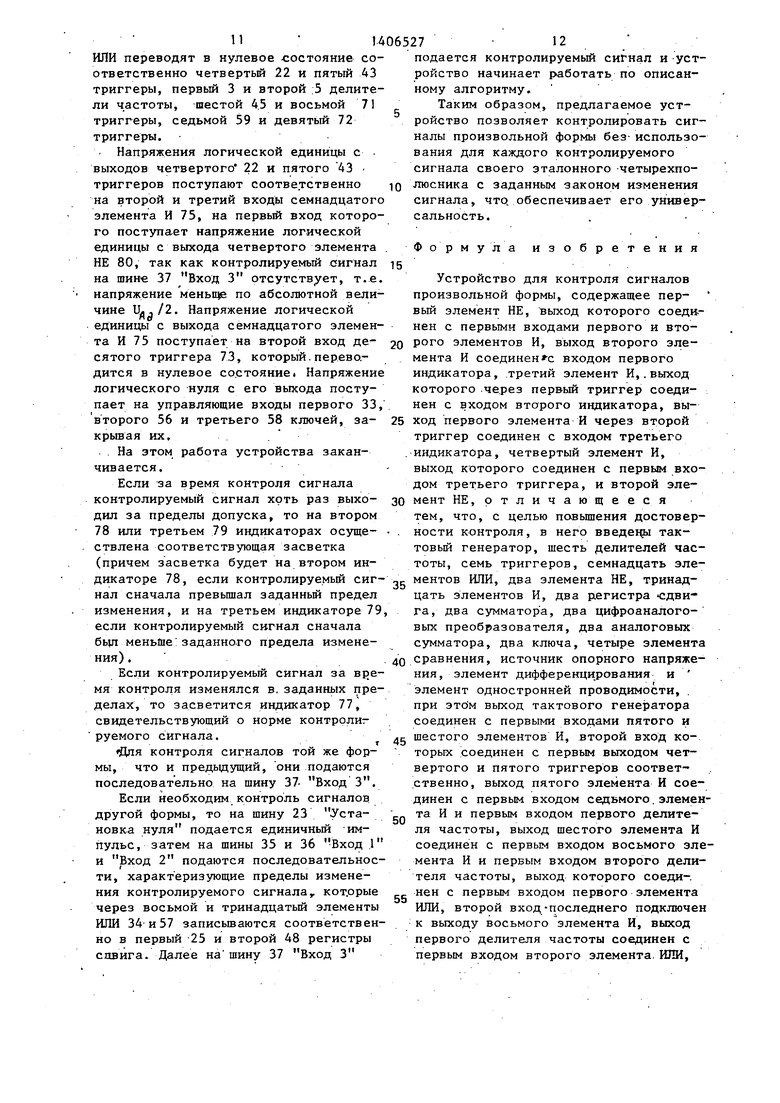

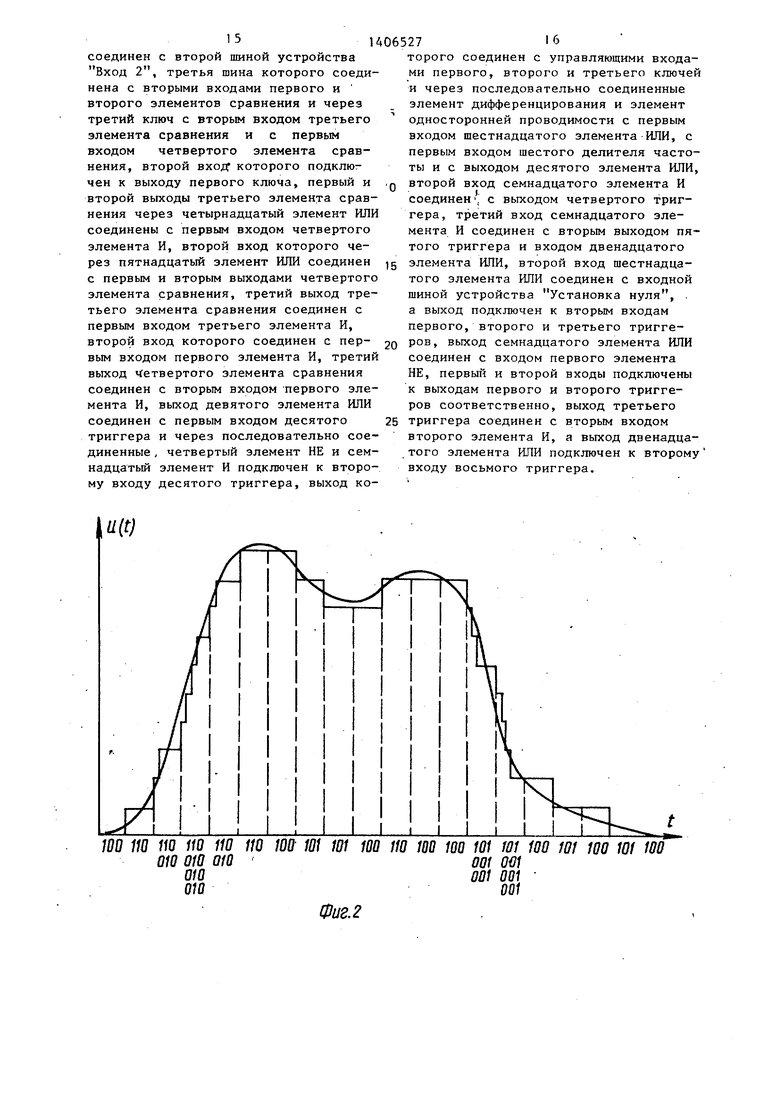

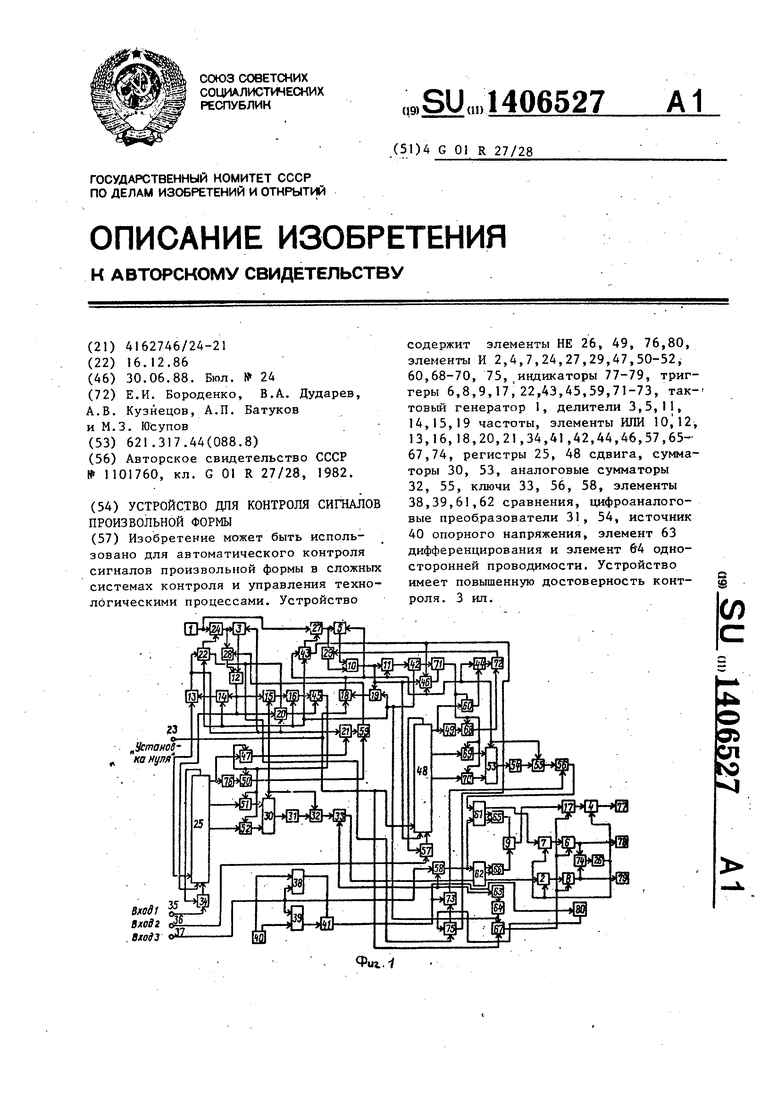

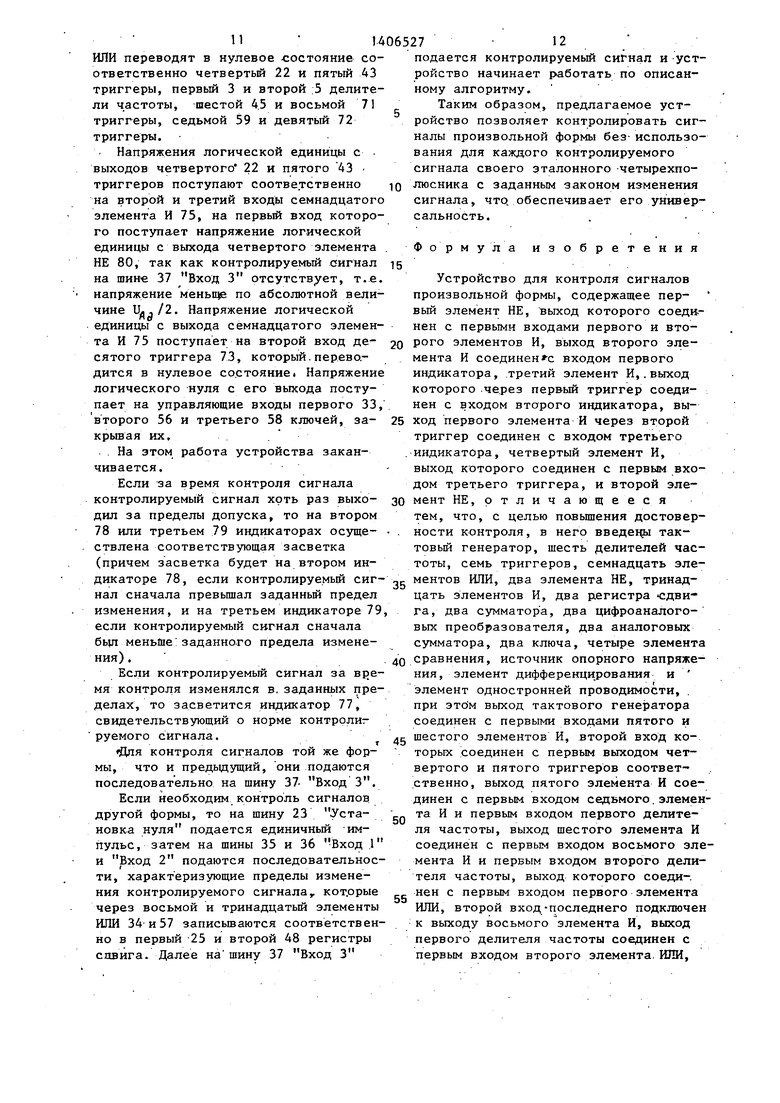

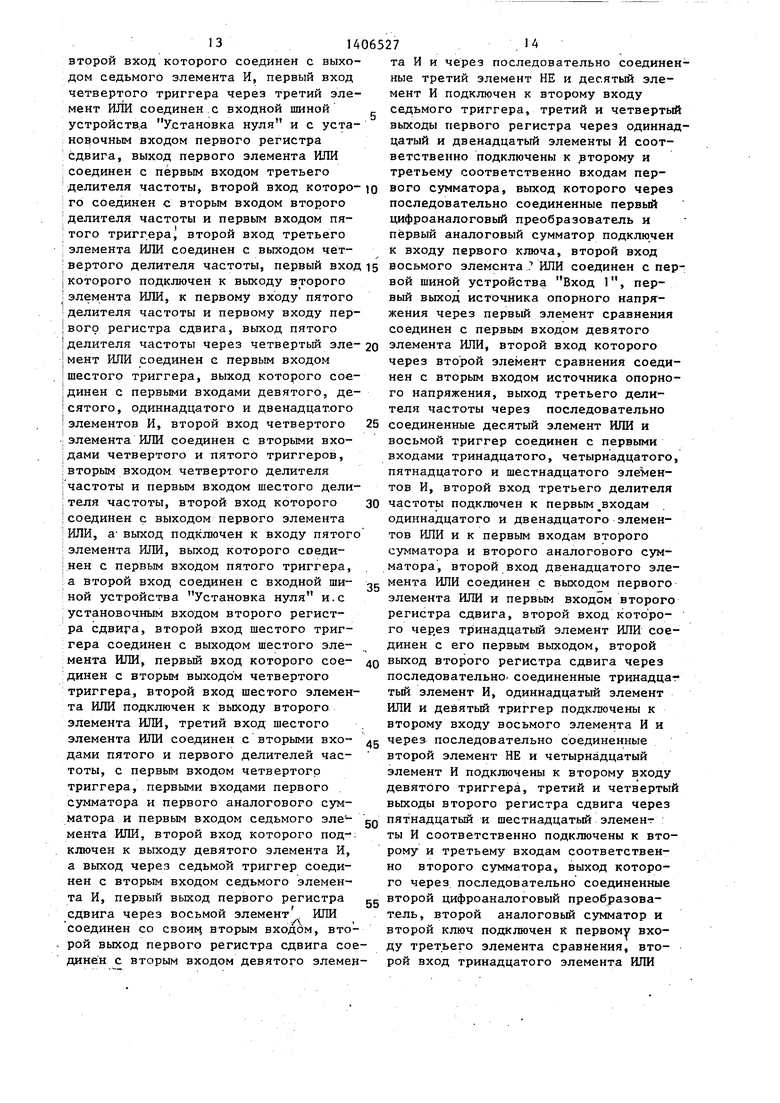

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - график формирова- |ния сигнала по его цифровой аппрокси |мации; на фиг. 3 - эпюры контроли- |руемого и допусковых сигналов для трех вариантов результатов контроля.

Устройство содержит тактовый гене |ратор I, первый элемент И 2, первый Делитель 3 частоты, второй элемент |И 4, второй делитель 5 частоты, пер- |вый триггер 6, третий элемент И 7, второй триггер 8, четвертый элемент |и 9, первый элемент ИЛИ 10, третий целитель 1 частоты, второй элемент ИЛИ 12, третий, элемент ИЛИ 13, чет- Ьертьй делитель 14 частоты, пятый Целитель 15 частоты, четвертый элемент ИЛИ 16, третий триггер 17, пятый элемент ИЛИ 18, шестой делитель 19 частоты, шестой элемент ИЛИ 20, седьмой элемент ИЛИ 21, четвертый триггер 22, входную шину 23 устройст иа Установка нуля, пятый элемент 1 24, первый регистр 25 сдвига, пер- иый элемент НЕ 26, шестой элемент li 27, седьмой элемент И 28, восьмой элемент И 29, последовательно соединенные первый сумматор 30, первый цифроаналоговый преобразователь 31, 1ервый аналоговый сумматор 32 и первый ключ 33,восьмой элемент ИЛИ 34j Первую 35, вторую 36 и третью 37 ши- Иы устройства Вход 1, Вход 2 и Вход 3 соответственно, первый элемент 38 сравнения, второй элемент 39 Сравнения, источник 40 опорного на- йряжения, девятый элемент ИЛИ 41, девятый элемент ИЛИ 42, пятый триггер 43, одиннадцатый элемент ИЛИ 44, шестой триггер 45, двенадцатый элемент ИЛИ 46, девятый элемент И 47, второй регистр 48 сдвига, второй элемент НЕ 49, подключенные-к триггеру 45 Десятый элемент И 50, одиннадцатый элемент И 51, двенадцатьш элемент И 52, последовательно соединенные Йторой цифроанало овый преобразова- fenb 54, второй аналоговый сумматор 55 и второй ключ 56, тринадцатый эле

0

5

0

5

0

5

0

5

0

5

мент ИЛИ 57, третий ключ 58, седьмой триггер 59, тринадцатый элемент И 60, третий элемент 61 сравнения, четвертый элемент 62 сравнения, последовательно соединенные элемент 63 дифференцирования и элемент .64 односторонней проводимости, четырнадцатый эле- мент ИЛИ 65, пятнадцатый элемент ИЛИ 66, шестнадцатый элемент ИЛИ 67, четырнадцатый, пятнадцатый и шестнадцатый элементы И 68, 69 и 70, восьмой, девятый и десятый триггеры 71, 72 и 73, семнадцатый элемент ИЛИ 74, семнадцатьй элемент И 75, третий элемент НЕ 7.6, первьш индикатор 77, второй индикатор 78, третий индикатор 79, четвертый элемент НЕ 80.

Устройство работает следующим образом.

С первого выхода источника опорного 40 напряжения на первый вход первого элемента 38 сравнения подается напряжения, равное U() , а с второго выхода - на второй вход второй элемента 39 сравнения напряжение равное U(4.j ид /2.

В начальный момент времени на шину 23 Установка нуля подается единичный импульс, который переводит в нулевое состояние первый 25 и второй 48 регистры сдвига, через третий элемент ИЛИ 13т- четвертый триггер 22, первый 3 и пятый 15 делители частоты, первый аналоговый сумматор 32 и первьй сумматор 30 через третий 13 и шестой 20 элементы ИЛИ - шестой триггер 45, через третей 13 и седьмой 21 элементы ИЛИ - седьмой триггер 59, через пятый элемент ИЛИ 18 - пятый триггер 43, второй 5 и третий II делители частоты, второй сумматор 53 и второй аналоговый сумматор 55, через пятый 18 и двенадцатый 46 элементы ИЛИ - восьмой триггер 71, через пятый 18 и одиннадцатый 44 элементы ШШ - де- в ятьй триггер 72, .через шестнадцатый элемент ИЛИ 67 - первый 6, второй 8 и третий 17 триггеры. Напряжение логической единицы с вторых выходов четвертого 22 и пятого 43 триггеров поступает соответственно на второй и третий входы семнадцатого элемента И 75, на первьш вход которого поступает напряжение логической единицы с выхода четвертого элемента НЕ 80., (так как на шине Вход 3 присутствует нулевое напряжение и соответственно на выходах первого 38 и второго 39 элементов сравнения - напряжение логического нуля, на выходе десятого элемента ИЛИ 41 также напряжение логического нуля, которое поступает на вход четвертого элемента НЕ 80), поэтому на его выходе появится напряжение .логической единицы, которое переводит десятый триггер 73 в- состояние логического нуля.

Напряжения логического нуля с первых выходов четвертого 6 и пятого 8 триггеров поступают на вторые входы соответственно пятого 24 и шестого 27 элементов И, тем самым запрещая про- хождение на их выходы тактовых импульсов с выхода тактового генератора 1 .

Напряжение логического нуля с первого выхода десятого триггера 73 по- ступает на управляющие входы первого 33, второго 56 и третьего 58 ключей, закрывая, их.

В следующий момент времени на шину 35 Вход 1 и шину 36 Вход 2 поступает информация в виде нулей и единиц, характеризующая форму контролируемого сигнала (фиг. 2).

Процесс контроля заключается в том, что предварите льно задаются две двоичные п-разрядные цифровые последовательности кода, несущие информа

5

5

0

цию о форме контролируемого сигнала, причем первая из них в максимально допустимом значении контролируемого сигнала, а вторая - о предельном уменьшении его, т.е. разница между ними образует поле допуска на сигнал. На фиг. 2 показан график, поясняющий принцип предварительного составления последовательностей. Вся последова-. тельность разбивается на триады. Первый разряд каждой триады содержит информацию о сдвиге по оси времени (t), причем единица в этом разряде свидетельствует о сдвиге.на один щаг) ноль - о том, что сдвига нет и содер- жание второго и третьего разряда данной триады относится не к следующему, а к текущему шагу т.е. имеет место сдвиг на один щаг только по оси уровня (и). Второй и третий разряды триад содержат информацию о характере сдвига по U, а именно: состояние 10 в этих разрядах говорит об одношаговом приращении по U относительно предьщу- щего щага, 01 - однощаговом уменьшении по и относительно предьщущего шага и 00 - отсутствии изменения по U относительно предьщущего шага. Таким образом, цифровая последовательность кода сигнала, представленного - фиг. 2, имеет вид:

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1986 |

|

SU1451857A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Формирователь сигналов произвольной формы | 1987 |

|

SU1465956A1 |

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Устройство для контроля и регулирования параметров | 1984 |

|

SU1249491A1 |

| Устройство для деления в избыточном коде | 1984 |

|

SU1280612A1 |

| СПОСОБ ИЗМЕРЕНИЯ СРЕДНЕЙ ЧАСТОТЫ МОРСКИХ ВОЛН | 2007 |

|

RU2337313C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Параболический интерполятор | 1984 |

|

SU1160370A1 |

| Система записи и воспроизведения видеосигнала | 1990 |

|

SU1783635A1 |

Изобретение может быть использовано для автоматического контроля сигналов произвольной формы в сложных системах контроля и управления технологическими процессами. Устройство „Устамв- канупк Sxodi Bxodi , вхо&З о содержит элементы НЕ 26, 49, 76,80, элементы И 2,4,7,24,27,29,47,50-52, 60,68-70, 75, индикаторы 77-79, триггеры 6,8,9,17 22,43,45,59,71-73, так-- товый генератор 1, делители 3,5,11, 14,15,19 частоты, элементы ИЛИ 10,12, 13,16,18,20,21,34,41,42,44,46,57,65- 67,74, регистры 25, 48 сдвига, сумматоры 30, 53, аналоговые сумматоры 32, 55, ключи 33, 56, 58, элементы 38,39,61,62 сравнения, цифроаналого- вые преобразователи 31, 54, источник 40 опорного напряжения, элемент 63 дифференцирования и элемент 64 односторонней проводимости. Устройство имеет повышенную достоверность контроля. 3 ил. i (Л ел

.100 110 по 010 по 010 010 010 110 010 по 100 101 101 100 по 100 100 101 001 001 101 001 001 001 100 101 100 101 100.

(На фиг.2 обозначена под осью t в виде триад для каждого сдвига по t). Данным путем для каждого контролируемого сигнала составляются по две цифровые последовательности аппроксимирующие минимальные и макси- маЛные допустимые значения контролируемого сигнала. Поступив соответственно на вторые входы восьмого 34 и тринадцатого 57 элементов ИЛИ, она далее поступает на вторые входы соответственно первого 25 и второго 48 регистров сдвига и записывается в них. При этом в первый регистр 25 сдвига записьюается информация о. минимально допустимом значении контролируемого сигнала, а во второй ре гистр 48 сдвига - о максимально до- пустимом значении контролируемого сигнала.

После этого устройство готово для контроля сигнала. Контролируемый сигнал подается на шину 37 Вход 3. Он поступает на вторые входы первого и второго элементов 38 и 39 сравнения. Когда величина амплитуды контролируемого сигнала станет больше по абсолютной величине значения (если значение амплитуды сигнала больше и.,/2, то на выходе второго

элемента 39 сравнения появится напряжение логической единицы, если значение амплитуды сигнала меньше , то на выходе первого элемента 38 сравнения появится напряжение логической единицы). В зависимости от того каким является значение величины амплитуды контролируемого сигнала отрицательным или положительным, на выводах соответственно первого 38 или

второго 39 элементов сравнения появится напряжение логической единицы которое поступает соответственно на первый или второй входы д,евятого элемента ИЛИ 41. Напряжение логической единицы с выхода девято го элемента ИЛИ 41 поступает на первый вход деся ;того триггера 73 и переводит его в I единичное состояние. Напряжение логи 1 ческой единицы с его выхода поступает на управляющие входы первого 33, :второго 56 и третьего 58 ключей, от- ;крывая их, и через элемент 63 диффе- ;ренцирования, например CR-фильтр, - на выход элемента 64 односторонней Iпроводимости, например диод, единич- |ный импульс с выхода которого уста- |навливает в нулевое состояние четвертый делитель 14 частоты и шестой делитель 19 частоты, в единичное состояние - четв ертый триггер 22 и пятый триггер 43, через четвертый эле- |мент ИЛИ 16 -шестой триггер 45 а. через десятый элемент ИЛИ 42 - восьмой триггер 71.

Напряжения логической единицы с вторых выходов четвертого 22 и пято- го 43 триггеров поступают на вторые |входы соответственно пятого 24 и Шестого 27 элементов И, разрешая тем Ьамым прохождение тактов1 1х импульсов |с выхода тактового генератора 1 . на HX выходы.

I Напряжения логической единицы с ыходов шестого 45 и восьмого 71 т;ри еров поступают на первые входы девя |гог6 47, десятого 50, одиннадцатого ,51, двенадцатого 52,. тринадцатого 60 четырнадцатого 68, пятнадцатого 69 и иестнадцатого 70 элементов И, ,разре- Ьая тем самым появление напряжения логического нуля или единицы на их выходах в зависимости от наличия напряжения логического нуля или единиц поступающих на их вторые входы.

Напряжения логического нуля или Единицы с выходов .одиннадцатого 51, двенадцатого 52, пятнадцатого 69 и Шестнадцатого 70 элементов И поступают на соответствующие суммирующий и вычитающий входы первого 30 и второго 53 сумматоров.

Содержимое первого 30 и второго 53 cjmMaторов с их выходов поступает соответственно на входы первого 31 и Второго 54 цифроаналоговых преобразователей. Напряжение на их выходах будет пропорционально содержимому

,

- ,

10

15

20

25

406527 6 ..

соответствующих сумматоров 30 и 53. Напряжение с выходов первого 31 и второго 54 цифроаналоговых преобразователей поступает на вторые входы соответственно первого 32 и второго 55 аналоговых сумматоров, далее их содержимое через первый 33 и второй 56 ключи поступает на второй вход четвертого элемента 62 сравнения и на первый вход третьего элемента 61 сравнения. На второй вход третьего элемента 61 сравнения и на первый вход четвертого элемента 62 сравнения поступает контролируемый сигнал с выхода третьего ключа 58.

Если контролируемый сигнал .находится в заданных пределах, то напря-- жение логической единицы будет присутствовать на втором или -первом выходе третьего элемента 61 сравнения и на первом- или втором выходе четвертого элемента 62 сравнения.; Эти напряжения логической единицы со-ответ- ственно через четырнадцатый 65 и пятнадцатый 66 элементы ИЛИ поступят на первьй и второй входы четвертого элемента И 9, напряжение логической единицы с выхода которого переведет третий триггер 17 в состояние логической единицы. Напряжение логической единицы с .его выхода через второй элемент И 4 поступит на вход первого индикатора 77 и засветит его, что будет соответствовать тому, что контролируе-- мый сигнал находится в заданных пределах, т.е. он в норме (фиг. За).

Ecj|H на третьем выходе: третьего элемента 61 сравнения появится напряжение логической единицы, т.е. контролируемый сигнал выше нормы, или на третьем выходе четвертого элемента 62 сравнения появится .напряжение логической единицы, т.е. контролируемый сигнал ниже нормы, то через третий 7 или первый 2 элементы И соответственно оно переведет в состояние логической единицы соответственно первьй 6 или второй 8 триггеры, так как на входах третьего 7 и первого 2 элементов И присутствует напряже ние ло- . гической единицы с выхода первого элемента Н.Е 26, поскольку первый 6 и второй 8 триггеры были в состоянии логической единицы.

Напряжение логической единицы с выхода первого 6 или второго 8 триг- геров поступает соответственно на второй 78 или третий 79 индикатор.

30

35

40

М5

50

55

засвечивая его. Это свидетельствует о том, что контролируемый сигнал выше или ниже нормы. Это же напряжение поступает через семнадцатый элемент ИЛИ 7 на вход первого эле- мента НЕ 26, напряжений логи ского нуля с выхода которого поступает на первый вход второго элемента И 4, запрещая отсветку первого индикатора 77 о том, что контролируемый сигнал в норме, и на второй и первый входы третьего 7 и первого 2 элементов И, запрещая перевод в единичное состояние первого 6 или второго 8 триггеров , которые находятся в состоянии логического нуля. В этом случае дальнейший контроль сигнала прекращается но формирование изменения верхнего и нижнего предела контролируемого сигнала во времени будет осуществлено полностью.

Устройство работает следующим. 66- разом.

Если на втором выходе первого 25 и второго 48 регистров сдвига напряжение логической единицы, т.е. в первом разряде триады записана логичесПервый импульс с выхода второго 12 .и первого 10 элементов ИЛИ через шестой 20 и двенадцатый 46 элементы Ш1И соответственно устанавливает шестой

кая единица, то на выходах соответственно девятого 47 и тринадцатого 60 30 45 и восьмой 71 триггеры в нулевое элементов И будет напряжение логичес-- состояние. Напряжение логического ну- кой единицы, состояния седьмого 59 ля с их выходов поступает на первые и девятого 72 триггеров не изменятся входы соответственно девятого 47, и напряжения логического нуля с выхо- . десятого 50, одиннадцатого 51, две- дов седьмого 59 и девятого 72 тригге- g надцатого 52, тринадцатого 60, четьф- ров поступают на вторые входы соответ- надцатого 68, пятнадцатого 69 и шест ственно седьмого 28 и восьмого 29 надцатого VO элементов И, на выходах элементов И, запрещая тем самым про- которых появится напряжение логичес- хождение на их выход тактовых импуль- кого нуля.

сов, поступающих на их первьй вход. 40 Импульсы с выходов второго 12 и Если же на вторых выходах первого первого 10 элементов ИЛИ поступают 25 и второго 48 регистров сдвига или у одного их них напряжение логического нуля, то на выходах десятого 50 и четырнадцатого 68 элементов И или од- 45 импульса осуществляется сдвиг содер- Hofo из них будет напряжение логичес- жимого регистров 25 и 48 на один раз- кой единицы, которое переводит соот- . ряд, причем информация старших разря- ветственно седьмой 28 и девятый 72 дов с первых их выходов через восьмой триггеры или один их них в единичное 3 и тринадцатый 57 элементы ИЛИ за- состояние. Напряжение логической еди- gg писывается в младшие разряды, ницы с выходов седьмого 28 и девятого . С выходов второго 12 и первого 10

также на первый сдвигающий вход первого 25 и второго 48 регистров сдвига соответственно. Под действием каждого

72 триггеров или одного из них поступает на вторые входы седьмого 28 и восьмого 29 элементов И или одного

из них, разрешая тем самым прохожде- gg тоты. Их коэффициент деления равен

трем. После того, как третьи импуль поступят на их первые входы, на их выходах появляется импульс,, который переводит соответственно шестой 45

ние на их вькод тактовых импульсов, поступающих на первый вход обоих элементов И 28 и 29 или одного из них. Тактовые импульсы с выходов пятого

24 и шестого 27 элементов И поступают на первые входы соответственно седьмого элемента И 28, первого дели-. уеля 3 частоты и восьмого элемента И 29 и второго делителя 5 частоты.

Если на выходе седьмого 28 и восьмого 29 элементов И или одного из них присутствует напряжение логической единицы, то на выходе второго 12 иди первого 10 элементов ИЛИ или одного из них появятся импульсы с частотой тактового генератора 1.

Если на выходе седьмого 28 и вось- мого 29 элементов И или одного из них напряжение логического нуля, то на вых оде второго 12 и первого 10 элементов ШШ или одного из них появляются импульсы с частотой в п раз меньшей частоты тактового генератора 1. Частота следования импульсов бу- дет определяться коэффициентом деле- ния первого 3 и второго 5 делителей частоты или одного из них. Их коэффи- циент деления равен п.

Первый импульс с выхода второго 12 .и первого 10 элементов ИЛИ через шестой 20 и двенадцатый 46 элементы Ш1И соответственно устанавливает шестой

45 и восьмой 71 триггеры в нулевое состояние. Напряжение логического ну- ля с их выходов поступает на первые входы соответственно девятого 47, десятого 50, одиннадцатого 51, две- надцатого 52, тринадцатого 60, четьф- надцатого 68, пятнадцатого 69 и шест надцатого VO элементов И, на выходах которых появится напряжение логичес- кого нуля.

Импульсы с выходов второго 12 и первого 10 элементов ИЛИ поступают импульса осуществляется сдвиг содер- жимого регистров 25 и 48 на один раз- ряд, причем информация старших разря- дов с первых их выходов через восьмой 3 и тринадцатый 57 элементы ИЛИ за- писывается в младшие разряды, С выходов второго 12 и первого 10

также на первый сдвигающий вход первого 25 и второго 48 регистров сдвига соответственно. Под действием каждого

элементов ИЛИ.импульсы поступают также на первые входы соответственно пяг того 15 и третьего 11 делителей часттоты. Их коэффициент деления равен

трем. После того, как третьи импульсы поступят на их первые входы, на их выходах появляется импульс,, который переводит соответственно шестой 45

и восьмой 71 триггеры в единичное состояние. В этот момент времени в трех старших разрядах первого 25 и второго 48 регистров сдвига будут вторые триады заданных последователь- ностей допусковых сигналов. i. Напряжения логической единицы с выходов шестого 45 и восьмого 71 |триггеров поступают на первые входы Девятого 47, десятого 50, одиннадцатого 51, двенадцатого.52, тринадца- JToro 60, четырнадцатого 68, пятнадца- JToro 69 и шестнадцатого 70 элементов

и на первом или втором выходе четвертого элемента 62 сравнения. Эти напряжения логической единицы соответст- с венно через четырнадцатый 65 ff пятнадцатый 66 элементы ИЛИ поступят соответственно на первый и второй входы четвертого элемента И , напряжение логической единицы с выхода ко- 10 торого поступает на первый вход третьего триггера 17. Если триггер 17 бьш в нулевом состоянии, т.е. в предшествующее время контроля сигнал выходил за пределы нормы, то он переИ, разрешая тем самым появление на- 15 водится в единичное состояние, но

отсветки ,на индикаторе 77 не будет, так как на первом входе второго элемента И 4 будет напряжение логического нуля. Если триггер 17 был в еди- 20 начнем состоянии, то его состояние не изменится и на индикаторе 77 будет отсветка о том, что сигнал находится в заданных пределах.

Если на третьем выходе третьего

пряжения логического нуля или, единицы на их выходах в зависимости от наличия напряжения логического нуля или.единицы, поступающего на их вторые входы.

Напряжения логичес кого нуля или единицы с выходов одиннадцатого 51 и двенадцатого 52, пятнадцатого 59 и шестнадцатого 70 элементов И поступают на соответствующие суммирующие 25 элемента 61 сравнения появится напряди вычитающие входы соответственно жение логической единицы, т.е. конт- |первого 30 и второго 53 сумматоров. ; Содержимое первого 30 и второго 53 сумматоров в зависимости от того, |что поступило на их суммирующие и вычитающие входы, изменяется или ос- ;Тается неизменным. Далее напряжение |с их выходов поступает соответствен- :Но на входы первого 31 и второго 54 |цифроаналоговьгх преобразователей. или второй 8 триггеры, если до этого |пряжение на их выходах будет пропор- момента контролируемый сигнал нахо- ционально содержимому соответствующих сумматоров 30 и 53. Напряжение с выходов первого 31 и второго 54 цифро.ролируемый сигнал выше нормы, или на третьем выходе четвертого элемента 62 сравнения появится напряжение логи- 30 ческой единицы, т.е. контролируемый сигнал ниже нормы, то оно переведет в состояние логической единицы соответственно через третий 7 или первый 2 элементы И соответственно первый 6

дился в заданных пределах. Если один из триггеров 6 или 8 находится в состоянии логической единицы, то их

аналоговьпс преобразователей поступает 40 состояние не изменится, так как на

на первые входы соответственно первого 32 и второго 55 аналоговых сумматоров , где суммируется с содержимым, находящимся в них,, и далее их

содержимое через соответственно пер- 45 выхода первого 6 или второго 8. тригвый 33 и второй 56 ключи поступает соответственно на второй вход четвертого элемента 62 сравнения и на первый вход третьего элемента 61 сравнегеров поступает на соответствующие индикаторы 78 или 79, засвечивая; один из них, причем на первом индикаторе 77 будет запрещена отсветка о норме

ния. На второй вход третьего элемен га gQ контролируемого сигнала. (фиг.Зб и в). 61 сравнения и на первьй вход четвер- Далее устройство работает по опитого элемента 62 сравнения поступает . санному алгоритму до тех пор, пока

контролируемый сигнал с выхода .третьего ключа 58.

Если контролируемый сигнал находится в заданных пределах, то напряжение логической eдиницы будет при сутствовать на втором или первом выходе третьего элемента 61 сравнения

отсветки ,на индикаторе 77 не будет, так как на первом входе второго элемента И 4 будет напряжение логического нуля. Если триггер 17 был в еди- 20 начнем состоянии, то его состояние не изменится и на индикаторе 77 будет отсветка о том, что сигнал находится в заданных пределах.

Если на третьем выходе третьего

25 элемента 61 сравнения появится напря жение логической единицы, т.е. конт- д или второй 8 триггеры, если до этого момента контролируемый сигнал нахо-

элемента 61 сравнения появится напряжение логической единицы, т.е. конт- или второй 8 триггеры, если до этого момента контролируемый сигнал нахо-

ролируемый сигнал выше нормы, или на третьем выходе четвертого элемента 62 сравнения появится напряжение логи- ческой единицы, т.е. контролируемый сигнал ниже нормы, то оно переведет в состояние логической единицы соответственно через третий 7 или первый 2 элементы И соответственно первый 6

элемента 61 сравнения появится напряжение логической единицы, т.е. конт- или второй 8 триггеры, если до этого момента контролируемый сигнал нахо-

дился в заданных пределах. Если один из триггеров 6 или 8 находится в состоянии логической единицы, то их

первых входах третьего 7 и первого 2 элементов И - напряжение логического нуля.

Напряжение логической единицы с

геров поступает на соответствующие индикаторы 78 или 79, засвечивая; один из них, причем на первом индикаторе 77 будет запрещена отсветка о норме

на выходах четвертого 14 и шестого 19 делителей частоты не появятся единич- gg ные импульсы, которые свидетельствуют о том,что содержимое в первом 25 и втором 48 регистрах сдвига совершило полный цикл. Эти единичные импульсы через третий.13 и пятый 18 элементы

ИЛИ переводят в нулевое состояние соответственно четвертый 22 и пятый 43 триггеры, первьй 3 и второй ,5 делители частоты, шестой 4.5 и восьмой 71 триггеры, седьмой 59 и девятый 72 триггеры.

Напряжения логической единицы с выходов четвертого 22 и пятого 43 - триггеров поступают соответственно на второй и третий входы семнадцатого элемента И 75, на первый вход которого поступает напряжение логической единицы с выхода четвертого элемента НЕ 80, так как контролируемый сигнал на шине 37 Вход 3 отсутствует, т.е. напряжение меньще по абсолютной величине 11,,/2. Напряжение логической единицы с выхода семнадцатого элемента И 75 поступает на второй вход десятого триггера 73, который.переводится в нулевое состояние Напряжение логического нуля с его выхода поступает на управляющие входы первого 33, второго 56 и третьего 58 ключей, за- крьшая их.

. . На этом работа устройства заканчивается.

Если за время контроля сигнала контролируемый сигнал хоть раз выходил за пределы допуска, то на втором 78 или третьем 79 индикаторах осуще- ствлена соответствующая засветка (причем засветка будет на втором индикаторе 78, если контролируемьй сиг- нал сначала превьшал заданньй предел изменения, и на третьем индикаторе 79 если контролируемый сигнал сначала бьщ меньше:заданного предела изменения) .

Если контролируемый сигнал за время контроля изменялся в. заданных пределах, то засветится индикатор 77, свидетельствующий о норме контролит- руемого сигнала,

Дпя контроля сигналов той же формы, что и предыдущий, они подаются последовательно на шину 37- Вход 3.

Если необходим контроль сигналов другой формы, то на шину 23 Установка нуля подается единичный импульс, затем на шины 35 и 36 Вход .1 и Вход 2 подаются последовательности, характеризующие пределы измене

ния контролируемого сигнала,, кот.орые через восьмой и тринадцатьш элементы ИЛИ 34-и 57 записьтаются соответственно в первый 25 и второй 48 регистры сдвига. Далее на шину 37 Вход 3

подается контролируемый сигнал и -устройство начинает работать по описанному алгоритму.

Таким образом, предлагаемое устройство позволяет контролировать сигналы произвольной формы без- использования для каждого контролируемого сигнала своего эталонного -четырехполюсника с заданным законом изменения сигнала, что. обеспечивает его универсальность..Формула

изобретения

0

Q 5

. g

0

Устройство для контроля сигналов произвольной формы, содержащее первый элемент НЕ, выход которого соеди-- нен с первыми входами первого и второго элементов И, выход второго элемента И соединен с входом первого индикатора, .третий элемент И,.выход которого .че.рез первый триггер соединен с входом второго индикатора, вы5 ход первого элемента И через второй

триггер соединен с входом третьего .индикатора, четвертый элемент И, выход которого соединен с первым входом третьего триггера, и второй элемент НЕ, отличающееся тем, что, с целью повьш1ения достоверности контроля, в него введещл тактовый генератор, шесть делителей частоты, семь триггеров, семнадцать элементов ИЛИ, два элемента НЕ, тринадцать элементов И, два р,егистра -сдвига, два сумматора, два цифроаналого- вых преобразователя, два аналоговых сумматора, два ключа, четыре элемента сравнения, источник опорного напряжения, элемент дифференцирования и элемент одностронней проводимости, . при это м вькод тактового генератора соединен с первыми входами пятого и

5 шестого элементов И, второй вход которых соединен с первым выходом четвертого и пятого триггеров соответ- .ственно, выход пятого элемента И соединен с первым входом седьмого.элемента И и первым входом первого делителя частоты, выход шестого элемента И соединен с первым входом восьмого элемента И и первым входом второго делителя частоты, выход которого соеди-. нен с первым входом первого элемента ИЛИ, второй вход-последнего подключен к выходу восьмого элемента И, выход первого делителя частоты соединен с первым входом второго элемента. ИЛИ,

0

0

55

второй вход которого соединен с выходом седьмого элемента И, первый вход четвертого триггера через третий элемент ИЛИ соединен.с входной шиной устройств.а Установка нуля и с установочным входом первого регистра сдвига, выход первого элемента ИЛИ соединен с первым входом третьего делителя частоты, второй вход которо- го соединен с вторым входом второго делителя частоты и первым входом пятого триггера, второй вход третьего элемента ИЛИ соединен с выходом четвертого делителя частоты, первый вход которого подключен к выходу второго элемента ИЛИ, к первому входу пятого делителя частоты и первому входу первого регистра сдвига, выход пятого делителя частоты через четвертый эле- мент ИЛИ соединен с первым входом шестого триггера, выход которого соединен с первыми входами девятого, десятого, одиннадцатого и двенадцатого элементов И, второй вход четвертого элемента ИЛИ соединен с вторыми входами четвертого и пятого триггеров, вторым входом четвертого делителя частоты и первым входом шестого делителя частоты, второй вход которого соединен с выходом первого элемента ИЛИ, а- выход подключен к входу пятого элемента ИЛИ, вьпсод которого соединен с первым входом пятого триггера, а второй вход соединен с входной ши- ной устройства Установка нуля и.с установочным входом второго регистра сдвига, второй вход шестого триггера соединен с выходом шестого элемента ИЛИ, первый вход которого сое- динен с вторым выходом четвертого триггера, второй вход шестого элемента ИЛИ подключен к выходу второго элемента ИЛИ, третий вход шестого элемента ИЛИ соединен с вторыми вхо- дами пятого и первого делителей час- тоты, с первым входом четвертого триггера, первьми входами первого сумматора и первого аналогового сумматора и первым входом седьмого эле- мента ШШ, второй вход которого подключен к выходу девятого элемента И, а выход через седьмой триггер соединен с вторым входом седьмого элемента И, первый выход первого регистра сдвига через восьмой элемент . ИЛИ соединен со свои вторым входом, второй выход первого регистра сдвига сое дине н с вторым входом девятого элемента И и через последовательно соединенные третий элемент НЕ и десятый элемент И подключен к второму входу седьмого триггера, третий и четвертый выходы первого регистра через одиннадцатый и двенадцатый элементы И соответственно подключены к рторому и третьему соответственно входам первого сумматора, выход которого через последовательно соединенные первый цифроаналоговый преобразователь и первый аналоговый сумматор подключен к входу первого ключа, второй вход восьмого элемента ИЛИ соединен с пер вой шиной устройства Вход 1, первый выход источника опорного напря - жения через первый элемент сравнения соединен с первым входом девятого элемента ИЛИ, второй вход которого через второй элемент сравнения соединен с вторым входом источника опорного напряжения, выход третьего делителя частоты через последовательно соединенные десятый элемент ИЛИ и восьмой триггер соединен с первыми входами тринадцатого, четырнадцатого, пятнадцатого и шестнадцатого тов И, второй вход третьего делителя частоты подключен к первым входам одиннадцатого и двенадцатого элементов ИЛИ и к первым входам второго сумматора и второго аналогового сумматора, второй вход двенадцатого элемента ИЛИ соединен с выходом первого элемента ИЛИ и первым входам второго регистра сдвига, второй вход которого через тринадцатый элемент ИЛИ соединен с его первым выходом, второй выход второго регистра сдвига через последовательно, соединенные тринадцаг тый элемент И, одиннадцатый элемент ИЛИ и девятый триггер подключены к второму входу восьмого элемента И и через последовательно соединенные второй элемент НЕ и четырнадцатый элемент И подключены к второму входу девятого триггера, третий и четвертый выходы второго регистра сдвига через пятнадцатый и шестнадцатый элемент ; ты И соответственно подключены к второму и третьему входам соответственно второго сумматора, выход которого через последовательно соединенные второй цифроаналоговый преобразователь, второй аналоговый сумматор и второй ключ подключен к первому входу третьего элемента сравнения, второй вход тринадцатого элемента ИЛИ

15

соединен с второй шиной устройства Вход 2, третья шина которого соединена с вторыми входами первого и второго элементов сравнения и через третий ключ с вторым входом третьего элемента сравнения и с первым входом четвертого элемента сравнения, второй Bxoff которого подклюг чен к выходу первого ключа, первый и второй выходы третьего элемента сравнения через четырнадцатый элемент ИЛИ соединены с первым входом четвертого элемента И, второй вход которого через пятнадцатый элемент ИЛИ соединен с первым и BTOpbw выходами четвертого элемента сравнения, третий выход третьего элемента сравнения соединен с первым входом третьего элемента И, второй вход которого соединен с первым входом первого элемента И, третий выход Четвертого элемента сравнения соединен с вторым входом первого элемента И, выход девятого элемента ИЛИ соединен с первым входом десятого триггера и через последовательно соединенные , четвертый элемент НЕ и семнадцатый элемент И подключен к второU

му входу десятого триггера, выход ко100 т ffo 110 110 110 100 т ioi тт т т ioi wi т ioi wo wt wo

010 010 Q1Q OQ1 0€1

010001 001

010001

Фиг. 2

0652716

торого соединен с управляющими входами первого, второго и третьего ключей и через последовательно соединенные элемент дифференцирования и элемент односторонней проводимости с первым входом шестнадцатого элемента-ИЛИ, с первым входом шестого делителя частоты и с выходом десятого элемента ИЛИ,

.Q второй вход семнадцатого элемента И соединен ,; с выходом четвертого триггера, третий вход семнадцатого элемента И соединен с вторым выходом пятого триггера и входом двенадцатого

5 элемента ИЛИ, второй вход шестнадцатого элемента ИЛИ соединен с входной шиной устройства Установка нуля, . а выход подключен к вторым входам первого, второго и третьего тригге20 ров, выход семнадцатого элемента ИЛИ соединен с входом первого элемента НЕ, первый и второй входы подключены к выходам первого и второго триггеров соответственно, выход третьего

25 триггера соединен с вторым входом

второго элемента И, а выход двенадцатого элемента ИЛИ подключен к второму входу восьмого триггера.

U(i)

a .

i/(t)A -S

Фие.г

| Устройство для допускового контроля амплитудно-частотной характеристики четырехполюсников | 1982 |

|

SU1101760A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-06-30—Публикация

1986-12-16—Подача