40

Примечание

тельный код в); - произвольное состояние.

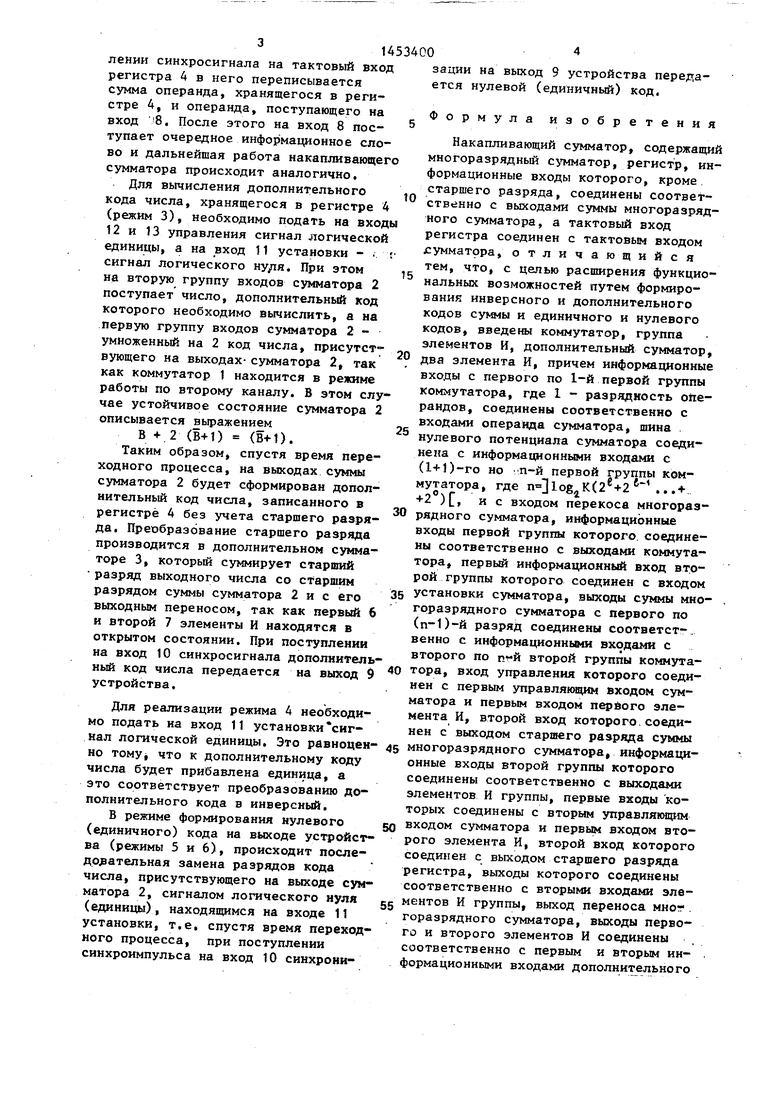

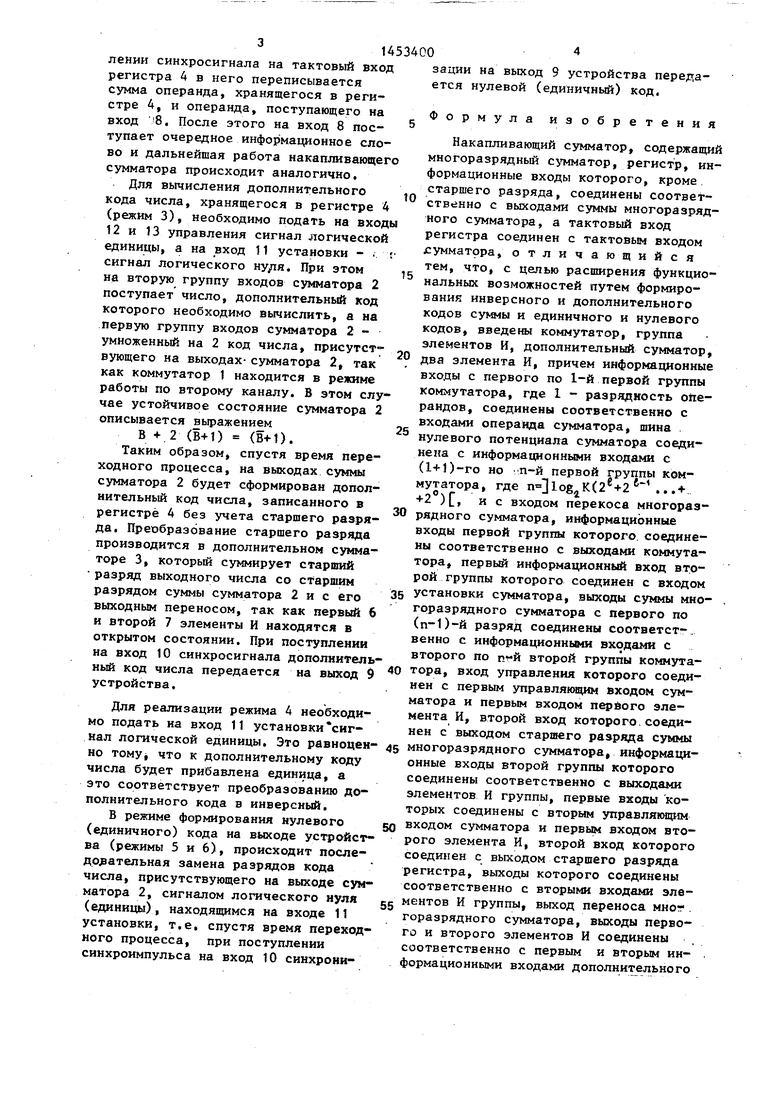

Если на входах 12 и 13 управления присутствует сигнал логического нуля, то накапливающий сумматор работает в режиме передачи информации, поступающей на вход 8 и на вьпсод 9 без изг

ления - сигнал логической единицы. Состояние сигнала на входе 11 установки - произвольное. В этом режиме коммутатор 1 работает по первому каналу, а группа элементов И 5 разблокируется сигналом логической единицы, поступающим на его вторые входы с входа 13 управления, и пропускает на вторую группу входов сумматора 2 число, записанное в регистре 4, кроме старщего разряда. Сумматор 2 производит сложение П-разрядных операндов и передает результат на В(§+1 -дополни-50 информационные входы регистра 4.

В - информация на выходе устройства; а; - i-fi входное слог во; В - инверсия

45

55

Старший, (П-И)-й, разряд суммы вычисляется путем сложения в дополнительном сумматоре 3 сигнала с выхода переноса сумматора 2 и старшего разряда числа, записанного в регистре 4 и поступающего через открытый сигналом логической единицы второй элемент И 7 на вход переноса дополнительного сумматора 3. При поступления - сигнал логической единицы. Состояние сигнала на входе 11 установки - произвольное. В этом режиме коммутатор 1 работает по первому каналу, а группа элементов И 5 разблокируется сигналом логической единицы, поступающим на его вторые входы с входа 13 управления, и пропускает на вторую группу входов сумматора 2 число, записанное в регистре 4, кроме старщего разряда. Сумматор 2 производит сложение П-разрядных операндов и передает результат на 0 информационные входы регистра 4.

5

Старший, (П-И)-й, разряд суммы вычисляется путем сложения в дополнительном сумматоре 3 сигнала с выхода переноса сумматора 2 и старшего разряда числа, записанного в регистре 4 и поступающего через открытый сигналом логической единицы второй элемент И 7 на вход переноса дополнительного сумматора 3. При поступлении синхросигнала на тактовый вход регистра 4 в него переписывается сумма операнда, хранящегося в регистре А, и операнда, поступающего на вход 8. После этого на вход 8 поступает очередное информационное слово и дальнейшая работа накапливающего сумматора происходит аналогично.

Для вычисления дополнительного кода числа, хранящегося в регистре 4 (режим 3), необходимо подать на входы 1 и 13 управления сигнал логической единицы, а на вход 11 установки - . сигнал логического ну/гя. При этом на вторую группу входов сумматора 2 поступает число, дополнительный код которого необходимо вычислить, а на первую группу входов сумматора 2 - умноженный на 2 код числа, присутствующего на выходах-сумматора 2, так как коммутатор 1 находится в режиме работы по второму каналу. В этом случае устойчивое состояние сумматора 2 описывается выражением

В 4-2 (В+1) (в+1). Таким образом, спустя время переходного процесса, на выходах суммы сумматора 2 будет сформирован дополнительный код числа, записанного в

1453400

зации на выход 9 устройства передается нулевой (единичный) код.

5 Формула изобретения

Накапливающий сумматор, содержащий многоразрядный сугтатор, регистр, информационные входы которого, кроме старшего разряда, соединены соответственно с выходами суммы многоразрядного сумматора, а тактовый вход регистра соединен с тактовым входом сумматора, отличающийся g тем, что, с целью расширения функциональных возможностей путем формирования инверсного и дополнительного кодов СУМ4Ы и единичного и нулевого кодов, введены коммутатор, группа элементов И, дополнительный сумматор, два элемента И, причем информационные входы с первого по 1-й первой группы коммутатора, где 1 - разрядность операндов, соединены соответственно с 2 входами операнда сумматора, шина нулевого потенциала сумматора соединена с информационными входами с (1+1)-го но П-й первой группы ком1 - - О 4

- - -, .... „ IJJyilHD

мутатора, где К(

2°),

...+

и с

входом перекоса многораз- - ----- V 4 Ч/ а л. г - - мни г о

регистре 4 без учета старшего разря- Рядного сумматора, ннформациЬнные пя. Ппо««„,, входы первой группы которого соединены соответственно с выходами коммутатора, первый информационный вход второй группы которого соединен с входом 35 установки сумматора, выходы суммы многоразрядного сумматора с первого по (п-1)-й разряд соединены соответст-. венно с информационнь ш входами с второго по п-й второй группы коммута- 40 тора, вход управления которого соединен с первым управляющим входом сумматора и первым входом элемента И, второй вход которого соединал логической единиц Гэт Гр вн ен- ° ° старшего разряда суммы но тому, что к дополни;ел1номГкопГ ««° °Р РяДного сумматора, информаци- -сла будет прибавлена :диница ,Г ..°« ° Р «-°Р°- это соответствует преобразованию дополнительного кода в инверсный.

В режиме формирования нулевого сп (единичного) кода на выходе устройст- ва (режимы 5 и 6), происходит последовательная замена разрядов кода числа, присутствующего на выходе сумматора 2, сигналом логического нуля (единицы), находящимся на входе 11

- ... . « J 4/ Ю-1/Л

да. Преобразование старшего разряда производится в дополнительном сумматоре 3, который сумчирует старший разряд выходного числа со старшим разрядом суммы сумматора 2 и с его выходным переносом, так как первый б и второй 7 элементы И находятся в открытом состоянии. При поступлении на вход 10 синхросигнала дополнительный код числа передается на выход $ устройства.

Для реализации режима 4 необходимо подать на вход 11 установки сигустановки, т.е. спустя время переходного процесса, при поступлении синхроимпульса на вход 10 синхронисоединены соответственно с выходами элементов И группы, первые входы которых соединены с вторым управляющим входом сумматора и первым входом второго элемента И, второй вход которого соединен с выходом старшего разряда регистра, выходы которого соединены соответственно с вторыми входами эле- 55 ментов И группы, выход переноса мног горазрядного сумматора, выходы первого и второго элементов И соединены соответственно с первым и вторым информационными входами дополнительного

од го

1453400

зации на выход 9 устройства передается нулевой (единичный) код.

5 Формула изобретения

Накапливающий сумматор, содержащий многоразрядный сугтатор, регистр, информационные входы которого, кроме старшего разряда, соединены соответственно с выходами суммы многоразрядного сумматора, а тактовый вход регистра соединен с тактовым входом сумматора, отличающийся g тем, что, с целью расширения функциональных возможностей путем формирования инверсного и дополнительного кодов СУМ4Ы и единичного и нулевого кодов, введены коммутатор, группа элементов И, дополнительный сумматор, два элемента И, причем информационные входы с первого по 1-й первой группы коммутатора, где 1 - разрядность операндов, соединены соответственно с входами операнда сумматора, шина нулевого потенциала сумматора соединена с информационными входами с (1+1)-го но П-й первой группы ком1 - - О 4

- - -, .... „ IJJyilHD

мутатора, где К(

2°),

...+

и с

входом перекоса многораз л. г - - мни г о

Рядного сумматора, ннформациЬнные входы первой группы которого соедине ° ° старшего разряда суммы ««° °Р РяДного сумматора, информаци- ..°« ° Р «-°Р°-

соединены соответственно с выходами элементов И группы, первые входы которых соединены с вторым управляющим входом сумматора и первым входом второго элемента И, второй вход которого соединен с выходом старшего разряда регистра, выходы которого соединены соответственно с вторыми входами эле- ментов И группы, выход переноса мног горазрядного сумматора, выходы первого и второго элементов И соединены соответственно с первым и вторым инормационными входами дополнительного

51453400

гистоа. выходы регистра соединены

суьшатора и входом его переноса, вы- с вькодами результата ход суммы дополнительного сумматора соответственно соединен с входом старшего разряда ре- сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Последовательный сумматор | 1989 |

|

SU1633392A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения состоит в расширении функциональных возможностей путем формирования инверсного и дополнительного кодов суммы, а также нулевого или единичного кодов на выходе устройства. Накапливающий сумматор содержит коммутатор 1, сумматор 2, дополнительный сумматор 3, регистр 4, группу элементов И 5, первый 6 и второй 7 элементы И, вход 8 операндов сумматоров, выход 9, тактирующий вход 10, вход 11 установки, первый 12 и второй 13 входы управления. 1 ил., 1 табл.

| Устройство для вычитания | 1984 |

|

SU1215109A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Применение интегральных микросхем в электронной вычислительной технике: Справочник/Под ред | |||

| Б.Н.Файзулаева, Б.В.Тарабрина | |||

| М.: Радио-и связь, 1986, с.114, рис.5.59. | |||

Авторы

Даты

1989-01-23—Публикация

1987-01-05—Подача