1

Изобретение относится к медицинской технике, а именно к средствам диагностики и контроля нормальной и патологической физиологии сердечно-сосудистой системы.5

Цель изобретения - повышение достоверности измерения гемодинамических параметров путем уменьшения погрешности измерения, связанной с наличием сердечной аритмии.

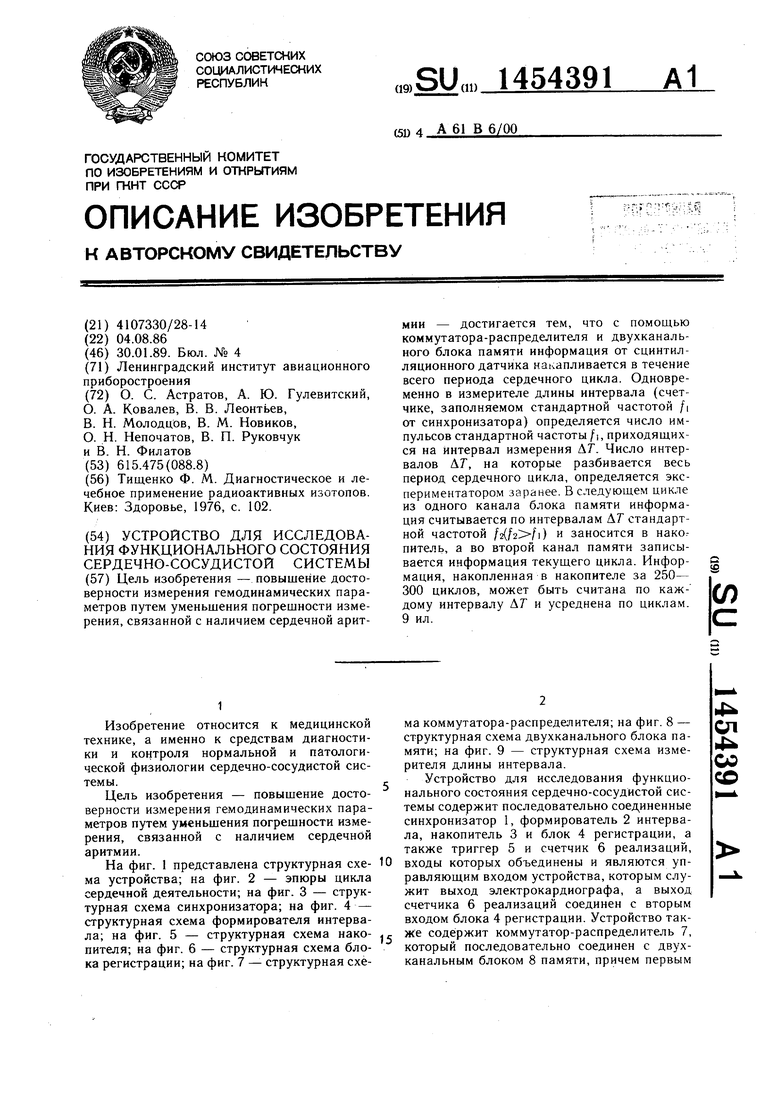

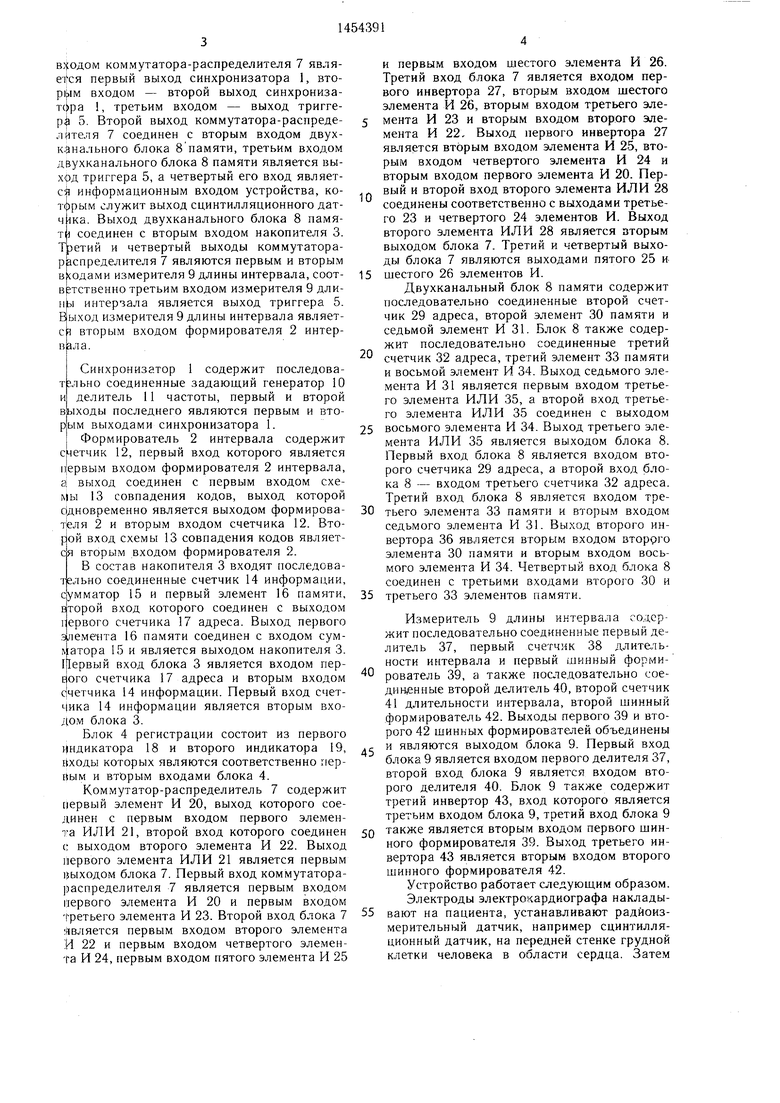

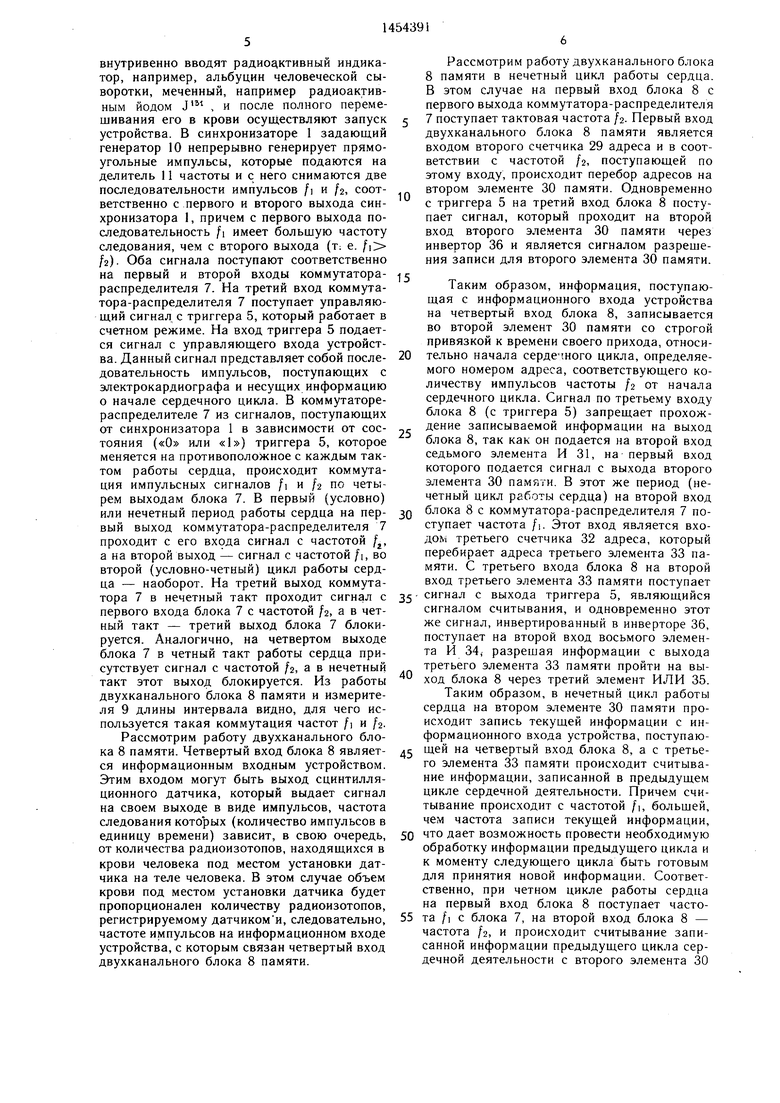

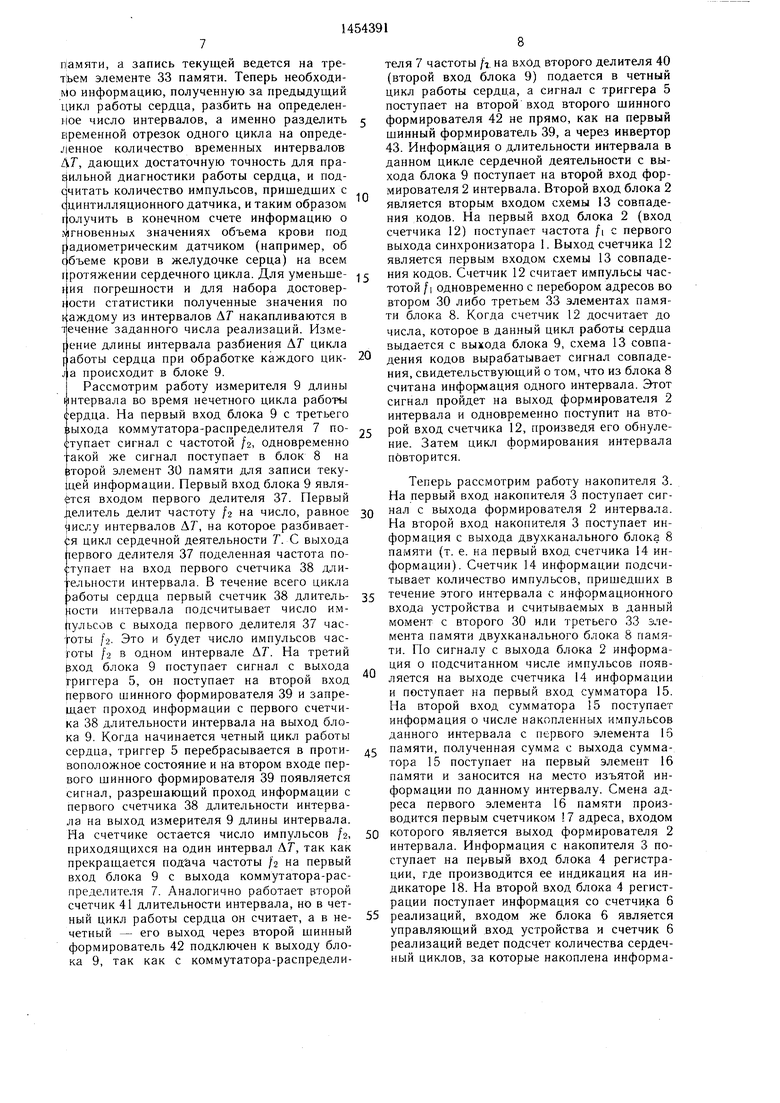

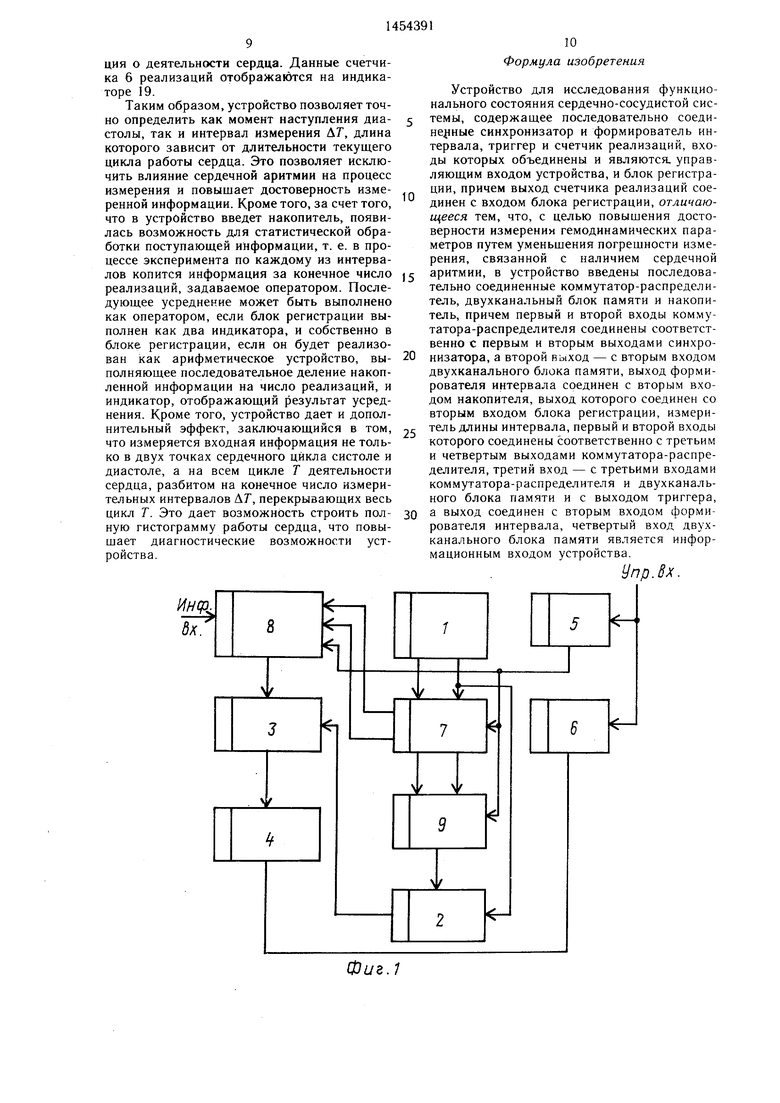

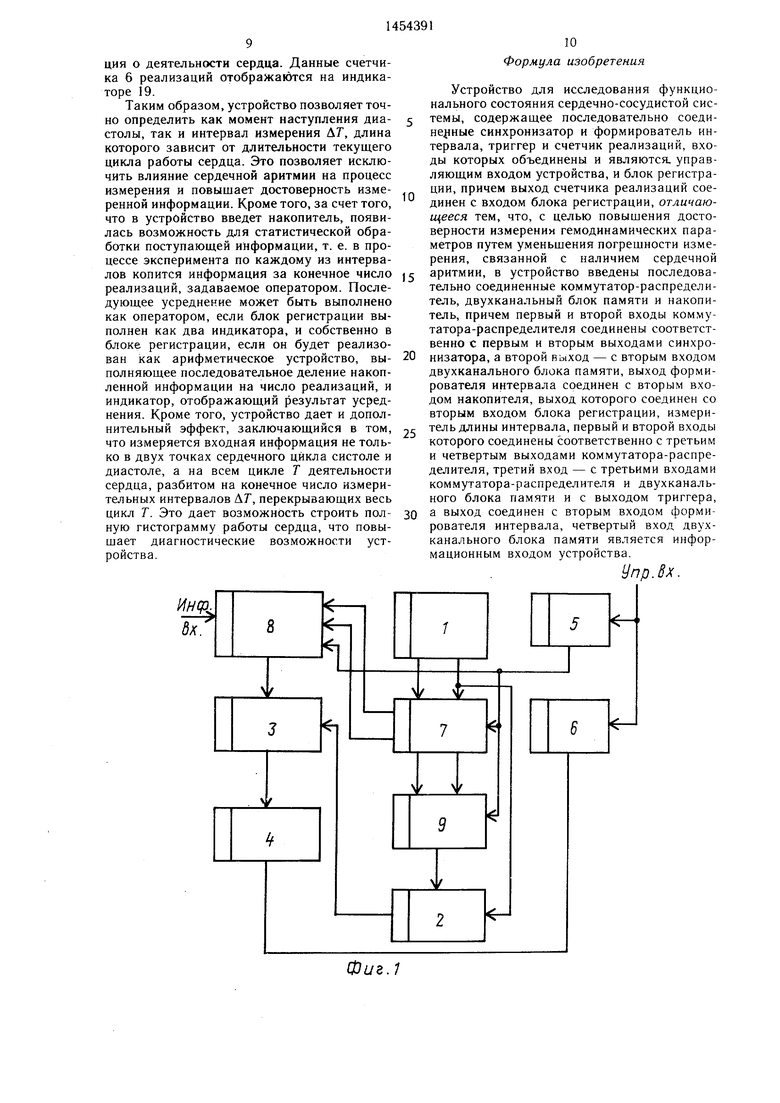

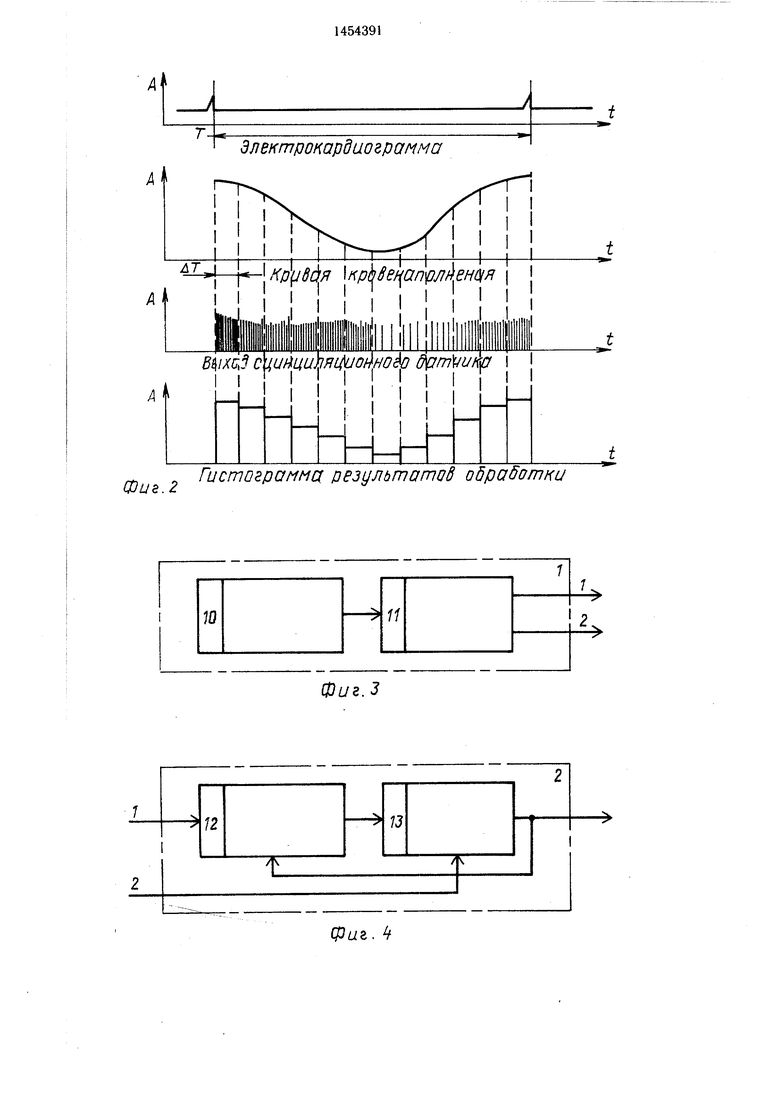

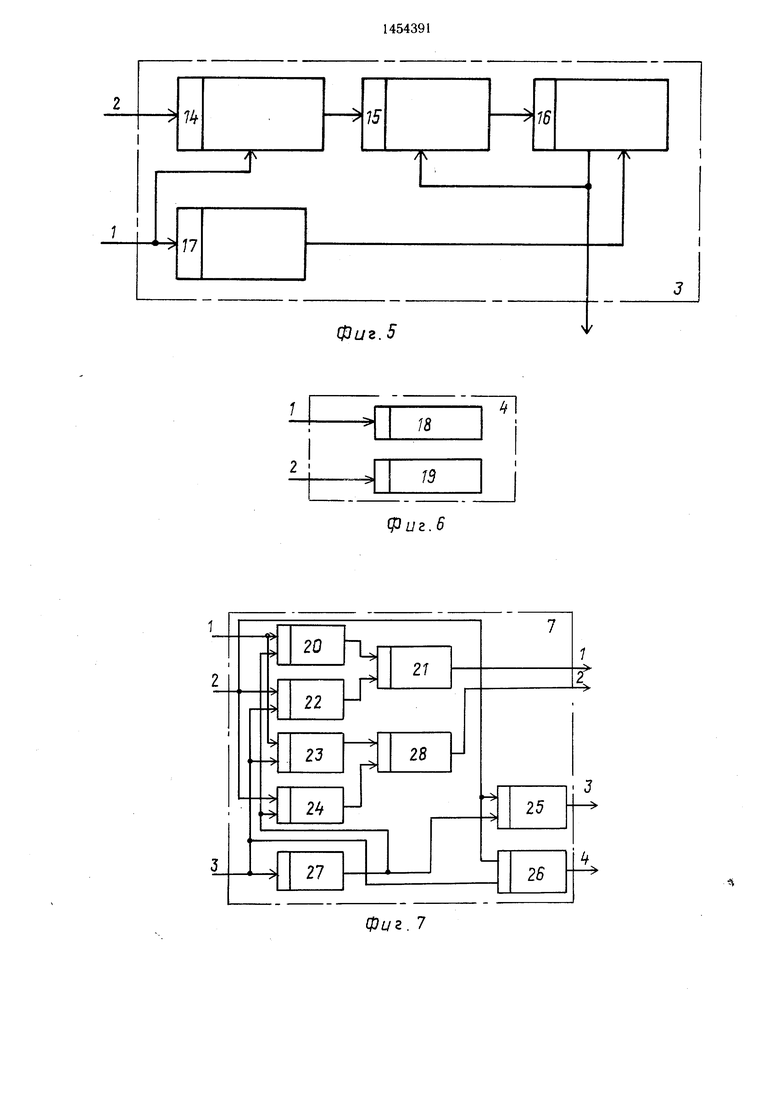

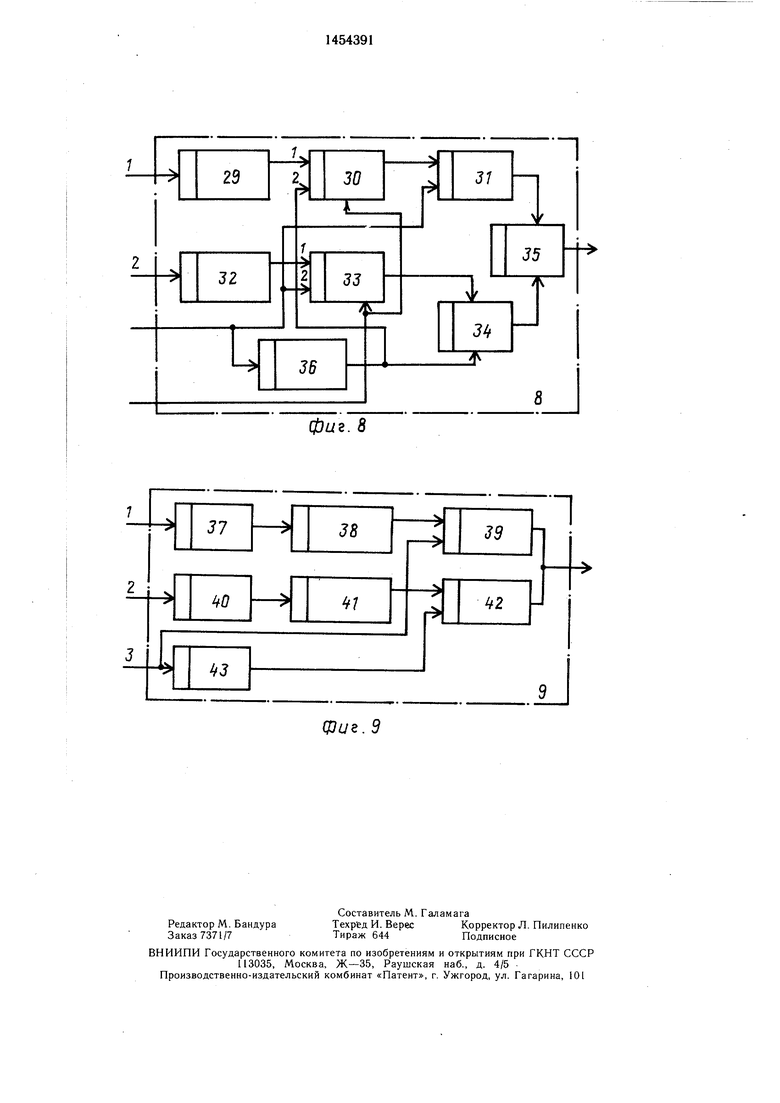

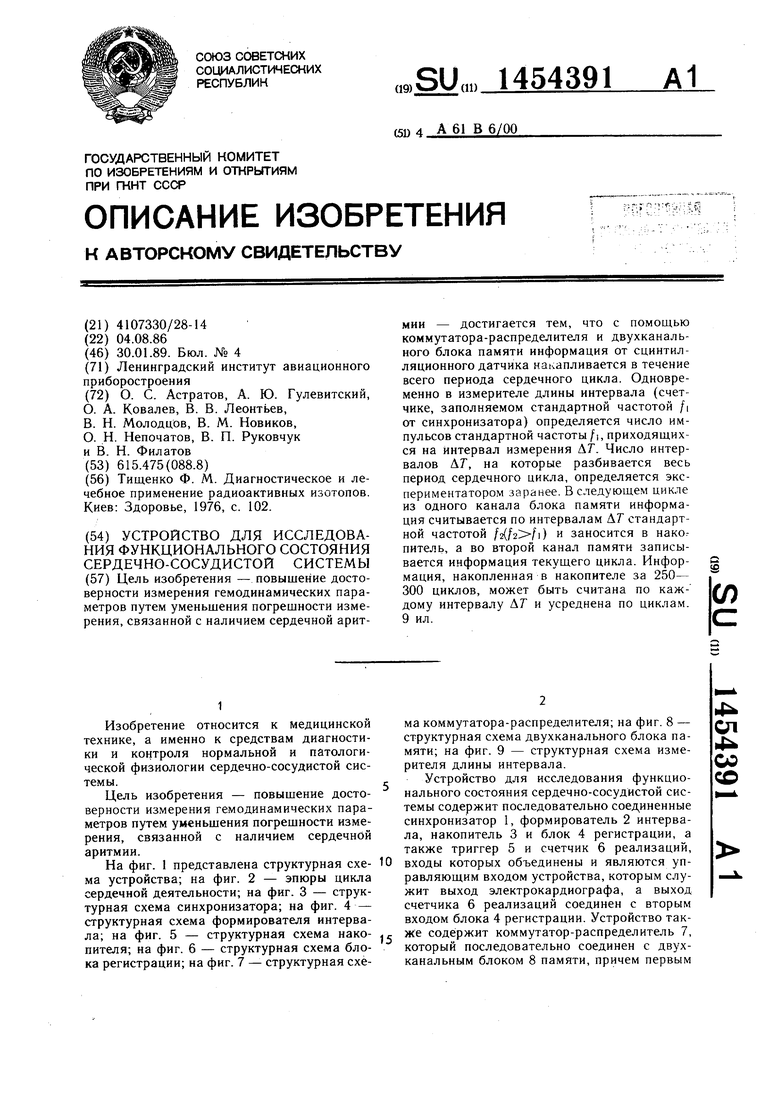

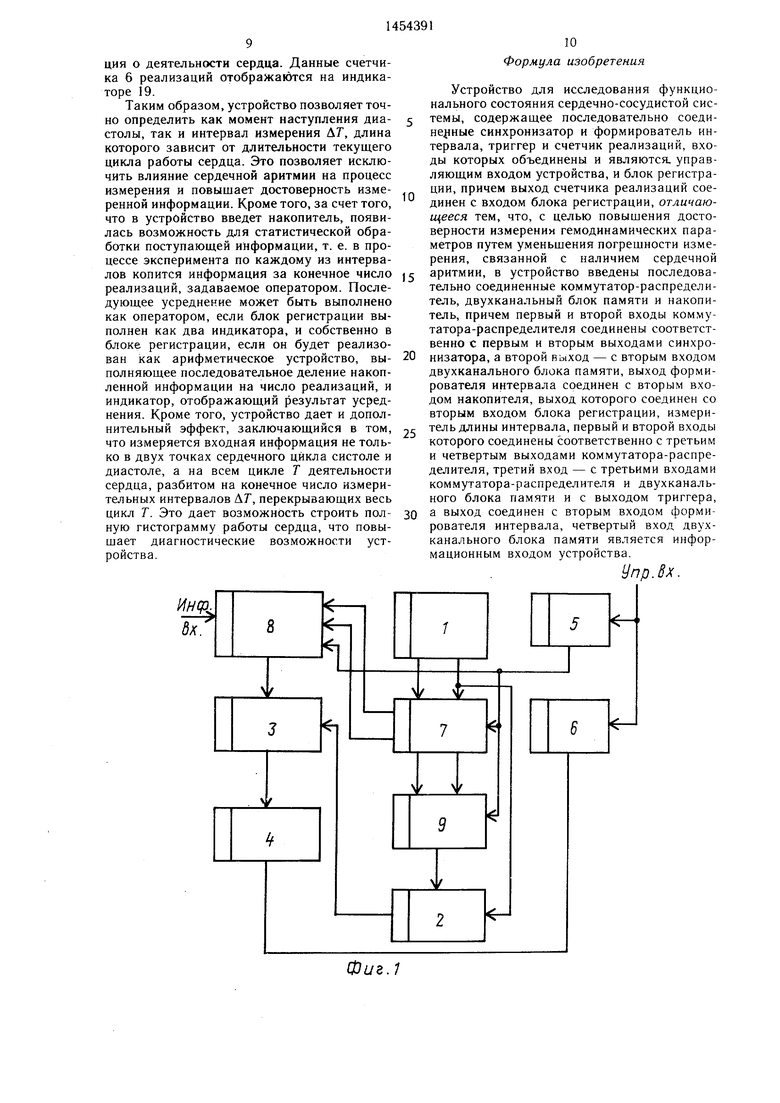

На фиг. 1 представлена структурная схе- Ю ма устройства; на фиг. 2 - эпюры цикла сердечной деятельности; на фиг. 3 - структурная схема синхронизатора; на фиг. 4 - структурная схема формирователя интервала; на фиг. 5 - структурная схема нако- пителя; на фиг. 6 - структурная схема блока регистрации; на фиг. 7 - структурная схема коммутатора-распределителя; на фиг. 8 - структурная схема двухканального блока памяти; на фиг. 9 - структурная схема измерителя длины интервала.

Устройство для исследования функционального состояния сердечно-сосудистой системы содержит последовательно соединенные синхронизатор 1, формирователь 2 интервала, накопитель 3 и блок 4 регистрации, а также триггер 5 и счетчик 6 реализаций, входы которых объединены и являются управляющим входом устройства, которым служит выход электрокардиографа, а выход счетчика 6 реализаций соединен с вторым входом блока 4 регистрации. Устройство также содержит коммутатор-распределитель 7, который последовательно соединен с двух- канальным блоком 8 памяти, причем первым

СП

СО

;о

BjfOAOM коммутатора-распределителя 7 является первый выход синхронизатора 1, вто- pij)iM входом - второй выход синхрониза- т4ра , третьим входом - выход тригге- р 5. Второй выход коммутатора-распределителя 7 соединен с вторым входом двух- к.анального блока 8 памяти, третьим входом двухканального блока 8 памяти является выход триггера 5, а четвертый его вход является информационным входом устройства, ко- т( служит выход сцинтилляционного дат- Ч1ка. Выход двухканального блока 8 памяти соединен с вторым входом накопителя 3. Третий и четвертый выходы коммутатора- распределителя 7 являются первым и вторым входами измерителя 9 длины интервала,соот- вртственно третьим входом измерителя 9 дли- uti интерзала является выход триггера 5. Выход измерителя 9 длины интервала являет- ч вторым входом формирователя 2 интер- врла.

Синхронизатор 1 содержит последова- гльно соединенные задающий генератор 10 делитель 11 частоты, первый и второй

лходы последнего являются первым и втоВЬ

рым выходами синхронизатора 1.

Формирователь 2 интервала содержит счетчик 12, первый вход которого является первым входом формирователя 2 интервала, а выход соединен с первым входом схемы 13 совпадения кодов, выход которой с|дновременно является выходом формирова- 2 и вторым входом счетчика 12. Второй вход схемы 13 совпадения кодов является вторым входом формирователя 2.

В состав накопителя 3 входят последовательно соединенные счетчик 14 информации, сумматор 15 и первый элемент 16 памяти, второй вход которого соединен с выходом первого счетчика 17 адреса. Выход первого элеме нта 16 памяти соединен с входом сумматора 15 и является выходом накопителя 3. Шервый вход блока 3 является входом пер- Ejoro счетчика 17 адреса и вторым входом о четчика 14 информации. Первый вход счетчика 14 информации является вторым входом блока 3.

Блок 4 регистрации состоит из первого |lндикaтopa 18 и второго индикатора 19, которых являются соответственно пер- йым и вторым входами блока 4.

Коммутатор-распределитель 7 содержит первый элемент И 20, выход которого соединен с первым входом первого элемента ИЛИ 21, второй вход которого соединен с выходом второго элемента И 22. Выход первого элемента ИЛИ 21 является первым 15ЫХОДОМ блока 7. Первый вход коммутатора- распределителя 7 является первым входом первого элемента И 20 и первым входом Сретьего элемента И 23. Второй вход блока 7 является первым входом второго элемента И 22 и первым входом четвертого элемента И 24, первым входом пятого элемента И 25

и первым входом шестого элемента И 26. Третий вход блока 7 является входом первого инвертора 27, вторым входом шестого элемента И 26, вторым входом третьего элемента И 23 и вторым входом второго элемента И 22, Выход первого инвертора 27 является вторым входом элемента И 25, вторым входом четвертого элемента И 24 и вторым входом первого элемента И 20. Первый и второй вход второго элемента ИЛИ 28 соединены соответственно с выходами третьего 23 и четвертого 24 элементов И. Выход второго элемента ИЛИ 28 является вторым выходом блока 7. Третий и четвертый выходы блока 7 являются выходами пятого 25 и

шестого 26 элементов И.

Двухканальный блок 8 памяти содержит последовательно соединенные второй счетчик 29 адреса, второй элемент 30 памяти и седьмой элемент И 31. Блок 8 также содержит последовательно соединенные третий

0 счетчик 32 адреса, третий элемент 33 памяти и восьмой элемент И 34. Выход седьмого элемента И 31 является первым входом третьего элемента ИЛИ 35, а второй вход третьего элемента ИЛИ 35 соединен с выходом

5 восьмого элемента И 34. Выход третьего элемента ИЛИ 35 является выходом блока 8. Первый вход блока 8 является входом второго счетчика 29 адреса, а второй вход блока 8 - входом третьего счетчика 32 адреса. Третий вход блока 8 является входом тре0 тьего элемента 33 памяти и вторым входом селчьмого элемента И 31. Выход второго инвертора 36 является вторым входом второго элемента 30 памяти и вторым входом восьмого элемента И 34. Четвертый вход блока 8 соединен с третьими входами второго 30 и

5 третьего 33 элементов памяти.

Измеритель 9 длины интервала содержит последовательно соединенные первый делитель 37, первый счетчик 38 длительности интервала и первый шинный форми- 0 рователь 39, а также последовательно соединенные второй делитель 40, второй счетчик 41 длительности интервала, второй шинный формирователь 42. Выходы первого 39 и второго 42 шинных формирователей объединены и являются выходом блока 9. Первый вход блока 9 является входом первого делителя 37, второй вход блока 9 является входом второго делителя 40. Блок 9 также содержит третий инвертор 43, вход которого является третьим входом блока 9, третий вход блока 9 0 также является вторым входом первого шинного формирователя 39. Выход третьего инвертора 43 является вторым входом второго шинного формирователя 42.

Устройство работает следуюш,им образом.

Электроды электрокардиографа наклады5 вают на пациента, устанавливают радйоизмерительный датчик, например сцинтилляционный датчик, на передней стенке грудной

клетки человека в области сердца. Затем

внутривенно вводят радиоактивный индикатор, например, альбуцин человеческой сыворотки, меченный, например радиоактивным йодом J , и после полного перемешивания его в крови осуществляют запуск устройства. В синхронизаторе 1 задающий генератор 10 непрерывно генерирует прямоугольные импульсы, которые подаются на делитель 11 частоты и с него снимаются две последовательности импульсов /i и /2, соответственно с первого и второго выхода синхронизатора 1, причем с первого выхода последовательность /1 имеет большую частоту следования, чем с второго выхода (т; е. /i /2). Оба сигнала поступают соответственно на первый и второй входы коммутатора- распределителя 7. На третий вход коммутатора-распределителя 7 поступает управляющий сигнал с триггера 5, который работает в счетном режиме. На вход триггера 5 подается сигнал с управляющего входа устройства. Данный сигнал представляет собой последовательность импульсов, поступающих с электрокардиографа и несущих информацию о начале сердечного цикла. В коммутаторе- распределителе 7 из сигналов, поступающих от синхронизатора 1 в зависимости от состояния («О или «1) триггера 5, которое меняется на противоположное с каждым тактом работы сердца, происходит коммутация импульсных сигналов f и /2 по четырем выходам блока 7. В первый (условно) или нечетный период работы сердца на первый выход коммутатора-распределителя 7 проходит с его входа сигнал с частотой /, а на второй выход - сигнал с частотой /i, во второй (условно-четный) цикл работы сердца - наоборот. На третий выход коммутатора 7 в нечетный такт проходит сигнал с первого входа блока 7 с частотой /2, а в четный такт - третий выход блока 7 блокируется. Аналогично, на четвертом выходе блока 7 в четный такт работы сердца присутствует сигнал с частотой /2, а в нечетный такт этот выход блокируется. Из работы двухканального блока 8 памяти и измерителя 9 длины интервала видно, для чего используется такая коммутация частот /i и /2. Рассмотрим работу двухканального блока 8 памяти. Четвертый вход блока 8 является информационным входным устройством. Этим входом могут быть выход сцинтилля- ционного датчика, который выдает сигнал на своем выходе в виде импульсов, частота следования которых (количество импульсов в единицу времени) зависит, в свою очередь, от количества радиоизотопов, находящихся в крови человека под местом установки датчика на теле человека. В этом случае объем крови под местом установки датчика будет пропорционален количеству радиоизотопов, регистрируемому датчиком и, следовательно, частоте импульсов на информационном входе устройства, с которым связан четвертый вход двухканального блока 8 памяти.

5

Рассмотрим работу двухканального блока 8 памяти в нечетный цикл работы сердца. В этом случае на первый вход блока 8 с первого выхода коммутатора-распределителя 7 поступает тактовая частота /2. Первый вход двухканального блока 8 памяти является входом второго счетчика 29 адреса и в соответствии с частотой /2, поступающей по этому входу, происходит перебор адресов на втором элементе 30 памяти. Одновременно с триггера 5 на третий вход блока 8 поступает сигнал, который проходит на второй вход второго элемента 30 памяти через инвертор 36 и является сигналом разрешения записи для второго элемента 30 памяти.

Таким образом, информация, поступающая с информационного входа устройства на четвертый вход блока 8, записывается во второй элемент 30 памяти со строгой привязкой к времени своего прихода, относи0 тельно начала сердечного цикла, определяемого номером адреса, соответствующего количеству импульсов частоты /2 от начала сердечного цикла. Сигнал по третьему входу блока 8 (с триггера 5) запрещает прохождение записываемой информации на выход блока 8, так как он подается на второй вход седьмого элемента И 31, на первый вход которого подается сигнал с выхода второго элемента 30 памяти. В этот же период (нечетный цикл работы сердца) на второй вход

Q блока 8 с коммутатора-распределителя 7 поступает частота f. Этот вход является входом третьего счетчика 32 адреса, который перебирает адреса третьего элемента 33 памяти. С третьего входа блока 8 на второй вход третьего элемента 33 памяти поступает

5-сигнал с выхода триггера 5, являющийся сигналом считывания, и одновременно этот же сигнал, инвертированный в инверторе 36, поступает на второй вход восьмого элемента И 34, разрешая информации с выхода третьего элемента 33 памяти пройти на вы ход блока 8 через третий элемент ИЛИ 35. Таким образом, в нечетный цикл работы сердца на втором элементе 30 памяти происходит запись текущей информации с информационного входа устройства, поступаю5 щей на четвертый вход блока 8, а с третьего элемента 33 памяти происходит считывание информации, записанной в предыдущем цикле сердечной деятельности. Причем считывание происходит с частотой /:, большей, чем частота записи текущей информации,

0 что дает возможность провести необходимую обработку информации предыдущего цикла и к моменту следующего цикла быть готовым для принятия новой информации. Соответственно, при четном цикле работы сердца на первый вход блока 8 поступает часто5 та /1 с блока 7, на второй вход блока 8 - частота /2, и происходит считывание записанной информации предыдущего цикла сердечной деятельности с второго элемента 30

памяти, а запись текущей ведется на третьем элементе 33 памяти. Теперь необходимо информацию, полученную за предыдущий цикл работы сердца, разбить на определенное число интервалов, а именно разделить временной отрезок одного цикла на определенное количество временных интервалов ДГ, дающих достаточную точность для правильной диагностики работы сердца, и подсчитать количество импульсов, прищедших с

сцинтилляционного датчика, и таким образом г:олучить в конечном счете информацию о мгновенных значениях объема крови под радиометрическим датчиком (например, об сбъеме крови в желудочке серца) на всем г ротяжении сердечного цикла. Для уменьше- Р:ИЯ погрешности и для набора достовер- ьюсти статистики полученные значения по ь:аждому из интервалов ДГ накапливаются в течение заданного числа реализаций. Измерение длины интервала разбиения ДГ цикла работы сердца при обработке каждого цик- ла происходит в блоке 9.

Рассмотрим работу измерителя 9 длины интервала во время нечетного цикла работы сердца. На первый вход блока 9 с третьего кыхода коммутатора-распределителя 7 по- ступает сигнал с частотой /г, одновременно акой же сигнал поступает в блок 8 на 5торой элемент 30 памяти для записи теку- 1цей информации. Первый вход блока 9 является входом первого делителя 37. Первый делитель делит частоту /2 на число, равное нсг.у интервалов ДГ, на которое разбивается цикл сердечной деятельности Г. С выхода первого делителя 37 поделенная частота поступает на вход первого счетчика 38 дли- ельности интервала. В течение всего цикла )аботы сердца первый счетчик 38 длитель- 1ости интервала подсчитывает число им- (тульсов с выхода первого делителя 37 частоты /2. Это и будет число импульсов час- готы /2 в одном интервале ДГ. На третий рход блока 9 поступает сигнал с выхода Триггера 5, он поступает на второй вход первого шинного формирователя 39 и запрещает проход информации с первого счетчика 38 длительности интервала на выход блока 9. Когда начинается четный цикл работы сердца, триггер 5 перебрасывается в проти- воположное состояние и на втором входе первого шинного формирователя 39 появляется сигнал, разрешающий проход информации с первого счетчика 38 длительности интервала на выход измерителя 9 длины интервала. На счетчике остается число импульсов /2, приходящихся на один интервал ДГ, так как прекращается под ача частоты fa на первый вход блока 9 с выхода коммутатора-распределителя 7. Аналогично работает второй счетчик 41 длительности интервала, но в четный цикл работы сердца он считает, а в не- четный - его выход через второй шинный формирователь 42 подключен к выходу блока 9, так как с коммутатора-распредели

0

5 О 5 45 50 55

теля 7 частоты /7. на вход второго делителя 40 (второй вход блока 9) подается в четный цикл работы сердца, а сигнал с триггера 5 поступает на второй вход второго шинного формирователя 42 не прямо, как на первый шинный формирователь 39, а через инвертор 43. Информация о длительности интервала в данном цикле сердечной деятельности с выхода блока 9 поступает на второй вход формирователя 2 интервала. Второй вход блока 2 является вторым входом схемы 13 совпадения кодов. На первый вход блока 2 (вход счетчика 12) поступает частота / с первого выхода синхронизатора 1. Выход счетчика 12 является первым входом схемы 13 совпадения кодов. Счетчик 12 считает импульсы частотой /I одновременно с перебором адресов во втором 30 либо третьем 33 элементах памяти блока 8. Когда счетчик 12 досчитает до числа, которое в данный цикл работы сердца выдается с выхода блока 9, схема 13 совпадения кодов вырабатывает сигнал совпадения, свидетельствующий о том, что из блока 8 считана информация одного интервала. Этот сигнал пройдет на выход формирователя 2 интервала и одновременно поступит на второй вход счетчика 12, произведя его обнуление. Затем цикл формирования интервала повторится.

Теперь рассмотрим работу накопителя 3. На первый вход накопителя 3 поступает сигнал с выхода формирователя 2 интервала. На второй вход накопителя 3 поступает информация с выхода двухканального блока 8 памяти (т. е. на первый вход счетчика 14 информации). Счетчик 14 информации подсчитывает количество импульсов, пришедших в течение этого интервала с информационного входа устройства и считываемых в данный момент с второго 30 или третьего 33 элемента памяти двухканального блока В памяти. По сигналу с выхода блока 2 информация о подсчитанном числе импульсов появляется на выходе счетчика 14 информации и поступает на первый вход сумматора 15. На второй вход сумматора 15 поступает информация о числе накопленных импульсов данного интервала с первого элемента 16 памяти, полученная сумма с выхода сумматора 15 поступает на первый элемент 16 памяти и заносится на место изъятой информации по данному интервалу. Смена адреса первого элемента 16 памяти производится первым счетчиком 7 адреса, входом которого является выход формирователя 2 интервала. Информация с накопителя 3 поступает на первый вход блока 4 регистрации, где производится ее индикация на индикаторе 18. На второй вход блока 4 регистрации поступает информация со счетчика 6 реализаций, входом же блока 6 является управляющий вход устройства и счетчик 6 реализаций ведет подсчет количества сердечный циклов, за которые накоплена информация о деятельности сердца. Данные счетчика 6 реализаций отображаются на индикаторе 19.

Таким образом, устройство позволяет точно определить как момент наступления диастолы, так и интервал измерения АГ, длина которого зависит от длительности текущего цикла работы сердца. Это позволяет исключить влияние сердечной аритмии на процесс измерения и повышает достоверность измеренной информации. Кроме того, за счет того, что в устройство введет накопитель, появилась возможность для статистической обработки поступающей информации, т. е. в процессе эксперимента по каждому из интервалов копится информация за конечное число реализаций, задаваемое оператором. Последующее усреднение может быть выполнено как оператором, если блок регистрации выполнен как два индикатора, и собственно в блоке регистрации, если он будет реализован как арифметическое устройство, выполняющее последовательное деление накопленной информации на число реализаций, и индикатор, отображающий результат усреднения. Кроме того, устройство дает и дополнительный эффект, заключающийся в том, что измеряется входная информация не только в двух точках сердечного цикла систоле и диастоле, а на всем цикле Т деятельности сердца, разбитом на конечное число измерительных интервалов АГ, перекрывающих весь цикл Т. Это дает возможность строить полную гистограмму работы сердца, что повышает диагностические возможности устройства.

10 Формула изобретения

Устройство для исследования функционального состояния сердечно-сосудистой системы, содержащее последовательно соеди- синхронизатор и формирователь интервала, триггер и счетчик реализаций, входы которых объединены и являются, управляющим входом устройства, и блок регистрации, причем выход счетчика реализаций соединен с входом блока регистрации, отличаю- ш,ееся тем, что, с целью повышения достоверности измерении гемодинамических параметров путем уменьшения погрешности измерения, связанной с наличием сердечной аритмии, в устройство введены последовательно соединенные коммутатор-распределитель, двухканальный блок памяти и накопитель, причем первый и второй входы коммутатора-распределителя соединены соответственно с первым и вторым выходами синхронизатора, а второй выход - с вторым входом двухканального блока памяти, выход формирователя интервала соединен с вторым входом накопителя, выход которого соединен со вторым входом блока регистрации, измеритель длины интервала, первый и второй входы которого соединены соответственно с третьим и четвертым выходами коммутатора-распределителя, третий вход - с третьими входами коммутатора-распределителя и двухканального блока памяти и с выходом триггера, а выход соединен с вторым входом формирователя интервала, четвертый вход двухканального блока памяти яв.:1яется информационным входом устройства.

Упр.Вх.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Устройство для сжатия информации | 1987 |

|

SU1529043A1 |

| Устройство для контроля видеосигнала | 1982 |

|

SU1069190A1 |

| Регистрирующее устройство | 1988 |

|

SU1509595A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| ДОПЛЕРОВСКИЙ ИЗМЕРИТЕЛЬ СОСТАВЛЯЮЩИХ ВЕКТОРА СКОРОСТИ, ВЫСОТЫ И МЕСТНОЙ ВЕРТИКАЛИ ДЛЯ ВЕРТОЛЕТОВ И КОСМИЧЕСКИХ АППАРАТОВ ВЕРТИКАЛЬНОЙ ПОСАДКИ | 1995 |

|

RU2083998C1 |

| Устройство для сопряжения с датчиками | 1989 |

|

SU1695286A1 |

| Многоканальное устройство для форми-РОВАНия ВРЕМЕННыХ иНТЕРВАлОВ | 1979 |

|

SU815875A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

Цель изобретения - повышение достоверности измерения гемодинамических параметров путем уменьшения погрешности измерения, связанной с наличием сердечной аритмии - достигается тем, что с помош,ью коммутатора-распределителя и двухканаль- ного блока памяти информация от сцинтил- ляционного датчика накапливается в течение всего периода сердечного цикла. Одновременно в измерителе длины интервала (счетчике, заполняемом стандартной частотой /i от синхронизатора) определяется число импульсов стандартной частоты f, приходящихся на интервал измерения ДГ. Число интервалов ДГ, на которые разбивается весь период сердечного цикла, определяется экспериментатором заранее. В следующем цикле из ОДНОГО канала блока памяти информация считывается по интервалам ДТ стандартной частотой /2{/2 fi) и заносится в наког питель, а во второй канал памяти записывается информация текущего цикла. Информация, накопленная в накопителе за 250- 300 циклов, может быть считана по каждому интервалу ДГ и усреднена по циклам. 9 ил. S (Л

Фиг.1

T.

длектрокардиогра/ ма

т I

-j ру8дя кр е/ ап лЛенО(я

II I ....I

B C CUUfiUUML Of HO /77(Уг/ЛК7

I I г I I I I I 1 I г

I

I

Фие.2

Гистограмма, результатов обработки

Фиг.З

фиг.

лЛенО(я

III I ....I

1 I г

I

фиг.6

Фиг. 7

фиг. 8

Фи.9

| Тищенко Ф | |||

| М | |||

| Диагностическое и лечебное применение радиоактивных изотопов | |||

| Киев: Здоровье, 1976, с | |||

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU102A1 |

Авторы

Даты

1989-01-30—Публикация

1986-08-04—Подача