hd

315

Изобретение относится к вычислительной технике, в частности к адаптивным мультипроцессорным системам, перестраивающим свою структуру в. зависимости как от заданньи способов обработки данных, так и от отказов отдельных процессоров, и может быть применено в измерительно-вычислительных комплексах и в автоматизиро- ванных системах управления технологическими процессами, в системах автоматизации испытаний и контроля сложных объектов и в других подобных системах, имеющих высокую живучесть.

Цель изобретения - повышение надежности системы при работе в реаль- ном времени за счет автоматического восстановления ее функции при отказах отдельных процессоров

Указанная цель обеспечивается тем что восстановление функционирования системы при отказе одного или нескольких процессоров осуществляется путем упорядоченного з еньшения пото ка заявок, поступающего в блок памяти, и исключения возможности переполнения блока памятио Для этого все заявки условно разбиваются по степени значимости на несколько независимых приоритетных групп. В грзшпу с высшим приоритетом назначаются заявки, несущие особо важную информацию, в группу с низшим приоритетом - заявки несущие вспомогательнзпо информацию.

Для случая информационно-измери- тельньпс систем с многоканальной структурой сбора данных разбивку на такие группы целесообразно осуществлять поканально, Тое все выборки от нескольких вспомогательных каналов следует отнести к одной, например, низшей приоритетной группе,все выборки более важных каналов следует отнести по некоторому числу ка- налов в следующие приоритетные группы

Число приоритетных групп целесообразно выбрать равным числу процессоров в системе При зтом число каналов в группах всегда можно установить так, чтобы среднее время обработки выборок в группах было практически одинаковым Тогда при отказе одного процессора можно будет отключать одну группу каналов, двух процессоров - две группы и так далее по увеличению приоритета.

5 0 5

0 5

0

5

14

Тем самым обеспечивается упорядоченное, адекватное снижение пропускной способности системы,уменьшение входного потока заявок и исключается переполнение блока памяти. Система остается работоспособной,вьшол- няет функции обработки оставшихся наиболее важных групп каналов и таким образом переходит в разряд систем с постепенным отказом. Так как в системе отсутствуют внешние признаки отказов отдельных процессоров,в качестве критерия для упорядоченного уменьшения входного потока используется уровень заполнения блока памяти

В согласованной по потокам системе, реального времени уровень заполнения из-за неравномерности записываемого и считываемого из блока памяти потоков является переменным с определенным для данного режима работы максимумом Переход через этот максимум во время работы однозначно свидетельствует об отказе какого-либо процессора

По признаку перехода первого максимума может отключаться первая группа каналов с низшим приоритетом ; При этом в системе вновь устанавли-- вается согласованный режим обработки с другим максимумом Отказ следующе- го процессора приводит к переходу уровня заполнения блока памяти через этот другой максимум Признак перехода отключает следующую группу каналов и . Так как максимумы являются величинами переменными,удобнее установить для заданных режимов работы системы определенные граничные величины уровня заполнения блока памяти и переход через них использовать для переключения потока входной информации

Переход через последнюю граничную величину (равную полному заполнению . блока памяти) наступает в этом случае только при отказе всех процессоров.

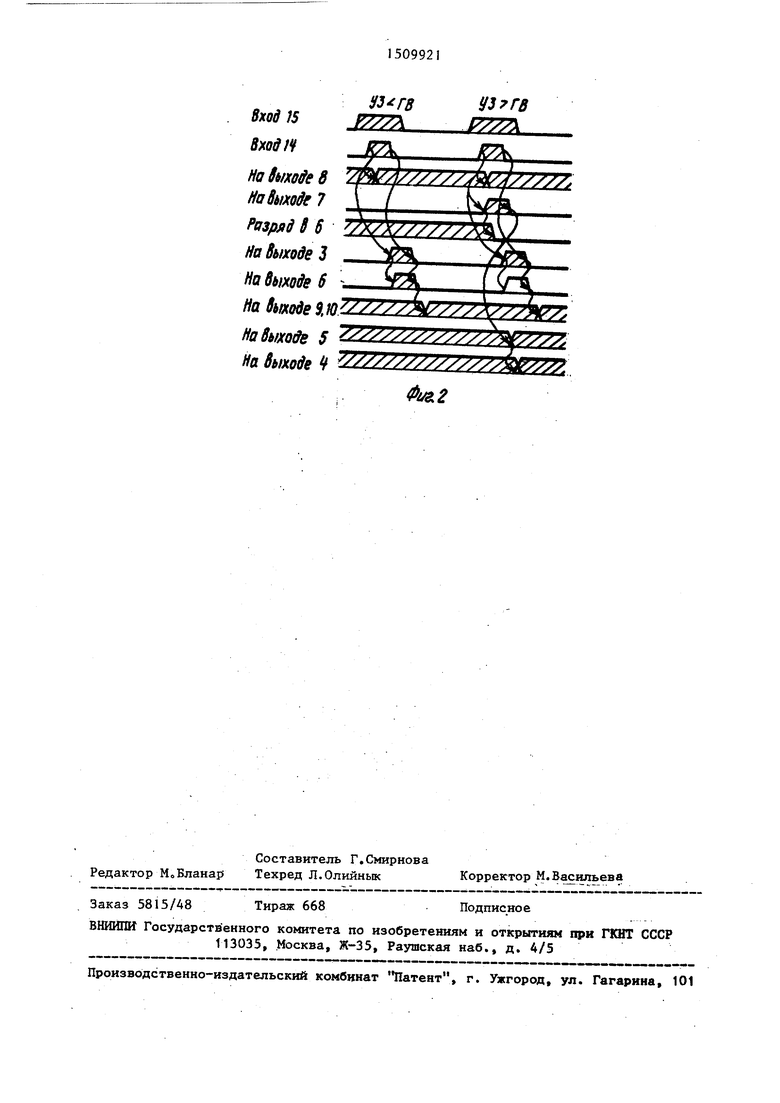

На представлена функциональная схема предлагаемой системы; на фиг. 2 - временная диаграмма работы спстемь1,

Адаптивная система обработки данных содержит блок 1 памяти, процессоры 2, регистровую память номеров приоритетных групп 3, регистровую память граничных величин 4, счетчик 5 адреса граничных величин, регистр

6 признаков приоритетных групп 6, схему 7 сравнения, входной регистр 8, счетчик 9 адреса записи, счетчик 10 заполнения, счетчик 11 адреса считьшания, вход 12 задания режима,магистраль 13 передачи данных, синхро- вход 14, информационный вход 15., выход 16 неисправности системы.

Система работает следующим обра-

ЗОМо

Е исходном состоянии в регистровую память номеров приоритетных групп 3 записаны коды номеров приоритетных групп, в разряды регистра 6 призна- ков приоритетных групп записаны признаки приоритетных групп, в регистровую память граничных величин 4 записаны коды граничных величин,счетчики 5,6,9, 10 и П и блок 1 памяти обнулены, процессоры 2 в рабочем состоянии

На информационный вход 15 системы последовательно поступают параллельным двоичным кодом заявки (выборки и соответствующие им номера измерительных каналов). Синхронизация поступления заявок осуществляется сигн.алом на синхровходе 14 системы. По переднему фронту этого сигнала производятся запись заявки во входной регистр 8, включение схемы 7 сравнения и сравнение величины уровня заполнения блока 1 памяти, поступающей с выхода счетчика 10 заполнения, с .текущей граничной величиной, поступающей с выхода регистровой памяти граничных величин 4, считьгаание из регистровой памяти номеров приоритетных групп 3 кода номера приоритетной группы.

Код номера приоритетной группы считывается из того регистра,адресом которого является код номера канала, поступающий с информационного. входа 15о Каждому каналу в зависимости от его приоритетности соответствует определенный номер приоритетной группы. Считанный код поступает в регистр 6 признаков приоритетных групп в качестве адреса соответствующего разряда В разрядах регистра 6 хранятся признаки приоритетных групп (1 НИИ О).

Если в разряде регистра 6 признак равен , то сигналом с выхода регистра 6 производится запись заявки в ячейку блока 1 памяти и входного регистра 8 Адрес ячейки в блоке . 1 па

д

0

5 0 Q

Q

5

мяти определяет код с выхода счетчика 9 адреса записи, работающего .по кольцевому принципу. По окончании записи содержимое счетчика 9 адреса записи увеличивается на I (по заднему фронту сигнала записи). Одновременно увеличивается на 1 содержимое счетчика 10 заполнения, подсчитывающего количество хранящихся в блоке 1 памяти заявок.

Ксли в разряде регистра 6 признак равен О, то сигнал на выходе стра 6 отсуствует, . запись заявок соответствующей приоритетной группы из входного регистра 8 в блок 1 памяти не происходит

Блок 1 памяти работает как кольцевой буфер о Считывание из него очередной заявки осуществляется по сигналу с выхода запроса первого процессора 2о Адрес считываемой ячейки определяет кольцевой счетчик 11 адреса считывания, содержимое которого увеличивается на 1 после каждого считьгоа- ния, одновременно уменьщается на 1 содержимое счетчика 10 заполнения.

Таким образом, в блок 1 памяти записьюаютсн заявки всех тех групп каналов, которые имеют в регистре 6 признак, равный 1. В том случае, если в момент сравнения в схеме 7 сравнения уровень заполнения блока 1 памяти превьшает значение граничной величины (вследствие отказа одного или нескольких процессоров 2), сигнал с выхода схемы 7 сравнения еще до прихода очередного номера приоритетной группы стирает в регистре 6 (т.е. записывает О в соответствующий разряд регистра).признак наименьшей по приоритету группы и тем самым запрещает последующую запись в блок 1 памяти, заявок по всем каналам этой группы Адресом обиуляе- мого в регистре 6 разряда служит код, поступающий с выхода счетчика 5 адреса граничных величин Этот код является также адресом регистра соответствующей граничной в регистровой памяти граничных величин АО Изменение значения кода в счетчике 5 адреса граничных величин (увеличение на I) производится по заднему фронту сигнала с выхода схемы 7 сравнения, после этого на первый вход схемы 7 сравнения подается значение следующей по приоритету граничной величины и т«До

Таким образом, при превышении текущей граничной величины производится стирание признаков в регистре 6 признаков приоритетных групп и уста- новка на первом входе схемы 7 сравнения следующей граничной величины Тем самым обеспечивается упорядоченное уменьшение входного потока заявок при отказах процессоров 2 о

Формула изобретения

Адаптивная система обработки данных, содержащая блок памяти и N про- цессоров, причем информационные входы-выходы всех процессоров и информационный вход-выход блока памяти соединены через магистраль передачи данных, вход задания режима каждого про- цессора подключен к входу задания режима системы, вход запроса блока памяти подключен к выходу запроса первого процессора, выход разрешения блока памяти подключен к входу раз- решения первого процессора, выход разрешения 1-го (, N-1) процессора подключен к входу разрешения (i+l)-ro процессора, выход запроса и выход неисправности 1-го (,N) процессора подключены соответственно к входу запроса и к входу опроса исправности (i-l)-ro процессора,выход неисправности первого процессора является выходом неисправности системы отличающаяся тем, что, с целью повьппения надежности системы при работе в реальном времени за сче автоматического восстановления ее функции при отказа;х отдельных процес соров, в нее введены регистровая память номеров приоритетных групп,регистровая память граничных величин.

счетчик адреса граничных величин,регистр признаков приоритетных групп, схема сравнения, входной регистр, счетчик адреса записи, счетчик заполнения, счетчик адреса считывания,причем информационный вход входного регистра и адресный вход регистровой памяти номеров приоритетных групп подключены к информационному входу системы, вход записи входного регистра, вход считывания регистровой памяти номеров приоритетных групп и вход разрешения схемь сравнения подключены к синхровходу системы, выход входного регистра подключен к информационному входу блока памяти, выход регистровой памяти номеров приоритетных групп подключен к первому адресному входу регистра признаков приоритетных групп, второй адресный вход которого подключен к адресному входу регистровой памяти граничных величин и к выходу счетчика адреса, граничных величин, счетный вход которого подключен к выходу схемы сравнения и к входу записи нуля регистра признаков приоритетных групп, вьтход которого подключен к входу записи блока памяти, входу прямого счета счетчика заполнения и счетному входу счетчика адреса записи, выход которого подключен к входу адреса записи блока памяти, вход адреса считывания которого подключен к выходу счетчика адреса считывания, счетный вход которого подключен к входу обратного счета счетчика заполнения и к входу зап- роса блока памяти, первьш вход схемь сравнения подключен к выходу регистровой памяти граничных величин,второй вход схемы сравнения подключен к выходу счетчика заполнения.

Вход 15 tfxff(f/y

HaSuxofeS Щ

НаВыхо 7 i /

PtfSftjid 8 6 wi Ha быходе 3 Ha дыходе S Hп8ы} oдe9.Ю ZZZZZ

Ha Выходе 5

РУ/А.

2:аК

2Хх

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная вычислительная система | 1990 |

|

SU1798799A1 |

| Адаптивная система обработки данных | 1985 |

|

SU1312596A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1455342A1 |

| Устройство сопряжения процессоров в многопроцессорной вычислительной системе с изменяемой конфигурацией | 1984 |

|

SU1259278A1 |

| Устройство управления обменом | 1977 |

|

SU771655A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1451713A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

| Устройство управления памятью | 1987 |

|

SU1411761A1 |

| Коммутационное устройство для мультипроцессорной системы | 1976 |

|

SU734697A1 |

Изобретение относится к вычислительной технике , в частности, к адаптивным мультипроцессорным системам, перестраивающим свою структуру в зависимости как от заданных способ обработки данных, так и от отказов отдельных процессоров, и может быть применено в измерительно-вычислительных комплексах, в автоматизированных системах управления технологическими процессами и в системах автоматизации испытаний и контроля сложных объектов. Цель изобретения - повышение надежности системы при работе в реальном времени за счет автоматического восстановления ее функционирования при отказах процессоров. Указанная цель достигается тем, что система содержит блок памяти 1, процессоры 2, регистровую память 3 номеров приоритетных групп, регистровую память 4 граничных величин, счетчик 5 адреса граничных величин, регистр 6 признаков приоритетных групп, схему 7 сравнения, входной регистр 8, счетчик 9 адреса записи, счетчик 10 заполнения и счетчик 11 адреса считывания. 2 ил.

й 8шо6е / //////// / / к УТ.

| Адаптивная система обработки данных | 1980 |

|

SU926662A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-23—Публикация

1988-01-04—Подача