(Л С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Внутрисхемный эмулятор | 1988 |

|

SU1615715A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для сопряжения ведущей и N ведомых цифровых вычислительных машин | 1988 |

|

SU1531104A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1282139A1 |

| УСТРОЙСТВО ДЛЯ ОТЛАДКИ МИКРОЭВМ | 1990 |

|

RU2015540C1 |

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1996 |

|

RU2110833C1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

Изобретение относится к вычислительной технике и предназначено для ввода и отладки программ в цифровой вычислительной системе. Цель изобретения - расширение области применения устройства. Устройство содержит дешифратор 1 адреса, узел 2 ввода-вывода, узел 3 захвата, узел 4 согласования шин, узел 5 останова. Использование управляющей микроЭВМ позволяет пользователю расширять набор отладочнЬ1Х функций, задавая в формате одного командного слова несколько отладочных режимов. 8 ил. (С

}9 21

20

Изобретение относится к вычислительной технике и предназначено для ввода и отладки программ в цифровой вычислительной системе, реализованной на базе микропроцессоров (МП) и имеющей магистральную структуру.

Цель изобретения - расширение области применения устройства.

Запуск отлаживаемой программы с определенного адреса, а также чтени и модификация содержимого внутренних регистров МП-процессора отлаживаемой вычислительной системы (ОВС) осуществляются в предлагаемом устройстве методом имитации памяти, пр этом в шину управления интерфейса процессора ОВС из узла программируемого ввода-вывода (ПВВ) формируются управляющие сигналы, осуществляющие логическое отклЕОчение Памяти и портов ввода-вывода процессора ОВС от внутреннего интерфейса, кроме того, осуществляется подмена их портом ввода-вывода данных узла ПВБ, Управ ляющая микроэвм вводит в порт ввода вывода данных узла ПВВ коды команд и операндов и, формируя из узла сог ласования шин сигнал приемопередачи (ППД), имитирует работу памяти и портов ввода-вывода процессора ОВС, при этом МП-процессора ОВС, выполня эти команды, осуществляет различные отладочные процедуры: переход к от- лаживйемой программе по определенному адресу, ввод или вывод содержиг- мого своих внутренних регистров и т.п. Трансляция данных между портом ввода-вывода данных узла ПВВ и шиной данных интерфейса процессора ОВС в данном режиме осуществляется через узел согласования шин при наличии сигналов ВВ, ВЫВ, СЧТ, ЗПС шины управления интерфейса процессора ОВС. Окончание трансляции данных через узел согласования шин определяется моментом.окончания сигналов ВВ, ВЫВ, СЧТ, ЗПС шины управления процессора ОВС, а не моментом окончания определенного временного интевала от начала трансляции данных,чт обеспечивает более надёжную работу МП-процессора ОВС. Таким образом, введение дополнительных признаков позволяет Получить положительный эффект и удовлетворяет критерию существенных отличий.

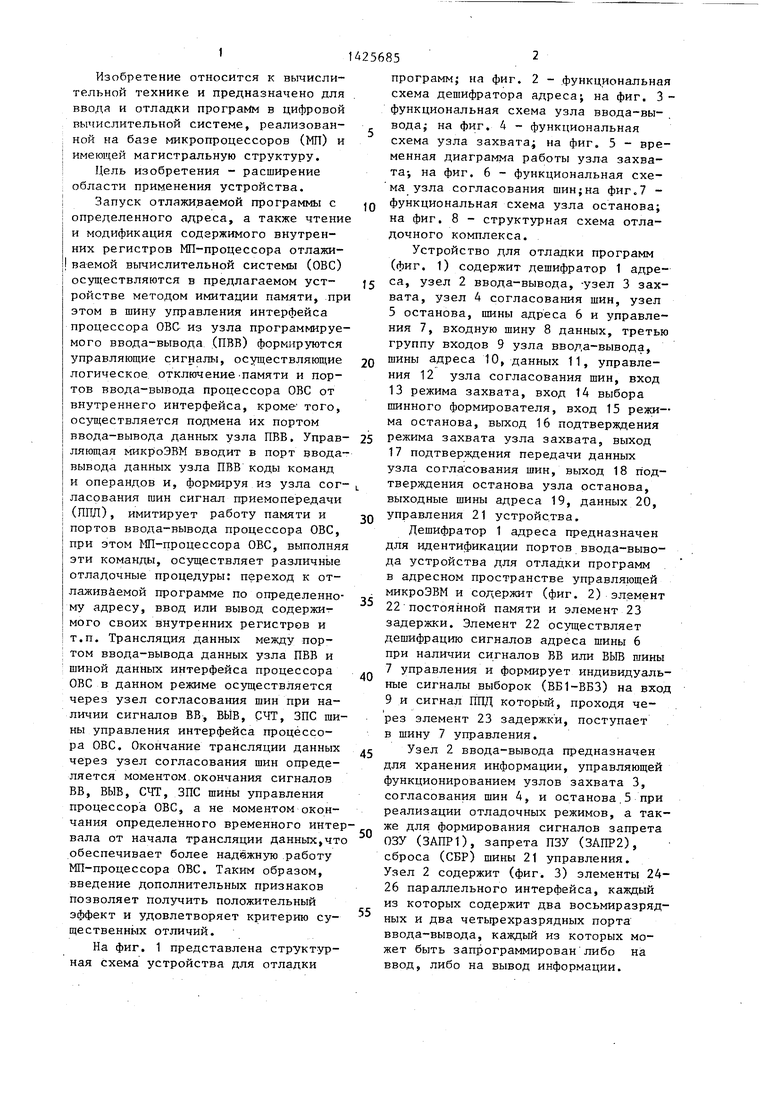

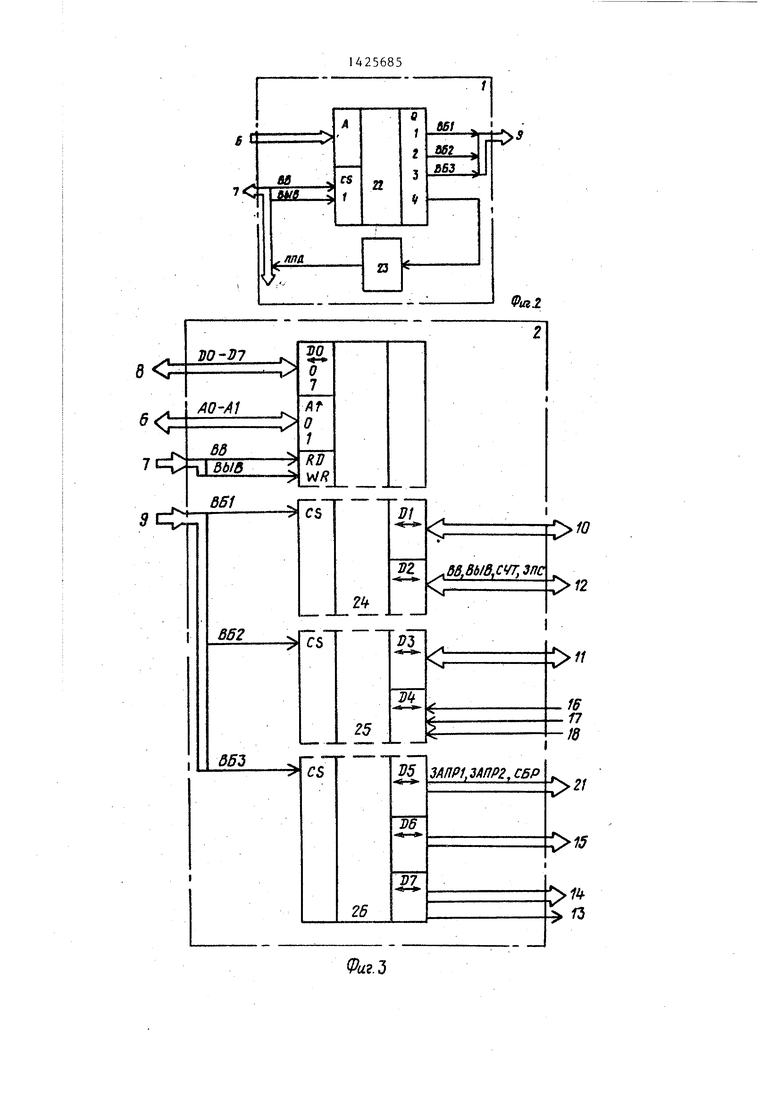

На фиг. 1 представлена структурная схема устройства для отладки

5

0

5

0

5

0

5

0

5

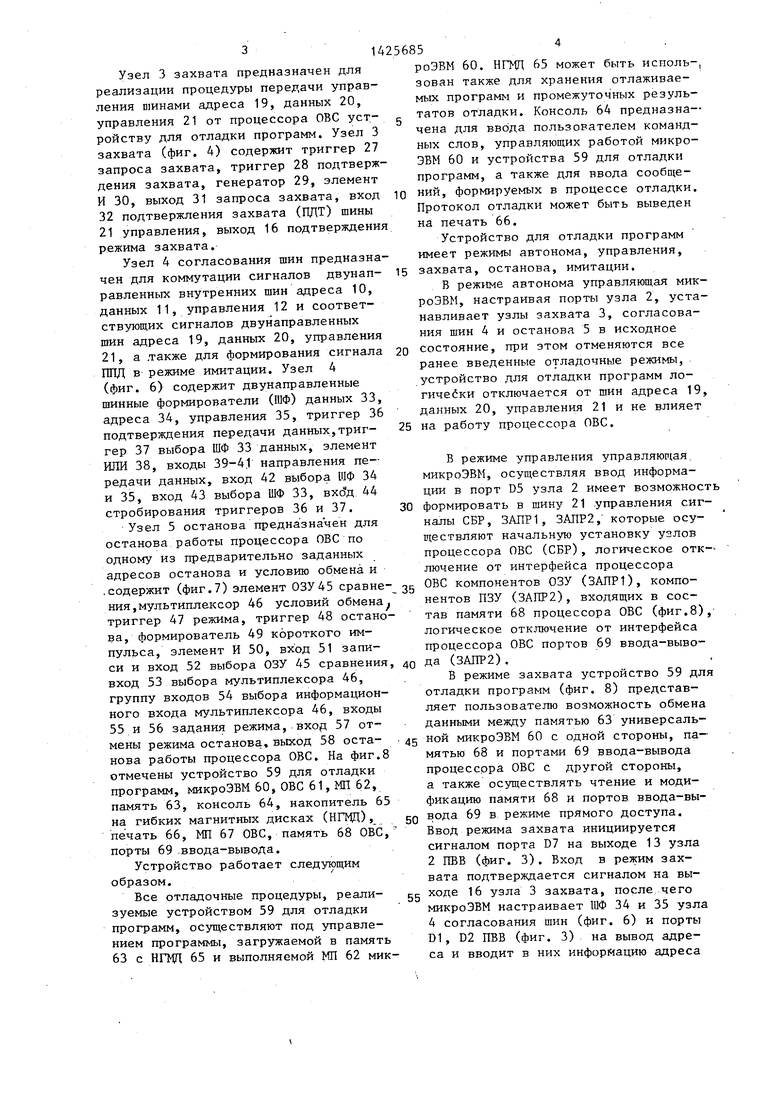

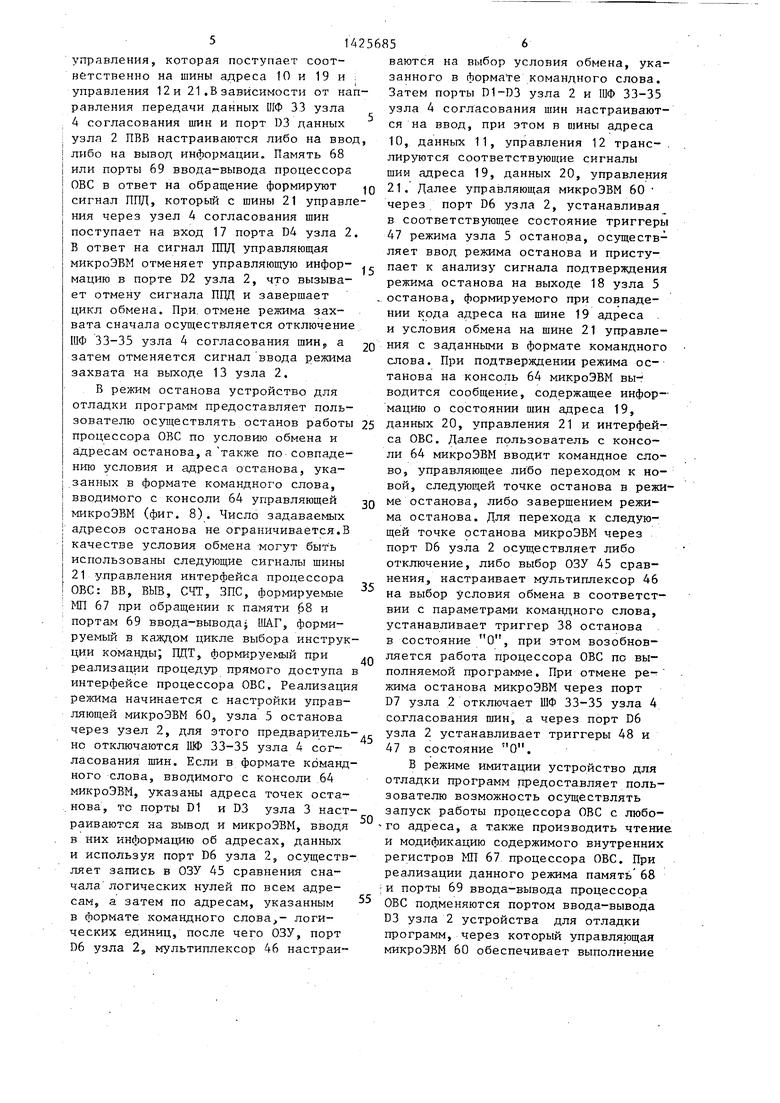

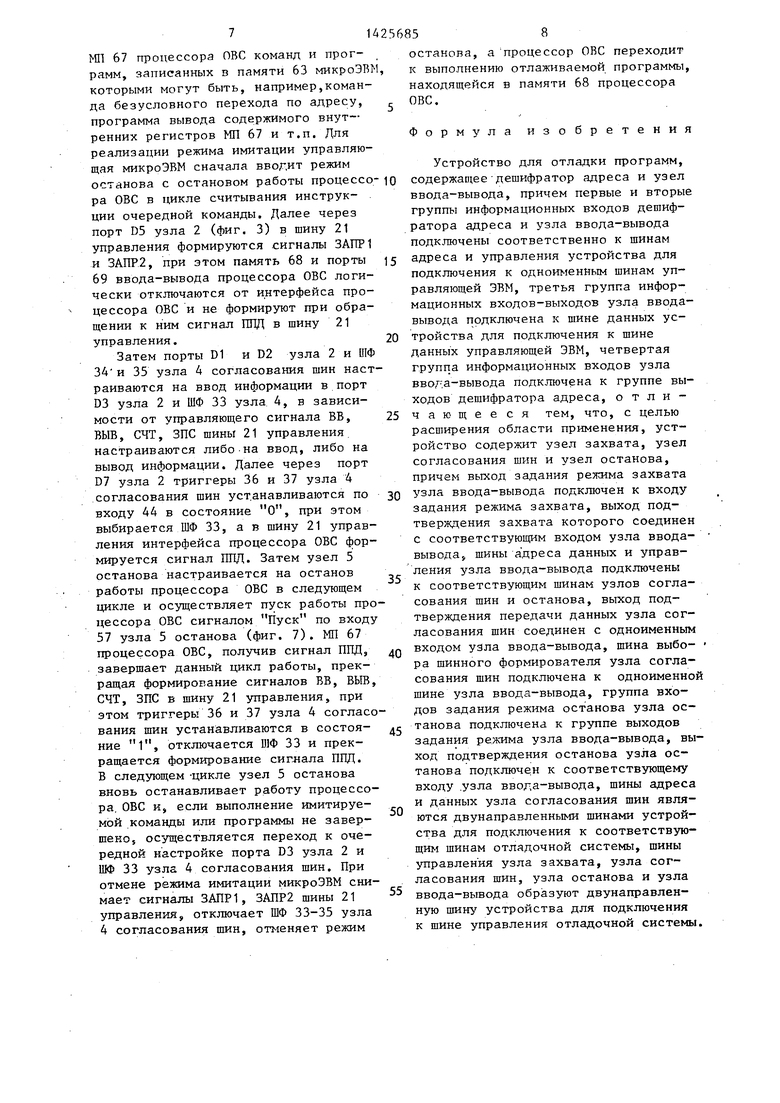

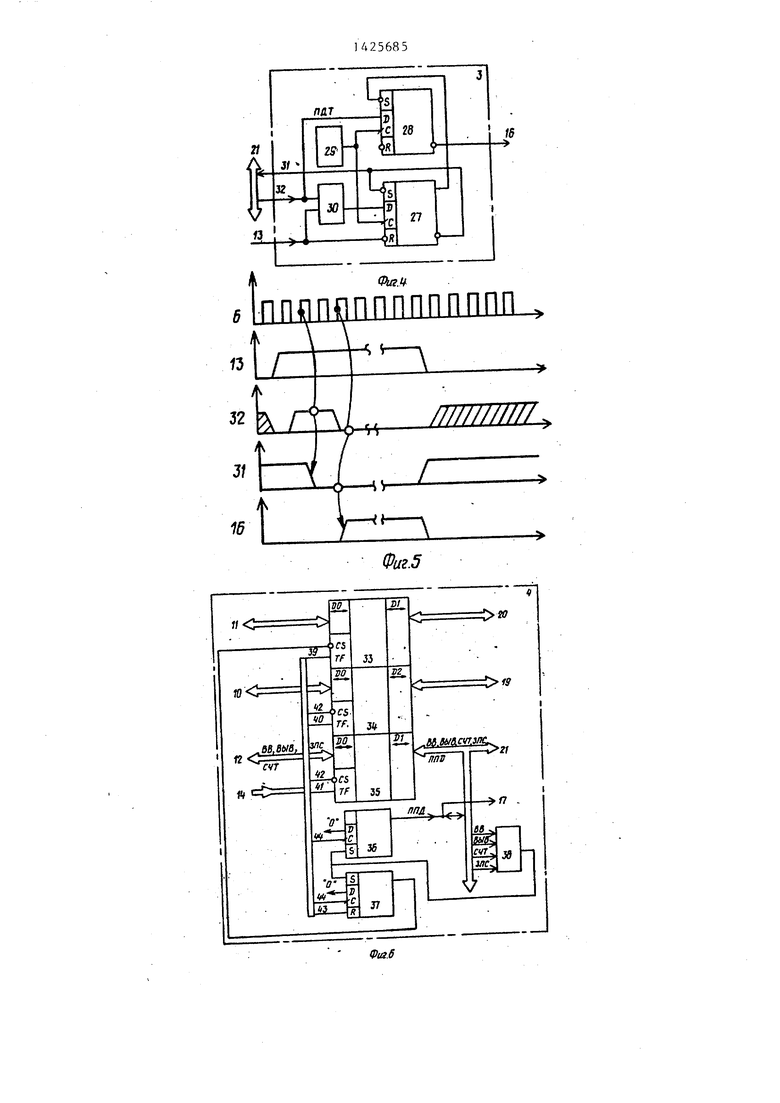

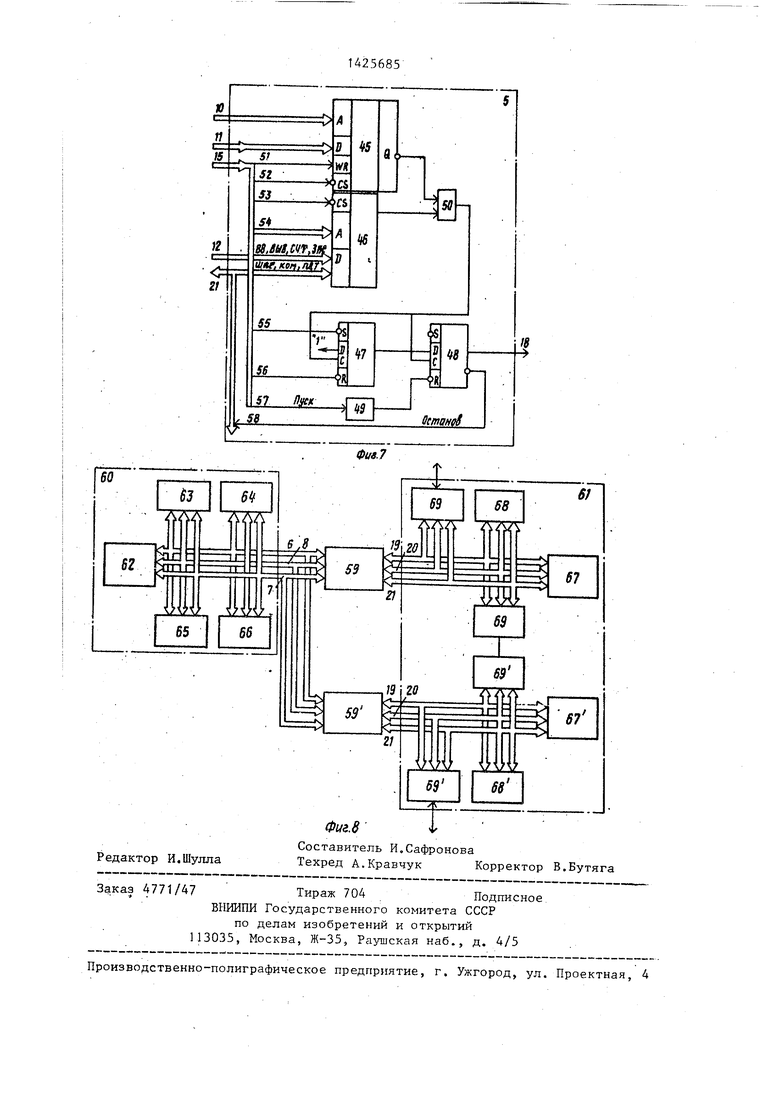

программJ на фиг. 2 - функциональная схема дешифратора адресаj на фиг, 3- функциональная схема узла ввода-вывода,- на фиг. 4 - функциональная схема узла захвата на фиг. 5 - временная диаграмма работы узла захвата-, на фиг. 6 - функциональная схе- ма узла согласования шин;на фиг.7 - функциональная схема узла останова; на фиг, 8 - структурная схема отладочного комплекса.

Устройство для отладки программ (фиг. 1) содержит дешифратор 1 адреса, узел 2 ввода-вывода, -узел 3 захвата, узел 4 согласования шин, узел 5 останова, шины адреса 6 и управления 7, входную шину 8 данных, третью группу входов 9 узла ввода-вывода, шины адреса 10, данных 11, управления 12 узла согласования шин, вход 13 режима захвата, вход 14 выбора шинного формирователя, вход 15 режима останова, выход 16 подтверждения режима захвата узла захвата, выход 17 подтверждения передачи данных узла согласования шин, выход 18 подтверждения останова узла останова, выходные шины адреса 19, данных 20, управления 21 устройства.

Дешифратор 1 адреса предназначен для идентификации портов ввода-вывода устройства для отладки программ в адресном пространстве управляющей микроэвм и содержит (фиг. 2) элемент 22 постоянной памяти и элемент 23 задержки. Элемент 22 осутцествляет дешифрацию сигналов адреса шины 6 при наличии сигналов ВВ или ВЫВ шины 7 управления и формирует индивидуальные сигналы выборок (ВБ1-ВБЗ) на вход 9 и сигнал ППД который, проходя через элемент 23 задержки, поступает в шину 7 управления.

Узел 2 ввода-вывода предназначен для хранения информации, управляющей функционированием узлов захвата 3, согласования шин 4, и останова.5 при реализации отладочных режимов, а также для формирования сигналов запрета ОЗУ (ЗАПР1), запрета ПЗУ (ЗАПР2), сброса (СВР) шины 21 управления. Узел 2 содержит (фиг. 3) элементы 24- 26 параллельного интерфейса, каждый из которых содержит два восьмиразрядных и два четьфехразрядных порта ввода-вывода, каждый из которых может быть запрограммирован либо на ввод, либо на вывод информации.

Узел 3 захвата предназначен для реализации процедуры передачи управления шинами адреса 19, данных 20, управления 21 от процессора ОВС устройству для отладки программ. Узел 3 захвата (фиг. 4) содержит триггер 27 запроса захвата, триггер 28 подтверждения захвата, генератор 29, элемент И 30, выход 31 запроса захвата, вход 32 подтвержления захвата (ПДТ) шины 21 управления, выход 16 подтверждения режима захвата.

Узел 4 согласования шин предназначен для коммутации сигналов двунаправленных внутренних шин адреса 10, данных 11, управления 12 и соответствующих сигналов двунаправленных шин адреса 19, данных 20, управления 21, а .также для формирования сигнала ПГЩ в режиме имитации. Узел 4 (фиг. 6) содержит двунаправленные шинные формирователи (ШФ) данных 33, адреса 34, управления 35, триггер 36 подтверждения передачи данных,триггер 37 выбора ШФ 33 данных, элемент ИЛИ 38, входы 39-41 направления передачи данных, вход 42 выбора ШФ 34 и 35, вход 43 выбора ШФ 33, 44 стробирования триггеров 36 и 37.

Узел 5 останова предна значен для останова работы процессора ОВС по одному из предварительно заданных адресов останова и условию обмена и

роЭВМ 60. НГМД 65 может быть исполь-, зован также для хранения отлаживаемых программ и промежуточных результатов отладки. Консоль 64 предназна-- чена для ввода пользователем командных слов, управляющих работой микро- ЭВМ 60 и устройства 59 для отладки программ, а также для ввода сообще10 НИИ, формируемых в процессе отладки. Протокол отладки может быть выведен на печать 66.

Устройство для отладки программ имеет режимы автонома, управления,

15 захвата, останова, имитации.

В режиме автонома управляющая мик- роЭВМ, настраивая порты узла 2, устанавливает узлы захвата 3, согласования шин 4 и останова 5 в исходное

20 состояние, при этом отменяются все ранее введенные отладочные режимы, устройство для отладки программ ло- гичебки отключается от шин адреса 19, данных 20, управления 21 и не влияет

25 на работу процессора ОВС.

В режиме управления управляющая, микроэвм, осуществляя ввод информации в порт D5 узла 2 имеет возможность 30 формировать в шину 21 управления сигналы СВР, ЗАПР1, ЗАПР2, которые осуществляют начальную установку узлов процессора ОВС (СВР), логическое отк-

лючение от интерфейса процессора

содержит (фиг. 7) элемент ОЗУ 45 сравне- компонентов ОЗУ (ЗАПР1), компония,мультиплексор 46 условий обмена,нентов ПЗУ (ЗАПР2), входящих в состриггер 47 режима, триггер 48 остано-тав памяти 68 процессора ОВС (фиг.8),

ва, формирователь 49 короткого им-логическое отключение от интерфейса

пульса, элемент И 50, вход 51 запи-процессора ОВС портов 69 ввода-вывоси и вход 52 выбора ОЗУ 45 сравнения, 40Д (ЗАПР2) .

вход 53 выбора мультиплексора 46, группу входов 54 выбора информационного входа мультиплексора 46, входы 55 и 56 задания режима, вход 57 отмены режима останова, выход 58 останова работы процессора ОВС. На фиг.8 отмечены устройство 59 для отладки программ, микроэвм 60, ОВС 61, МП 62, память 63, консоль 64, накопитель 65 на гибких магнитных дисках (НЩД) , 66, МП 67 ОВС, память 68 ОВС, порты 69 .ввода-вывода.

Устройство работает следующим образом.

Все отладочные процедуры, реализуемые устройством 59 для отладки программ, осуществляют под управлением программы, загружаемой в память 63 с НГЩ 65 и выполняемой МП 62 микВ режиме захвата устройство 59 для отладки программ (фиг. 8) представляет пользователю возможность обмена данными между памятью 63 универсаль- 45 ной микроэвм 60 с одной стороны, памятью 68 и портами 69 ввода-вывода процессора ОВС с другой стороны, а также осуществлять чтение и модификацию памяти 68 и портов ввода-вывода 69 в режиме прямого доступа. Ввод режима захвата инициируется сигналом порта D7 на выходе 13 узла 2 ПВВ (фиг. 3). Вход в режим захвата подтверждается сигналом на выходе 16 узла 3 захвата, после чего микроэвм настраивает ШФ 34 и 35 узла 4 согласования щин (фиг. 6) и порты D1, D2 ПВВ (фиг. 3) на вывод адреса и вводит в них информацию адреса

50

55

роЭВМ 60. НГМД 65 может быть исполь-, зован также для хранения отлаживаемых программ и промежуточных результатов отладки. Консоль 64 предназна-- чена для ввода пользователем командных слов, управляющих работой микро- ЭВМ 60 и устройства 59 для отладки программ, а также для ввода сообще0 НИИ, формируемых в процессе отладки. Протокол отладки может быть выведен на печать 66.

Устройство для отладки программ имеет режимы автонома, управления,

5 захвата, останова, имитации.

В режиме автонома управляющая мик- роЭВМ, настраивая порты узла 2, устанавливает узлы захвата 3, согласования шин 4 и останова 5 в исходное

0 состояние, при этом отменяются все ранее введенные отладочные режимы, устройство для отладки программ ло- гичебки отключается от шин адреса 19, данных 20, управления 21 и не влияет

5 на работу процессора ОВС.

В режиме управления управляющая, микроэвм, осуществляя ввод информации в порт D5 узла 2 имеет возможность 0 формировать в шину 21 управления сигналы СВР, ЗАПР1, ЗАПР2, которые осуществляют начальную установку узлов процессора ОВС (СВР), логическое отк-

В режиме захвата устройство 59 для отладки программ (фиг. 8) представляет пользователю возможность обмена данными между памятью 63 универсаль- 5 ной микроэвм 60 с одной стороны, памятью 68 и портами 69 ввода-вывода процессора ОВС с другой стороны, а также осуществлять чтение и модификацию памяти 68 и портов ввода-вывода 69 в режиме прямого доступа. Ввод режима захвата инициируется сигналом порта D7 на выходе 13 узла 2 ПВВ (фиг. 3). Вход в режим захвата подтверждается сигналом на выходе 16 узла 3 захвата, после чего микроэвм настраивает ШФ 34 и 35 узла 4 согласования щин (фиг. 6) и порты D1, D2 ПВВ (фиг. 3) на вывод адреса и вводит в них информацию адреса

0

5

управления, которая поступает соответственно на шины адреса 10 и 19 и , управления 12 и 21 ,В зависимости от направления передачи данных ШФ 33 узла 4 согласования шин и порт 1)3 данных узла 2 ПВВ настраиваются либо на ввод, либо на вывод информации. Память 68 или порты 69 ввода-вывода процессора ОВС в ответ на обращение формируют Q сигнал ППД которьш с шины 21 управления через узел 4 согласования шин поступает на вход 17 порта D4 узла 2. В ответ на сигнал ППД управляющая микроэвм отменяет управляющую инфор- мацию в порте D2 узла 2, что вызывает отмену сигнала ППД и завершает цикл обмена. При. отмене режима захвата сначала осуществляется отключение ШФ 33-35 узла 4 согласования шин а 20 затем отменяется сигнал ввода режима захвата на выходе 13 узла 2.

В режим останова устройство для отладки программ предоставляет пользователю осуществлять останов работы 25 процессора ОВС по условию обмена и адресам останова, а также по совпадению условия и адреса останова, указанных в формате командного слова, вводимого с консоли 64 управляющей 0 микроэвм (фиг. 8), Число задаваемых адресов останова не ограничивается.В качестве условия обмена могут быт ь использованы следующие сигналы шины 21 управления интерфейса процессора ОВС: ВВ, ВЫВ, СЧТ, ЗПС, формируемые МП 67 при обращении к памяти 68 и портам 69 ввода-вывода- ШАГ, формируемый в каждом цикле выбора инструкции команды; ПДТ, формируемый при

40

реализации процедур прямого доступа в интерфейсе процессора ОВС, Реализация режима начинается с настройки управляющей микроэвм 60, узла 5 останова через узел 2, для этого предварительно отключаются ШФ 33-35 узла 4 согласования шин. Если в формате командного слова, вводимого с консоли .64 микроэвм, указаны адреса точек оста- .нова, то порты D1 и D3 узла 3 настраиваются на вывод и микроэвм, вводя в них информацию об адресах, данных и используя порт D6 узла 2, осуществляет запись в ОЗУ 45 сравнения сначала логических нулей по всем адресам, а затем по адресам, указанным в формате командного слова - логических единиц, после чего ОЗУ, порт D6 узла 2 мультиплексор 46 настраиQ 0

5 0

0

5

0

5

ваются на выбор условия обмена, указанного в формате командного слова. Затем порты D1-D3 узла 2 и ШФ 33-35 узла 4 согласования шин настраиваются на ввод, при этом в шины адреса 10, данных 11, управления 12 транс- . лируются соответствующие сигналы шин адреса 19, данных 20, управления 21, Далее управляющая микроЭВМ 60 через порт D6 узла 2, устанавливая в соответствующее состояние триггеры 47 режима узла 5 останова, осуществляет ввод режима останова и приступает к анализу сигнала подтверждения режима останова на выходе 18 узла 5 останова, формируемого при совпадении кода адреса на шине 19 адреса и условия обмена на шине 21 управления с заданными в формате командного слова. При подтверждении режима останова на консоль 64 микроЭВМ вы- водится сообщение, содержащее информацию о состоянии шин адреса 19, данных 20, управления 21 и интерфейса ОВС. Далее пользователь с консоли 64 микроэвм вводит командное слово, управляющее либо переходом к новой, следзтощей точке останова в режиме останова, либо завершением режима останова. Для перехода к следующей точке останова микроЭВМ через порт D6 узла 2 осуществляет либо отключение, либо выбор ОЗУ 45 сравнения, настраивает мультиплексор 46 на выбор УСЛОВИЯ обмена в соответствии с параметрами командного слова, устанавливает триггер 38 останова в состояние О, при этом возобновляется работа процессора ОВС по выполняемой программе. При отмене ре- жима останова микроЭВМ через порт D7 узла 2 отключает ШФ 33-35 узла 4 сотласования шин, а через порт D6 узла 2 устанавливает триггеры 48 и 47 в состояние О,

В режиме имитации устройство для отладки программ предоставляет пользователю возможность осуществлять запуск работы процессора ОВС с любо- го адреса, а также производить чтение и модификацию содержимого внутренних регистров МП 67 процессора ОВС, При реализации данного режима память 68 I и порты 69 ввода-вывода процессора ОВС подменяются портом ввода-вывода D3 узла 2 устройства для отладки программ, через который управляющая микроэвм 60 обеспечивает выполнение

МП 67 процессора ОВС команд и программ, записанных в памяти 63 микроЭБ которыми могут быть, например,команда безусловного перехода по адресу, программа вывода содержимого внутренних регистров МП 67 и т.п. Для реализации режима имитации управляющая микроэвм сначала вводит режим останова с остановом работы процессо ра ОВС в цикле считывания инструкции очередной команды. Далее через порт D5 узла 2 (фиг. 3) в шину 21 управления формируются сигналы ЗАПР1 и ЗАПР2, при этом память 68 и порты 69 ввода-вывода процессора ОВС логически отключаются от интерфейса процессора ОВС и не формируют при обращении к ним сигнал ППД в шину 21 управления.

Затем порты D1 и D2 узла 2 и ШФ 34 и 35 узла 4 согласования шин настраиваются на ввод информации в порт D3 узла 2 и ШФ 33 узла 4, в зависимости от управляющего сигнала ВВ, ВЫВ, СЧТ, ЗПС щины 21 управления настраиваются либо-на ввод, либо на вывод информации. Далее через порт D7 узла 2 триггеры 36 и 37 узла 4 согласования шин устанавливаются по входу 44 в состояние О, при этом выбирается ШФ 33, а в шину 21 управления интерфейса процессора ОВС формируется сигнал ППД. Затем узел 5 останова настраивается на останов работы процессора ОВС в следующем цикле и осуществляет пуск работы процессора ОВС сигналом Пуск по входу 57 узла 5 останова (фиг. 7). МП 67 процессора ОВС, получив сигнал ППД, завершает данный цикл работы, прекращая формирование сигналов ВВ, ВЬВ, СЧТ, ЗПС в шину 21 управления, при этом триггеры 36 и 37 узла 4 согласования шин устанавливаются в состоя- ние 1, отключается DIO 33 и прекращается формирование сиглала ППД. В следующем -цикле узел 5 останова вновь останавливает работу процессора, ОВС и, если выполнение имитируемой команды или программы не завершено, осуществляется переход к очередной настройке порта D3 узла 2 и ШФ 33 узла 4 согласования шин. При отмене режима имитации микроЭВМ снимает сигналы ЗАПР1, ЗАПР2 шины 21 управления, отключает ШФ 33-35 узла 4 согласования шин, отменяет режим

15

20

25

ю

дд

30

35

40

0

5

останова, а процессор ОВС переходит к выполнению отлаживаемой программы, находящейся в памяти 68 процессора ОВС.

Формула изобретения

Устройство для отладки программ, содержащее дешифратор адреса и узел ввода-вывода, причем первые и вторые группы информационных входов дешифратора адреса и узла ввода-вывода подключены соответственно к шинам адреса и управления устройства для подключения к одноименным шинам управляющей ЭВМ, третья группа информационных входов-выходов узла ввода- вывода подключена к шине данных устройства для подключения к шине данных управляющей ЭВМ, четвертая групп а информационных входов узла ввог.а-вывода подключена к группе выходов дешифратора адреса, отличающееся тем, что, с целью расширения области применения, устройство содержит узел захвата, узел согласования шин и узел останова, причем выход задания режима захвата узла ввода-вывода подключен к входу задания режима захвата, выход подтверждения захвата которого соединен с соответствующим входом узла ввода- вывода, шины а дреса данных и управления узла ввода-вывода подключены к соответствующим шинам узлов согласования шин и останова, выход подтверждения передачи данных узла согласования шин соединен с одноименным входом узла ввода-вывода, шина выбо- ра шинного формирователя узла согласования шин подключена к одноименной шине узла ввода-вывода, группа входов задания режима останова узла останова подключена к группе выходов задания режима узла ввода-вывода, выход подтверждения останова узла останова подключе;н к соответствующему входу .узла ввода-вывода, шины адреса и данных узла согласования шин являются двунаправленными шинами устройства для подключения к соответствующим шинам отладочной системы, шины управления узла захвата, узла согласования шин, узла останова и узла ввода-вывода образуют двунаправленную шину устройства для подключения к шине управления отладочной системы.

nnflnfinnnnnnnnn ,

r

J-A

7

////////////

Редактор И.Шулла

Фиа.8

Составитель И.Сафронова

Техред А.Кравчук Корректор В.Бутяга

| Устройство для отладки программ | 1982 |

|

SU1100627A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1984 |

|

SU1223236A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-02-24—Подача