18 фиксЛдни сигнала, триггер 19 управления выбором команды, элементы ИЛИ 2П-25, элементы И 26-35, элементы НЕ 365 37, стартовые регистры 38, 39, вхоц сброса 40, вход 41 строби- рующего сигнала, шину 42 стробирующе го сигнала, информационную шину, 43, выход 44 сигнала требования синхронисыва ся триггер 1ь, через элемент ИЛИ 15 триггеры 17, 1Н и триггер 14, который своим инверсным выходом сбрасываем трш геры 15 и 19. Поэтому первый после включения питания строб на шине 42 пройдет через элемент И 28 и на шинах 43 АДРЕС/ДАННЫЕ будет выставлен код 777. Процессор зацик

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с устройством ввода-вывода | 1984 |

|

SU1180911A1 |

| Мажоритарно-резервированная магистральная модульная вычислительная система | 1986 |

|

SU1457643A1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1982 |

|

SU1132282A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Устройство для сопряжения в резервированной многопроцессорной системе | 1987 |

|

SU1501079A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА И ВЫВОДА ДИСКРЕТНЫХ СИГНАЛОВ | 1989 |

|

RU2022344C1 |

| Устройство для сопряжения процессоров в мультипроцессорной системе | 1984 |

|

SU1188747A1 |

| Резервированное процессорное устройство | 1987 |

|

SU1594545A1 |

| Система отладки микропроцессорных устройств | 1989 |

|

SU1700559A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

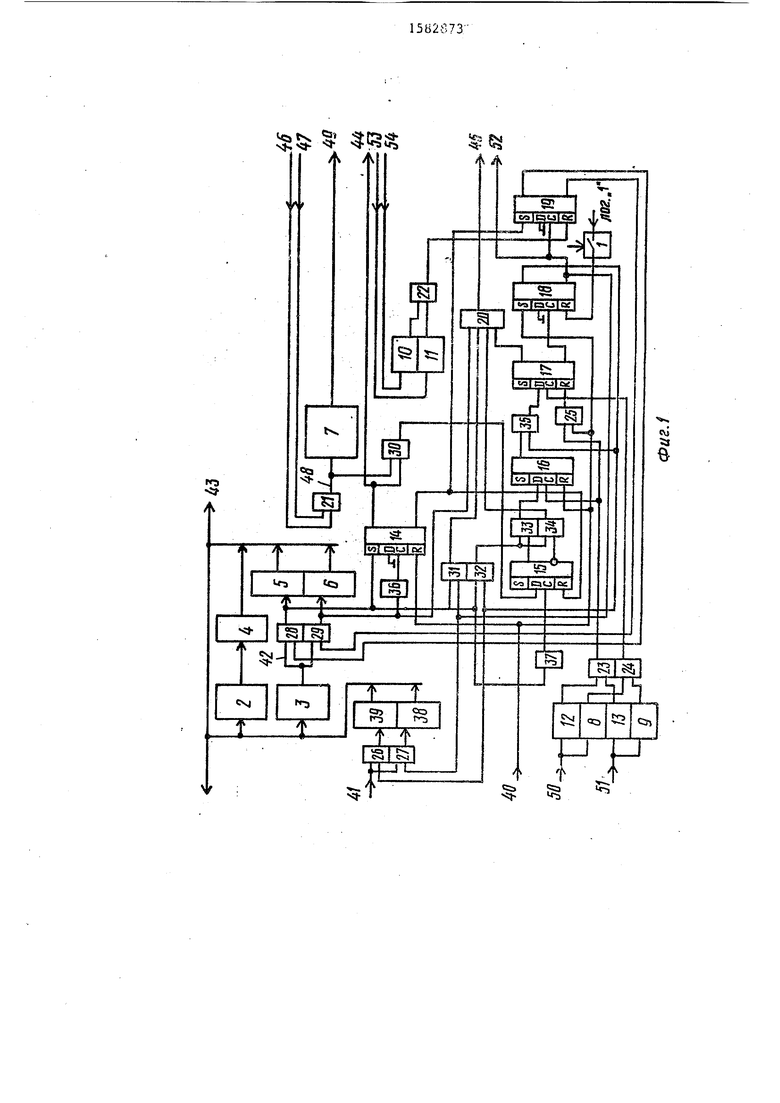

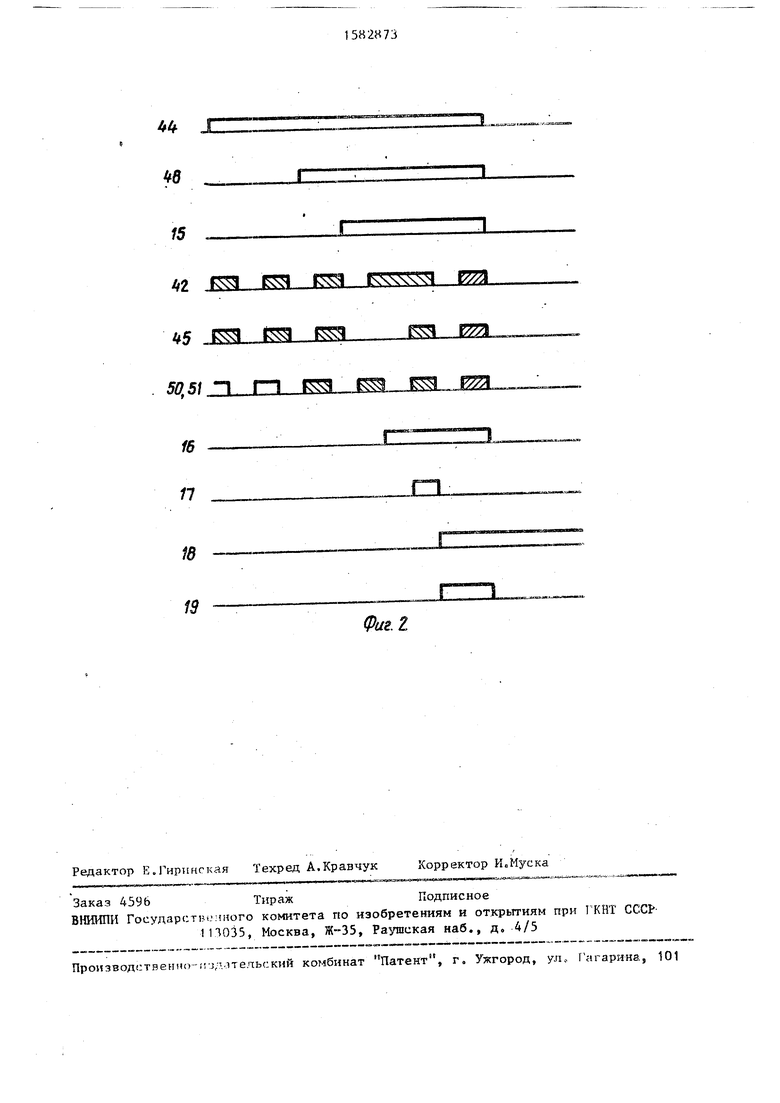

Изобретение относится к вычисли- тельной технике и может быть использовано в системах обработки информации высокой надежности. Цель изобретения - повышение надежности устройства. Устройство содержит переключатель режима работы, блоки выделения адреса, вентильные регистры, схему формирования сигнала требования прерывания, блоки вьщеления переднего и заднего фронтов сигнала, триггеры требования синхронизации, начала Изобретение относится к вычислительной технике и может быть использовано в системах обработки информации высокой надежности Цель изобретения - повышение наг. дежности устройства На фиг.1 представлена структурная схема устройства начальной синхронизации процессоров в резервированной .системе;на фиг.2 - временные диаграммы его работы синхронизации, фиксации переднего и заднего фронтов сигнала, фиксации сигнала, управления выбором команды, элементы И, ИЛИ, НЕ, стартовые регистры. Цель изобретения достигается тем, что вводимый в синхронный: режим работы процессор после включения зацикливается на исполнении команды безусловного перехода на саму себя. Работающие процессоры после обработки сообщения о таком состоянии вводимого процессора тоже переходят на выполнение той же команды. В этот момент происходит подсинхронизация фаз выполнения команды, а затем ее автоматическая подмена на другую, например на команду выхода из прерывания. Такой алгоритм начальной синхрониЗа- ции параллельно работающих процессоров позволяет проводить процесс синхронизации при выключенной системе прерываний, сделать его строго заданным по..времени и свободным от возможности появления неконтролируемых сбойных ситуаций, 2 ил. Устройство (фигоО содержит переключатель 1 режима работы, блоки 2, 3 вьщеления адреса, вентильные регистры 4, 5, 6, схему 7 формирования сигнала требования прерывания, блоки 8-11 вьщеления переднего фронта сигнала, блоки 12, 13 выделения заднего фронта сигнала, триггер 14 требования синхронизации, триггер 15 начала синхронизации, триггер 16 фиксации заднего фронта сигнала, триггер 17 фиксации переднего фронта сигнала, триггер (Л ел СО к 00 VI со

25

О

зации, выход 45 сигнала синхронизации, лится на этой команде, будет ее счи- входы 46, 47 сигналов требования синхронизации шину 48 сигнала требования синхронизации, выход 49 сигнала требования прерывания, входы 50, 51 сигналов синхронизации, выход 52 сиг- 15 нала фиксации фазы, входы 53, 54 сигналов требования фиксации фаз уст- роист ча,

схройхгво работает в двух режимах, эяцав.1,мых переключателем 1. Если 20 переключатель 1 замкнут (режим ведущий), триггер 1В независимо от сигнала на входе 40 Сброс будет находиться во взведенном состоянии высокий уровень на инверсном выходе) ,. В этом случае процессором по сгроиу на входе 41 через элемент Л 7 будет опрошен первый стартовый pel астр 3й и считан адрес 1М)000, ог орыч является начальным адресом р 1 Fаглил независимой работы ПрОЦеС- OpOB.

Еслп переключатель 1 разомкнут ведомый ), триггер 18 после сигнала на входе 40 Сброс останется ь сброшенной ее стоянии, Процессор, вътзаботзв послз включения питания строб ка входе ( 1 э через элемент II 2Ь считывает содержимое второго cTapiOJbcro регистра 39 - код

100(100. Затем обращается к регистру

1 troii 10000 С блок 2 выделения д( L а I- ентилъныь регистр 4) и 24 d e C код i/ЫЮО, который запи- cb FHf-тст: в счетчик команд для загруз- чи команд и их выполнения.

По адресу 176000 находится регистр с автоматически сменяемой информацией (блок 3 выделения адреса, вентильные регистры 5 и Ь, элементы II 2BS 29). В зависимости от состояния ipHvrepa 19 при nfip, щении к регистру Ь чли 6 может bin ъ считан код //7 или 2. Код 777 соответствует команде безусловного перехода на эту же команду,, а код / - команде выхода п прерывания

В режиме после включения

го сигналу на км ч ( Сброс свра-

ЗЬ

45

50

55

тывать и исполнять до тех пор, пока не произойдет подмены кода команды. Строб на шине 4 через злемен V 28, кроме того, взведет триггер i + (см. диаграмму на фиг.2) и в раСотаюш/ю часть мажоритарной системы поиде требование с выхода 44, .воря1чее о том, что включился новый процессор и требуется осуществить начальнур) сшг ронизап,ию. Строб ь.& лине 42, пройдя через элементы И 28, 32 и 34 и ИЛИ 20, формирует строб на выходе 45 синхрОд лзации, который сообщает процессору;, что данные на шинах 43 V.B данном случае; код 7/7) выставле™ ны« До появления строба на выходе 45 работа процессора приостанавливается.

Процессор будет находиться в ожидании (зациллен) с выставленным тре- ооваиием на синхронизацию на выходе 44 до тех пор, пока из работающей части системы не придет хотя бы один ответный сигнал требования синхронизации на входе 4b или 47. Эти ответные сигналы сформируют на выходе элемента ИЛИ 21 сигнал на шине 48.

Сигнал на шине 48 в работающих процессорах обрабатывается по-разному Сформированный во вводимом процессоре сигнал с выхода А4 поступает в работающий процессор в виде сигналов со входа 46 или 47, иоторме ераз элемент ИЛИ 21 и схему 7 п овут по явление сигнала требования прерывания на выходе 49. Работающие процессоры принимают сигнал с выхода -9 и входят в прерывание-подпрограмму начальной синхронизации. Триггер 18 находится во взведенном состоянии: пибо процессор был запущен в режим ведущий (переключатель 1 замкнут), либо с ним уже были прозедены операции начальной синхронизации, в результате которых триггер 18 оказывается Бчведенным. Поэтому, когда процессор переходит к самому моменту синхронизации (программная передача управген я на команду по адресу 17ЬООО) гтроб на шине 42 обходит схему подсмьхролчза-

5

О

лится на этой команде, будет ее счи- 5

0

Ь

5

0

5

тывать и исполнять до тех пор, пока не произойдет подмены кода команды. Строб на шине 4 через злемен V 28, кроме того, взведет триггер i + (см. диаграмму на фиг.2) и в раСотаюш/ю часть мажоритарной системы поиде требование с выхода 44, .воря1чее о том, что включился новый процессор и требуется осуществить начальнур) сшг ронизап,ию. Строб ь.& лине 42, пройдя через элементы И 28, 32 и 34 и ИЛИ 20, формирует строб на выходе 45 синхрОд лзации, который сообщает процессору;, что данные на шинах 43 V.B данном случае; код 7/7) выставле™ ны« До появления строба на выходе 45 работа процессора приостанавливается.

Процессор будет находиться в ожидании (зациллен) с выставленным тре- ооваиием на синхронизацию на выходе 44 до тех пор, пока из работающей части системы не придет хотя бы один ответный сигнал требования синхронизации на входе 4b или 47. Эти ответные сигналы сформируют на выходе элемента ИЛИ 21 сигнал на шине 48.

Сигнал на шине 48 в работающих процессорах обрабатывается по-разному. Сформированный во вводимом процессоре сигнал с выхода А4 поступает в работающий процессор в виде сигналов со входа 46 или 47, иоторме ераз элемент ИЛИ 21 и схему 7 п овут по явление сигнала требования прерывания на выходе 49. Работающие процессоры принимают сигнал с выхода -9 и входят в прерывание-подпрограмму начальной синхронизации. Триггер 18 находится во взведенном состоянии: пибо процессор был запущен в режим ведущий (переключатель 1 замкнут), либо с ним уже были прозедены операции начальной синхронизации, в результате которых триггер 18 оказывается Бчведенным. Поэтому, когда процессор переходит к самому моменту синхронизации (программная передача управген я на команду по адресу 17ЬООО) гтроб на шине 42 обходит схему подсмьхролчза-

ции фаз, собранную на базе триггеров 15, 16 и 17. Строб с шины 42 формирует сигнал на выходе 45 в этом случае через элементы К 28э ИЛИ 31 к 20„

После входа процессора в цикл взводится триггер 14 и сигнал с выхода 44 передается во вводимый процес- icop на вход 46 или 47. Сигнал с шины 48 во вводимом процессоре не вызывает прерывания, так как после включения питания все маски находятся в сброшенном сос тоянии. Триггер 14 уже взведен и сигнал с шины А8 через элемент К 30 устанавливает 1 на входе триггера 15, который будет взведен задним фронтом (т.е. после завершения очередной команды) строба с иины 4,2 через элемент И 28 и элемент КЕ37.

Взведение триггера 15 запрещает формирование сигнала на выходе 45 через элемент К 34„ Вновь пришедший строб с шины 42 установит на входе триггера 16 1 по цепи И 28, 32, 33. Триггер 16 будет взведен теперь после прихода первого заднего фронта сигналов со входа 50 или 51, транслируемых во вводимый процессор из работающих процессоров (с их выхода 45). Логическая 1 с входа триггера 16 через элемент И 35 поступает на вход .триггера 17, который будет взведен передним фронтом сигналов со входа 50 или 51 после первого заднего фронта тех же сигналов. Триггер 17 сбрасывается задним фронтом этих же сигналов. Таким образом, сигнал на выходе триггера 17 в момент синхронизации процессоров повторяет сигналы на входе 50 или 51. Сигнал с выхода триггера 17 через элемент ИЛИ 20 формирует поступающий на вход вводимого процес- сора сигнал с выхода 45, который был задержан до. момента прихода аналогичного сигнала из работающей системы.

Задним фронтом сигнала с выхода, триггера 17 взводится триггер 18, фиксирующий, что синхронизация процессоров, вводимого и работающих, произошла. При этом выключается схе- ма подсинхронизации фаз - изменяются сигналы на входах элементов И 31, 32,

Взведение триггера 18 вызывает установку триггера 19 как во вводимом процессоре, так и в работающих, в которые сигнал с выхода 52 -транслируется и поступает на вход 53 или 54. Триггер 19 переключает строб на шине 42 на выбор вентильного регистра 6

и} значит, на считывание процессорами вместо кода 777 кода 2 (на фиг.2 моменты считывания кода 777 отмечены тевой штриховкой, а кода 2 - правой), Считывание кода 2 (команды из прерывания) произойдет при следующем обращении процессоров к регистру 4 (при следующем формировании строба на шине 42)„ После чтения кода 2 по заднему фронту строба шины 42 через инвентор 36 будет сброшен триггер 14, что, в свою очередь,повлечет установку в- исходное состояние триггеров 15 и 19.

Таким образом, завершив начальную синхронизацию процессоров, предлагаемое устройство оказывается в состоянии, соответствующем режиму ведущий , а процессор, который вводился в работу, переходит в разряд работающих.

Формула изобретения

Устройство начальной синхронизации процессоров в резервированной системе, содержащее схему формирования сигнала требования прерывания, первый и второй блоки выделения адреса ко-- манды, первый и второй стартовые регистры, первый, второй и третий вен- тильные регистры, триггер требования синхронизации,.триггер начала синхронизации, триггер фиксации заднего фронта сигнала, триггер фиксации переднего фронта сигнала, триггер фиксации сигнала, триггер управления выбором команды, первый и второй элементы НЕ, первый-шестой элементы ИЛИ, первый-десятый элементы И, вход стробирующего сигнала устройства сое- динен с первыми входами первого и второго элементов К, выходы которых подключены к входам считывания соответственно первого- и второго стартовых регистров, выходы которых соединены с информационной шиной устройства, которая подключена к входам первого и второго блоков выделения адреса команды, выход первого из которых соединен со входом считывания первого вентильного регистра, выход которого и выходы второго и третьего вентильных регистров подключены к информационной шине устройства-,выход блока формирования сигнала требования прерывания является выходом сигнала требования прерывания устройства, выход третьего элемента К соеди-

ней с nncaiH первого „т&ыёнта Ч.% выход которого подключен к еинхрсвл суду триггера требования синхронизации, выход четвертого элементе F соединен с входом второго элемента HES вьгхог которого подключен к синхровходу триггера начала синхронизации, выход пятого элемента И соединен с первыми входами шестого и седьмого элементе а И, выход шестого элемента К подклю- чек к информационному входу триггера фиксации заднего фронта сигнала, выход первого элемента ИЛИ соединен с входом сброса триггера фиксаъки

переднего фронта сигнала „ инфоркащг- онньй вход которого подключен к вы-- ходу восьмого элемента Ч, выход второго элемента ИЛИ соединен с входом сброса триггера управления выбором команды, выход третьего элемента ШШ является выходом сигнала синхрониза- ции устройства, отличающееся ТЕМ, что, с целью повышения надежности устройства, в него введены переключатель режима работы, первый-1 четвертый блоки выделения переднего фронта сигналаs первый и второй блоки выделения заднего фронта сигнала, входы которых и входы пзрвого и вто- core блоков выделения переднего фронта сигнала подключены соответственно к первому и второму входам сигналов синхронизации -устройства, а выходы -.: соответствующем входа ч четвертого к пятого элементов ИЛИ, выход четвертого элемента ИЛИ соединен с первым входом первого элемента ИЛИ и синхро- входом триггера фиксации заднего фронта с-нгьалеЦ прямой выход которого coe динен с первым входом восьмого элемента Иэ выход пятого злемента RJTR подключен к синхровходу триггера фик- сяг ii переднего фронта сигнала, прямее выход которого соединен с первым входом третьего элемента ИЛИ, а ин- версный выход синхронходом триг- гера фиксации сигнала,.установочный вход которого подключеь ко второму входу первого элемента ИЛИ, входу

сброса устройства, входам установки в нуль1 триггера Ликс ции заднего фронта сигнала и рлггера требования

Ci-Jb-vpo 1. залЫл4 сДИЫ:ЧЛыЙ ВлОД КСТОрО -1

гг соединен с выходом четвертого эле- :менга И, инверсный выход - с входом установки Б нуль триггера начала синхронизации и вхоцоп тстановки в диницу триггера уаравления выбором команды} а прямой выход - с выходом сигнала требования синхронизации устройства и первым входом девятого элемента И, выход которого подключен к информационному входу триггеуч начала синхронизации, прямой и инверсный выходы которого соединены со втс рч-чи входами соответственно и седьмого элементов И, выход седьмого элемента И подключен к второму входу третьего злемента ИЛИ, третий и четвертый входы которого соединены с выходами соотве гтьгкно третьего

И неСЯТСК С ЭЛк МЬН Г ОВ К, ВХОД ЛОГИЧЕСКОЙ единицы ус/рсйства подключен к инфоргзиконному яходу переключателя режима ра, иты, управляюв ий вход, - к управляющему входу устройства, а выход ™ к зхоцу установки в ну/:ь триггера ф ксации сигнала, прямой выход чото/ого o ;клюreн ко вторг.м вхо- 1,см о, гятогс ч Coii O эль- i ertiOB И, а инвгрсный БЬРСОД - к выходу сигнала fHKcas MH фпзы устройства вторым входом второго и десятого эле- MeiiTuB И и слнхро эходу управления ЗЫбсрОМ KC tlUbi, ,/3.С И И№

веусный лы.ходы кот jyo.ro jочинены с первый илодаьи эотвкгсгвенно третьего и чечвертсго зл нентов И8 вторые входы которых под.лючены к выходу второго блока т щелен-гя адреса команды, лерг: и и зкоды сигналов требования м: кса.ч Лаз утройцт- ва соединены с вхо ани сотзл ственяо третьего и четвертого блок j выделения переднего фронта iv. i, зиходы которых подключены к со IT ггтзующим входам второго эленепта , первый и второй входы сигналов г чбор1лия синхронизации устройства оединены с соответствующими в «v u л ми п.естого элемента ИЛИ} выход кптг гп подключен ко BTOpCif/ вход/ де ято Ч) элемента К и входу схемы ( я сигнала требова гая гр рчвавия.

44 JC

W 15 ..

42 КЯ ЕчУЧчЧЧЧ №Я

45 E5S3 Ф7Л

50,51 П . . П f 1 .J55a.JESL

w

(put I

| ТИИЭР, т, 66, (Г 10, 1978, с | |||

| Приспособление для останова мюля Dobson аnd Barlow при отработке съема | 1919 |

|

SU108A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-10-23—Публикация

1988-12-27—Подача