с;

i b,f., , f. 0, если a;+bi-bf.,s (2)

а,- Ч- b;-t-f;, -s, если a.-i-b--ff. g

При сложении операндов Я b- и тг « /л.

f., Образуются величины: 4 формирования переноса

1:- всличипы.формируется перенос V; и сигнал V;

2--a, -t-b., с + J c-S,+l-S, (3)распространения переноса, согласно

одна из которых должна быть переданаследующим правилам: На выход S-сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор в системе остаточных классов | 1983 |

|

SU1111170A1 |

| Запоминающее устройство с переменным форматом данных | 1981 |

|

SU987678A1 |

| Арифметическое устройство по модулю | 1986 |

|

SU1425666A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Устройство для округления числа в системе остаточных классов | 1980 |

|

SU951305A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

Изобретение относится к вычислительной технике и может быть Hct пользовано для построения быстродействующих арифметических устройств, работающих как в двоичной, так и в позиционно-остаточной системах счисления. Целью изобретения является ; уменьшение объема оборудования. Цель достигается тем, что сумматор, содержащий первую группу коммутаторов 1, блок 4 формирования переноса, блок 5 формирования коррекции, труп-; пу матриц 9 элементов И, группу блоков 10 элементов ИЛИ, группу шифра- : торов 11, группу регистров 12, пер- I вую и вторую группы дешифраторов 18,: 19, содержит элемент ИЛИ 14, элемент 15 задержки, вторую группу коммутаторов 16 и группу блоков 17 хранения констант с соответствующий связями., 2 ил. 1

Г О , если S

V .

I, если Ь S,

V, ,

В блоке 5 по анализу величин r , V, и входного переноса f ,-, формируется выходной перенос f; и адрес блока 17 хранения констант.

В каждом из блоков 17 хранения констант группы размещены константы вида К 0,1 - S, 1 - s , причем, константы - S и 1 - S хранятся в дополнительном коде.

Блок 4 формирования переноса может быть реализован согласно прототипу в виде блока постоянной памяти или комбинационным.

Каждьй из группы шифраторов 11 формирует на своих выходах двоичный код величины, поступивший на вход, по соответствующим основаниям.

О, если

i S если S-1,

(4)

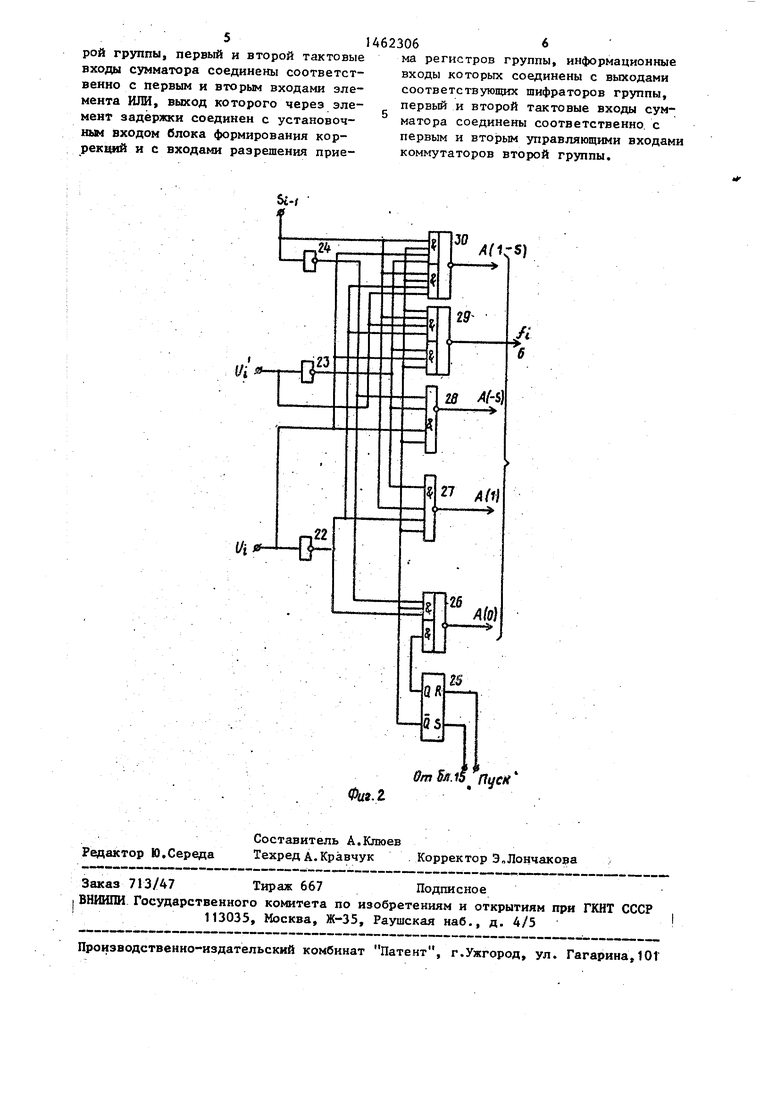

Сумматор работает в два такта. По входу 7 триггер 25-блока 5 ус- танавливается в исходное (нулевое) положение,

В первом такте по входу 2 подается первый тактовый сигнал, открьюаю- щий коммутаторы 1 и 6 первой и второй групп по первым ии юрмационным входам Операнды а- .:и Ь- с входов 20 и 21 сумматора проходят через коммутаторы групп 1 и 16 через дешифраторы 18 и 19 первой и второй групп и поступают на входы матриц элементов И группы, на выходах которых образуется сумма (а.+Ь) по соответствующим основаниям. Блоки 10 элементов ИЛИ группы преобразуют ре

зулнтат суммирования с выходов матриц 9 элементов И группы в код один из р. , который поступает на входы блока 4 формирования переноса и на входы соответствующих шифраторов 11 группы, где по каждому основанию об разуется двоичный код Через время, определенное временем задержки сра- батьшания элементов блоков 1, 18, 9, ;10 и 11, первый тактовый сигнал пройдя элемент ИЛИ 14 и элемент 15 задержки поступит на входы приема информации регистров 12 группы и запишет в них. результат суммирования

и сигнал переноса f в следующий S-й разряд

. V,. V V; - f,-., V. (6)

Через открытые по вторым информационным входам коммутаторы 1 и 16 групп и одна из констант с блоков 17 группы и содержимое регистров 12 группы проходят дешифраторы 18 и 19 групп и поступают на входы матриц 9 группы, на выходе которых формируется результат (а;+Ь, +К). На блоках элементов ИЛИ 10 группы и шифраторах 11 группы результат суммирования преобразуется в код (1 из Р;), а затем, в код COKj который заносится на регистры 12 группы.

Формула изобретения

S-й сумматор, содержащий первую группу коммутаторов, блок формирования переноса, блок формирования коррекции, группу матриц элементов И, группу блоков элементов ИЛИ,группу шифраторов, группу регистров, первую и вторую группы дешифраторов, причем выходы дешифраторов первой и второй группп соединены соответственно с первыми и вторыми группами входов соответствующих матриц элементов И группы, В1зкоды которых соединены с входами соответствующих блоков элементов И группы, выходы которых соединены с входами соответствующих шифраторов группы и соответству- гацими входами блока формирования переноса, выходы перекоса и условия

5

62306

На этом заканчивается первый такт работы сумматора.

Во втором такте по входу 3 подается второй тактовый сигнал, открывающий коммутаторы 1 и 16 первой и второй групп по вторым информационным входам. К этому моменту времени блок 4 формирования переноса вьщал

10 блок 5 сигналы v и vj, сформированные в соответствии с (4), а блок 5 на основе этих сигналов и значения сигнала f,-., (Оили) сформировал. адрес (А) блоков 17 хранения кон- 15 стант по правилу

() ()

, (к -S)

V. ()

(5)

распространения переноса которого соединены соответственно с первым и вторым информационными входами блока 25 формирования коррекции, третий информационный вход которого соединен с входом переноса сумматора, вход запуска и выход переноса которого соединены соответственно с входом сбро- 0 са и первым выходом блока формирования коррекции, первый и второй тактовые входы сумматора соединены соответственно с первыми и вторыми управляющими входами коммутаторов первой 5 группы, выходы регистров группы являются выходом суммы сумматора, о т - личающийся тем, что, с целью уменьшения объема оборудования, он содержит элемент задержки, эле- 0 мент ИЖ, вторую группу коммутаторов и группу блоков хранения констант, причем второй выход блока формирования коррекции соединен с адресными входами блоков хранения констант 5 группы, входы первого слагаемого группы сумматора и выходы блоков хранения констант группы подключены соответственно к первым и вторым информационным входам соответствующих 0 коммутаторов первой группы, выходы которых соединены с входами соответствующих дешифраторов первой группы, входы второго слагаемого группы сумматора и выходы регистров группы под- 5 ключены соответственно к первым и вторым информационным входам соответствующих коммутаторов второй группы, выходы которых соединены с входами соответствующих дешифраторов второй группы, первый и второй тактовые входы сумматора соединены соответственно с первым и вторым входамн элемента ИЛИ, выход которого через элемент задержки соединен с установоч- тм входом блока формирования коррекций и с входами разрешения приеUi 22(/ js-J-g

Фи.г

14623066

ма регистров группы, информационные входы которых соединены с выходами соответствующих шифраторов группы, первый и второй тактовые входы сумматора соединены соответственно, с первым и вторым управляющими входами коммутаторов второй группы.

A(i S)

ffmSjfA

| Устройство для суммирования в избыточной системе счисления | 1985 |

|

SU1290314A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1987-07-01—Подача