с момента совпадения кодов в блоке 5 по азрядного сравнения кодов до но- ;вого совпадения кодов делитель 8 частоты проходит все П состояний, независимо от состояния, в котором нахо- дится реверсивный счетчик 4.

При расстройке по фазе между двумя моментами совпадения кодов пройдет П+1 или П-1 состояний делителя 8 частоты за счет изменения состояния реверсивного 4 под действием сигналов коррекции, которые формируются реверсивным усреднителем 3, импульсно-фазовым детектором 2 и блоком 1.

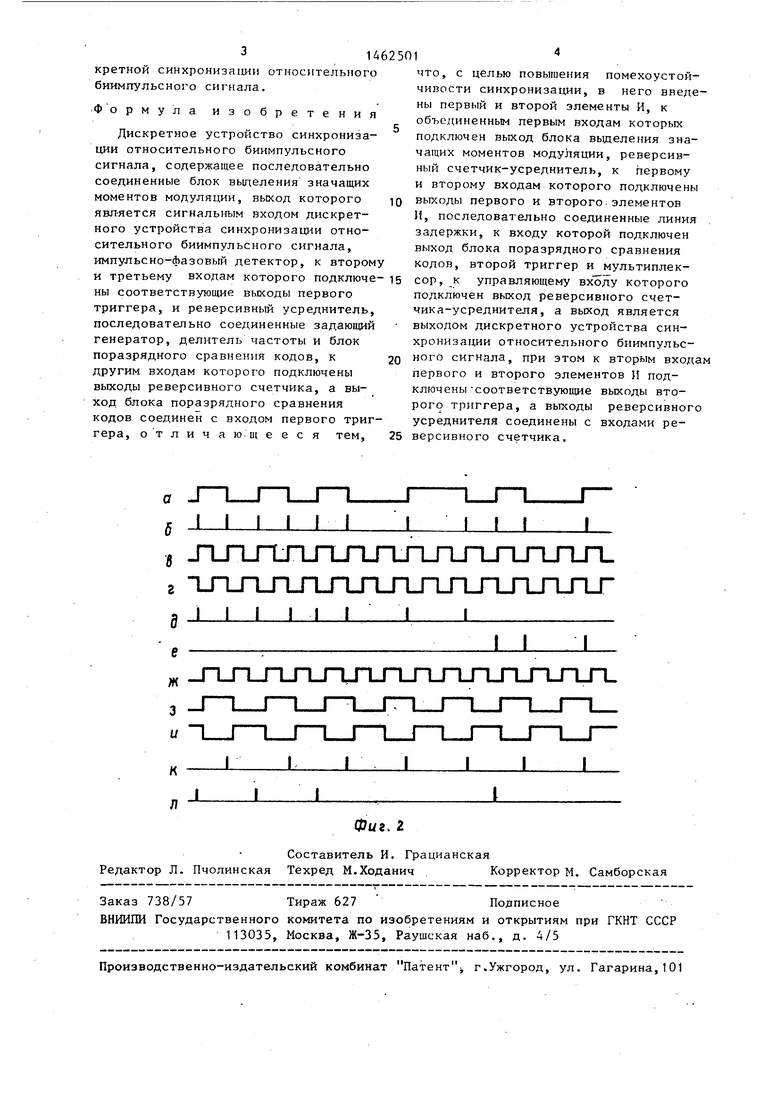

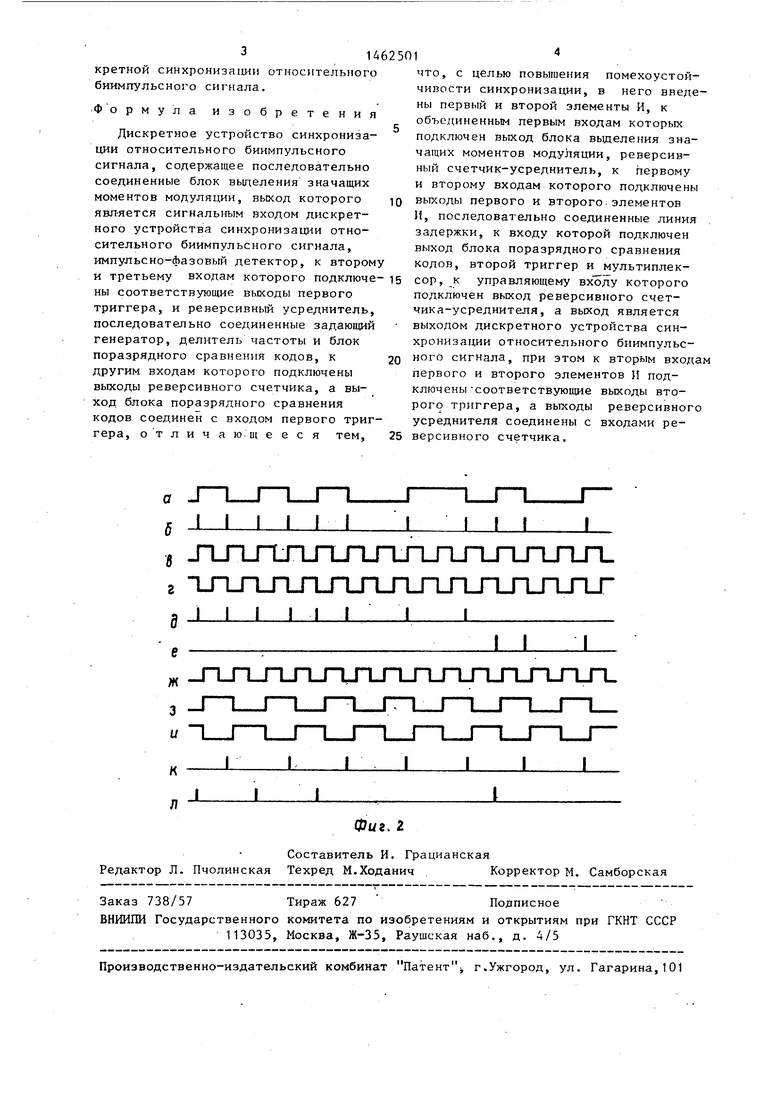

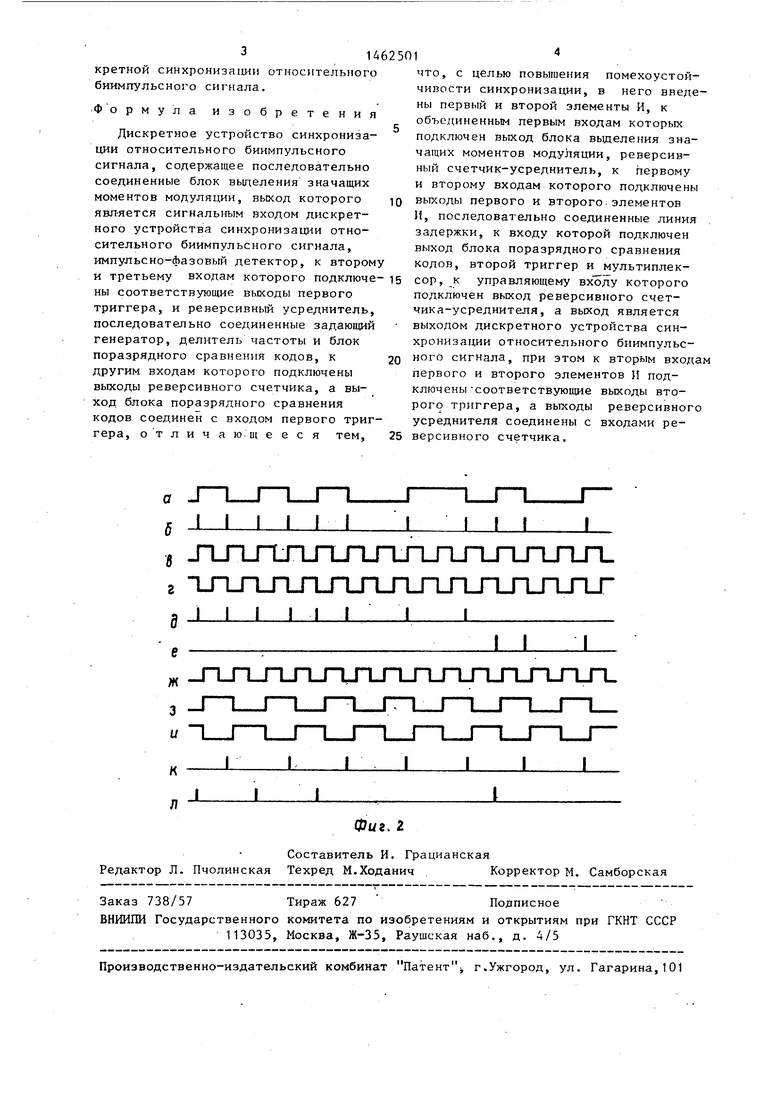

Блок 1 выделения значащих моментов модуляции вьщеляет из относительного биимпульсного сигнала (фиг. 2а) значащие моменты модуляции (фиг, 26),

5

0

5

с его выхода пропускает через мультиплексор 13 сигнал с первого выхода второго триггера 10 или с второго выхода второго триггера 10 соответственно.

Коммутация парафазных тактовых сигналов путем подсчета числа четных и нечетных импульсов, соответствующих значащим моментам модуляции относительного биимпульсного сигнала, поз- .воляет исключить неоднозначность выделения тактовой частоты. Использование всех значащих моментов модуляции относительного биимпульсного сигнала, поступающих с выхода блока 1 для формирования парафазных тактовых сигналов, повышает точность и помехоустойчивость устройства дискретной синхронизации относ1гтельного биимпульсного сигнала.

Ф о

.мула изобретения

Дискретное устройство синхронизации относительного биимпульсного сигнала, содержащее последовательно соединенные блок выделения значащих моментов модуляции, выход которого явл-яется сигнальным входом дискретного устройства синхронизации относительного биимпульсного сигнала, импульсно-фазовый детектор, к втором и третьему входам которого подключе мы соответствующие выходы первого триггера, и реверсивный усреднитель, последовательно соединенные задающий генератор, делитель частоты и блок поразрядного сравнения кодов, к другим входам которого подключены выходы реверсивного счетчика, а выход блока поразрядного сравнения кодов соединен с входом первого триггера, обличающееся тем,

что, с целью повышения помехоустойчивости синхронизации, в него введены первый и второй элементы Pi, к объединенным первым входам которых подключен выход блока вьщеления значащих моментов модуляции, реверсивный счетчик-усреднитель, к первому и второму входам которого подключены выходы первого и второго.элементов И, последовательно соединенные линия задержки, к входу которой подключен выход блока поразрядного сравнения кодов, второй триггер и мультиплексор, к управляющему вх од у которого подключен выход реверсивного счетчика-усреднителя, а выход является выходом дискретного устройства синхронизации относительного биимпульсного сигнала, при этом к вторым входам первого и второго элементов И подключены-соответствующие вькоды второго триггера, а выходы реверсивного усреднителя соединены с входами реверсивного счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выделения тактовых импульсов | 1982 |

|

SU1062880A1 |

| Устройство для измерения отношения частот последовательностей импульсов | 1988 |

|

SU1599793A1 |

| Устройство синхронизации с фазовой автоподстройкой частоты | 1988 |

|

SU1700751A1 |

| Управляемая линия задержки | 1990 |

|

SU1725370A2 |

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

| Преобразователь дельта-модулированного сигнала в сигнал с импульсно-кодовой модуляцией | 1984 |

|

SU1216831A1 |

| Цифровой приемник дельта-модулированных сигналов | 1989 |

|

SU1732499A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1988 |

|

SU1569983A1 |

| Преобразователь линейного перемещения в код | 1984 |

|

SU1274156A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости хсинхронизации. Устр-во содержит блок вьщеления 1 значащих моментов модуляции, импульс- но-фазовый детектор 2, реверсивный усреднитель 3, реверсивный счетчик 4, блок поразрядного сравнения 5 кодов, триггеры 6 и 10, задающий г-р 7, делитель 8 частоты, линию задержки 9, эл-ты И 11 и 14, реверсивный счетчик-усреднитель 12 и мультиплексор 13. Коммутация парафазных тактовых сигналов путем подсчета числа четных и нечетных импульсов, соответствующих значащим моментам модуляции относительного биимпульсного сигнала (ОБС), позволяет исключить неоднозначность вьоделения тактовой частоты. Использование всех значащих моментов модуля-; ции ОБС, поступающих с выхода блока выделения 1, для формирования пара- фазных тактовых сигналов повышает точность и помехоустойчивость синхронизации ОБС. 2 ил. о tfi (/

I I 1 I 1 i

а

e JlJljnJljnLJljnLJlJlJ

г IJnJTJbnJTJlJTJlJ JnJlJ I i I I I J I I

ж jnjn ruTjnj4JTjnLja.njTjnjijn

Составитель И. Грацианская Редактор Л. Пчолинская Техред М.Ходанич . Корректор м. Самборская

Заказ 738/57Тираж 627Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

1

I t I

II

Фиг. 2

| Авторское свидетельство СССР № 573897, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-02-28—Публикация

1986-08-22—Подача