lu а СП

(X

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования двух чисел с плавающей запятой | 1985 |

|

SU1405049A1 |

| Устройство для суммирования нормализованных чисел с плавающей запятой | 1987 |

|

SU1418704A1 |

| УСТРОЙСТВО СОВМЕСТНОГО КОДИРОВАНИЯ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497180C1 |

| Преобразователь комплексных сигналов | 1983 |

|

SU1104525A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ СОВМЕСТНО ХРАНИМЫХ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497179C1 |

| Цифровое устройство для вычисления обратной величины | 1983 |

|

SU1171783A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для нормализации чисел | 1986 |

|

SU1307454A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

Изобретение относится к цифровой вычислительнор1 технике и может - быть использовано при построении арифметических устройств вычислительных машин, а также в устройствах цифровой обработки сигналов. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что в устройство, содержащее . Шифратор 3 приоритета, мультиплексоры 6,7, блок 8 формирования порядка и кода нормализации и сумматор 9 округления, введена схема 10 .сравне- , ния с константой с соответствующими связями. 2 ил.

фигЛ

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении арифметических устройств вычислительных машин, а также в устройствах цифровой обработки сигналов,, работающих в системе счисления с плавающей запятой.

Цель изобретения - повышение быстродействия.

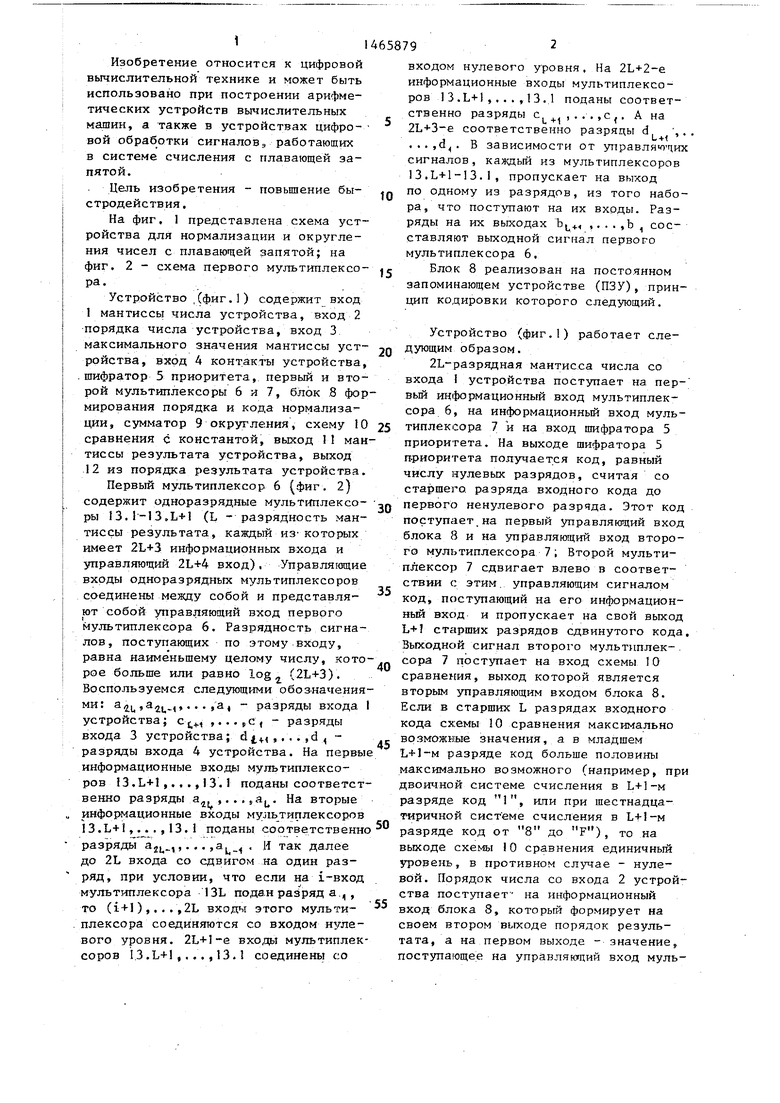

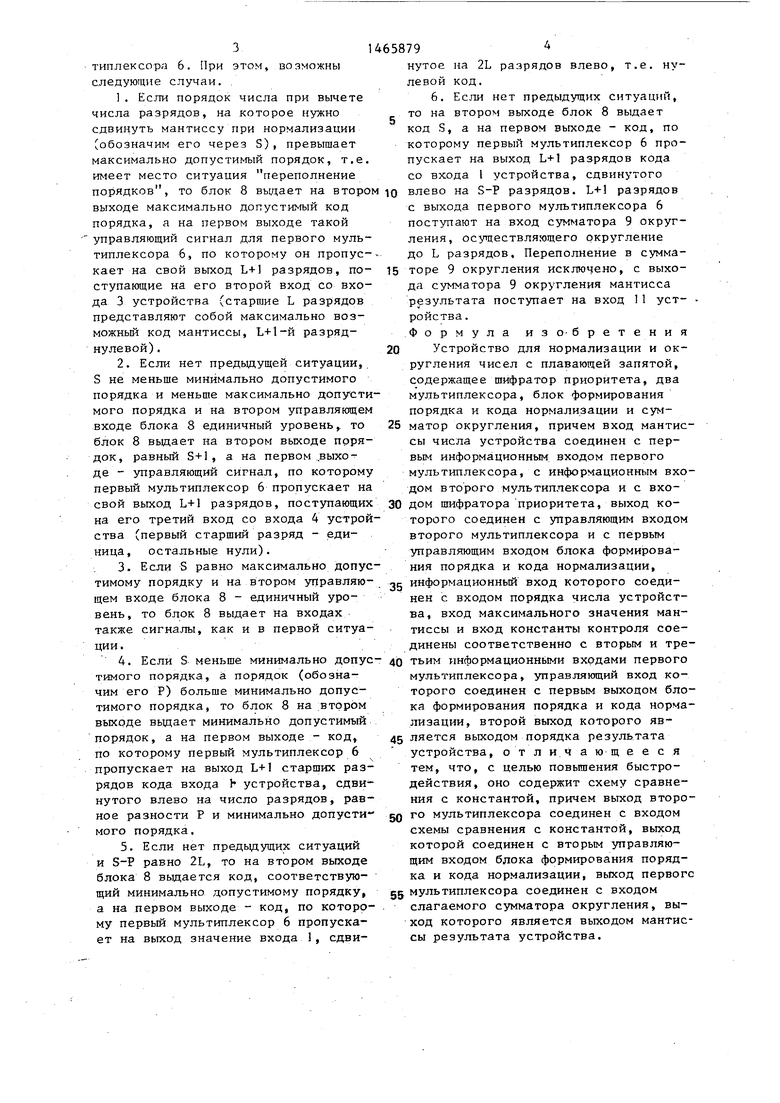

На фиг, 1 представлена схема устройства для нормализации и округления чисел с плавающей запятой; на фиг, 2 - схема первого мультиплексо ра.

Устройство , (фиг,1) содержит вход 1 мантиссы числа устройства, вход 2 порядка числа устройства, вход 3 максимального значения мантиссы устройства, вход 4 контакты устройства .шифратор 5 приоритета, первый и второй мультиплексоры 6 и 7, блок .8 фомирования порядка и кода нормализации, сумматор 9 округления, схему 1 сравнения с константой, выход П матиссы результата устройства, выход 12 из порядка результата устройства

Первый мультиплексор 6 (фиг, 2) содержит одноразрядные мультиплексоры 13. I -lS.L-t-l (L - разрядность мантиссы результата, каждый из- которых имеет 2L+3 информационных входа и управляющий 2L+4 вход). Управлянзщи входы одноразрядных мультиплексоров соединены между собой и представляют собой управляющий вход первого мультиплексора 6. Разрядность сигналов, поступающих по этому входу, равна наиме ньшему целому числу, котрое больше или равно log, (2L+3). Воспользуемся следующими обоз-начени ми: а/), .ал, ......а« - разряды входа

Чи ,-t устройства; с

t«

,с f - разряды

входа 3 устройства; d|,, ,,..,d, - разряды входа 4 устройства. На первы информационные входы мультиплексоров 13.L+1,...,13.1 поданы соответственно разряды а ,..,,a. На вторые информационные входы мультиплексоров 13.L+i,.. . , 13. 1 поданы соответственн разряды ,,. .. ,а . И так далее до 2L входа со сдвигом на один разряд, при условии, что если на i-вход мультиплексора 13L подан разряд а., , то (i+1),.,.,2L входы этого мультиплексора соединяются со входом нулевого уровня. 2L+l-e входы мультиплексоров 1.3 .L+1 , , .. , 13.1 соединены со

o

с

5

входом нулевого уровня, На 2L+2-e информационные входы мультиплексоров 13.L+1,... , 13.1 поданы соответственно разряды с , , . . ,с,. А на соответственно разряды d ..

. . D зависимости от управляю цих

сигналов, каждый из мультиплексоров 13.L+1-13.I, пропускает на выход по одному из разрядов, из того набора, что поступают на их входы. Разряды на их выходах bL. ,. . . ,Ь , сос- ставляют выходной сигнал первого мультиплексора 6.

Блок 8 реализован на постоянном запоминающем устройстве (ПЗУ), принцип кодировки которого следующий.

20

2530

35

40

45

5

Устройство (фиг.1) работает следующим образом.

2Ь-разрядная мантисса числа со входа I устройства поступает на первый ин|1)ормационный вход мультиплексора 6, на информационный вход мультиплексора 7 и на вход щифратора 5 приоритета. На выходе шифратора 5 п-риоритета получается код, равный числу нулевых разрядов, считая со старшего, разряда входного кода до первого ненулевого разряда. Этот код поступает.на первый управляющий вход блока 8 и на управляющий вход второго мультиплексора 7; Второй мультиплексор 7 сдвигает влево в соответствии с этим, управляющим сигналом код, поступающий на его информационный вход и пропускает на свой выход L+ старших разрядов сдвинутого кода. Выходной сигнал второго мультиплек-. сора 7 поступает на вход схемы 10 сравнения, выход которой является вторым управляющим входом блока 8. Если в старших L разрядах входного кода схемы 10 сравнения максимально возможные значения, а в младшем L+I-M разряде код больше половины максимально возможного (например, при двоичной системе счисления в L+1-м разряде код 1, или при шестнадцатиричной системе счисления в L+1-м разряде код от 8 до F), то на выходе схемы 10 сравнения единичный 5фовень, в противном случае - нуле- . Порядок числа со входа 2 устройства поступает на информационный вход блока 8, который формирует на своем втором выходе порядок результата, а на первом выходе - значение, пост5шающее на управляю ций вход муль3 этом.

типлексора 6. При этом, возможны следующие случаи. ,

второи вход со вхо- (старгаие L разрядов

ступающие на его да 3 устройства представляют собой максимально возможный код мантиссы, L+1-й разряд- нулевой) .

тимого порядка, а порядок (обозначим его Р) больше минимально допустимого порядка, то блок 8 на втором выходе вьщает минимально допустимый порядок, а на первом выходе - код, по которому первый мультиплексор 6 пропускает на выход L+1 старших разрядов кода входа h устройства, сдвинутого влево на число разрядов, раз- ное разности Р и минимально допустимого порядка.

нутое левой

ю влево на . 15

разрядов влево, т.е. ну

на 2L код.

S-P разрядов. L+1 разрядов с выхода первого мультиплексора 6 поступают на вход сумматора 9 округления, осуществляющего округление до L разрядов. Переполнение в сумматоре 9 округления исключено, с выхода сумматора 9 округления мантисса результата поступает на вход 11 уст- - ройства. Формула изо бретения

2Q Устройство для нормализации и округления чисел с плавающей запятой, содержащее шифратор приоритета, два мультиплексора, блок формирования порядка и кода нормализации и сум25 матор округления, причем вход мантиссы числа устройства соединен с первым информационным входом первого мультиплексора, с информационным входом второго мультиплексор а и с вхо30 дом шифратора приоритета, выход которого соединен с управляющим входом второго мультиплексора и с первым управляющим входом блока формирования порядка и кода нормализации,

25 информационный вход которого соединен с входом порядка числа устройства, вход максимального значения мантиссы и вход константы контроля соединены соответственно с вторым и тремультиплексора, управляющий вход которого соединен с первым выходом блока формирования порядка и кода нормализации, второй выход которого яв45 ляется выходом порядка результата устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит схему сравнения с константой, причем выход второ50 го мультиплексора соединен с входом схемы сравнения с константой, выход которой соединен с вторым управляющим входом блока формирования порядка и кода нормализации, выход первого

55 мультиплексора соединен с входом

слагаемого сумматора округления, выход которого является выходом мантиссы результата устройства.

| УСТРОЙСТВО ДЛЯ ПОДДЕРЖАНИЯ ПОСТОЯНСТВА ТОКА ПРИ РАЗГОНЕ И ТОРМОЖЕНИИ РЕВЕРСИВНОГО ДВИГАТЕЛЯ, ПИТАЕМОГО ОТ УПРАВЛЯЕМОГО РТУТНОГО ВЫПРЯМИТЕЛЯ | 1938 |

|

SU56181A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для суммирования нормализованных чисел с плавающей запятой | 1987 |

|

SU1418704A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-03-15—Публикация

1987-02-09—Подача