первой группы соединены с инверсным входом первого разряда группы разрядных информационных входов бпока управления нормализацией, инверсный вход (п1 + 1)-го разряда которой соединен с вторым входом первого элемента И т-ой группы (,2,. . . ,11-1) соответственно, выход первого элемента Ит-ой группы соединен с входом элемента НЕ Ю-ой группы и с первыми входами первого и второго элементов И В-ой груп пы (,. . . ,11-1) ссЮтветственно, выход элемента НЕ т-ой группы соединен с вторым входом второго элемента И m -ой группы соответственно, выход второго элемента И k -ой группы (Х 1,. .. ,Л-2) соединен- с k -ым входом шифратора и с k -ым выходом второй группы блока управления нормализацией выход второго элемента И (п-1)-ой группы соединен с первым входом элемента ИЛИ, выход которого соединен с (п-1)-ым входом шифратора и (л-1)-ым выходом второй группы блока управления нормализацией, нулевой выход которой соединен с прямым входом первого разряда группы разрядных информационных входов 6j70Ka управления нормализацией и с нулевым входом шифратора, выходы которого соединены с первой группой выходов блока управления нормализацией, выход- блока управления нормализацией соединен с выходом первого элемента И ()ой группы и с вторым входом элемента ИЛИ.2. Устройстйо ПОП.1, отличающееся тем, что блок вычитания содержит два сумматора, дешифратор, элемент НЕ, первую и вторую группы элементов И, каждая из которых состоит из П элементов И, третью и четвертую группы, элементов И, каждая из которых состоит из N элементов И, первьш и второй элементы И, группу элементов ИЛИ, выходной регистр порядка и выходной регистр мантиссы, информационные входы которого соединены с выходами первого сумматора, первые информационные входы которого соединены с выходами элементов И первой группы, а вторые входы - с выходами элементов И второй rpynimi, первые входы которых являются вторым входом блока вычитания, а вторые входы - с выходом первого элемента И, первый вход которого соединен с вы содом элемента НЕ и с первыми входами элементов И третьей группы, вторые входы

которых соединены с соответствующими первыми информационными входами второго сумматора, являющимися четвертым входом блока вычитания, вторые информационные входы второго сумматора являющиеся первым входом блока вычитания, соединены с первыми входами соответствующих элементов И четвертой группы, вторые входы которых соединены с выходом старшего разряда второго сумматора, входом элемента НЕ и первым входом второго элемента И, выход которого соединен с первыми входами элементов И первой группы,вторые входы которых являются третьим входом блока вычитания, второй, вход второго элемента И соединен с вторым входом первого элемента И. и выходом дешифратора, информационны входы которого соединены с вЬпсодами второго сумматора, выход выходного регистра порядка соединен с первым выходом блока вычитания, а информационные входы - с выходами элементов ИЛИ группы, первые и вторые входы которых соединены соответственно с выходами элементов И третьей и четвертой групп, выход И-го младшего разряда выходного регистра мантиссы соединен с третьим выходом блока вычитания, второй выход которого соединен с выходами (п-1) разрядов выходного регистра мантиссы, инве{)сные разрядные выходы и прямой выход первого разряда выходного регистра мантиссы соединены с четвертым выходом блока вычитания, управляющий вход которого соединен с третьими входами элементов И всех групп.

3. Устройство по П.1, отличающееся тем, что блок нормализации содержит входной регистр мантиссы, входной регистр порядка, сумматор, И групп элементов И, каждая из которых состоит из 11 элементов И, (п+1)-ую и (п+2)-ую группы элементов И, каж,цая из которых состоит из р элементов И, первую и вторую группы элементов ИЛИ, каждая из которых состоит из р и П элементов ИЛИ соответственно (Пир- разрядность регистров мантиссы и порядка соответственно) , выходной регистр мантиссы и выходной регистр порядка, выход которого соединен с вторым выходом блока нормализации, а информационные входы - с выходами элементов ИЛИ второй Группы, первые входы которых соединены с выходами элементов И (п+1)-ой группы, вторые входы - с выходами элементов И (li + 2)-oft группы, первые входы которых соединены с соответству ющими разрядными выходами сумматора, первые информационные входы которого соединены с первыми входами элементов И ( группы и с выходами входного регистра порядка, а вторые информационные входы - с четвертым входом нормализации, информационные входы входного регистра порядка соеди вены с первым входом блока нормализации, второй вход которого соединен с входами (n-l) разрядов входного регистра мантиссы, вход П -го младшего разряда которого соединен с третьим входом блока нормализации, прямой выход старшего разряда входного регистра мантиссы соединен с вторыми входа,ми элементов И (Г| + 1)-ой группы, а инверсный выход старшего разряда - с . вторыми -входами элементов И (п+2)-ой группы, первый выход блока нормализации соединен с выходом выходного регистра, мантиссы, информационные входы которого соединены с выходами элементов ИЛИ второй группы, I -е входы |-ых элементов ИЛИ которой соединены соответственно с выходами j-ых элемен тов И 1-ой группы, первые входы которых соединены с выходами J -го разряда входного регистра мантиссы, а вторые входы - с пятым входом, блока нормализации, первый управлякяций вход которого соединен с управляющими входами входного регистра мантиссы и входного регистра порядка, а второй управляющий вход блока нормализации соединен с третьими входами элементов И всех групп. 4. Устройство ПОП.1, отличающееся тем, что каждый блок умножения содержит матрицу из ПХ п элементов И и матрицу из пх п сумматоров, причем вход i -го разряда первого сомножителя блока умножения соединен с первыми входам (J,I)-HX элементов И матри11ы ( 1,. .. ,1 ,j 1, ...., п), а выход 1 -го разряда второго сомножителя блока умножения соединен с вторыми входами (i,j)-bix элементов И матрицы, выходы (i,j)-bix элементов И матрицы соединены с первыми входами (i,)-brx сумматоров матрицы соответственно, вторые входы (1,1)-ых и («,п)-ых сумматоров матрицы соединены с.шиной нулевого потенциала устройства, выходы (1,)-ых сумматоров матрицы кроме (1,1)-ых и (П,)-ых сумматоров матрицы соединены с вторыьш входами (i+I,J -1)-ых сумматоров матрицы, выходы (i,Т)-ых и (п, )-ых сумматоров матрицы соединены с выходами блока умножения. 5. Устройство по П.1, отличающееся тем, что блок синхронизации содержит четыре) -триггера, элемент И и элемент ИЛИ, первый вход которого соединен с управляющим входом Прием аргумента X устройства, с управляющими входами второго и третьего входных регистров и с входом первого Б -триггера блока синхронизации, выход которого соединен с управляющими входами первого и четвертого входных регистров и с входом второго) -триггера блока синхронизации, выход которого соединен с управляющим входом блока вычитания и входом третьего 3} -триггера блока синхронизации, выход которого соединен с первым управляющим входом блока нормализации и входом четвертого D-триггера блока синхронизации, выход которого соединен с первым входом элемента И блока синхронизации, второй вход которого соединен с входом Конец счета устройства , а выход - с вторым входом элемента ИЛИ блока синхронизации , выход которого соединен с вторым управляющим входом блока нормализации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для вычисления тригонометрических функций с плавающей запятой | 1986 |

|

SU1425661A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Преобразователь форматов данных | 1982 |

|

SU1092490A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

1. ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ОБРАТНОЙ ВЕЛИЧИНЫ, содержащее два входных регистра, сумматор и блок синхронизации, отличающееся тем, что, с целью повышения быстродействия, в него введены два входных регистра, два сумматора, два блока умножения, блок вычитания, блок управления нормализацией, элемент ИЛИ и блок нормализации, причем вход мантиссы аргумента X устройства соединен с информационным входом парного входного регистра и первым информационным входом второго входного регистра, второй информационный вход которого соединен с первым выходом блока нормализации, второй выход которого соединен с первым информационным входом третьего входного регистра, второй информационный вход которого соединен с выходом первого сумматора, первьй вход которого соединен с входом константы 2 устройства, а второй вход - с входом порядка аргумента X устройства и .информационньм входом четвертого входного регистра, выход которого соединен с первым входом второго сумматора, второй вход которого соединен с первым выходом третьего входного регистра, второй выход которого соединен с первым входом третьего сумматора, второй вход которого соединен с входом константы 2 устройства, а вьгходс первым входом блока вычитания,второй вход которого соединен с выходом первого блока умнолтения, вход первого сомножителя которого соединен с выходом первого входного регистра, а;вход второго сомножителя - с выходом второго блока умножения, входы первого и второго сомножителей которого соединены с выходом второго входного i регистра и с третьим входом блока вычитания, четвертый вход которого (Л соединен с выходом второго сумматор.а, nepBbtfi выход блока вычитания соеди- нен с первым входом блока нормализа- цииJ второй вход которого соединен с вторым выходом блока вычитания, третий выход которого соединен с первым входом элемента ИЛИ, выход кото- рого соединен с третьим входом блока нормализации, а.второй вход - с выходом блока управления нормализацией, sj первая группа выходов которого соеди00 нена с четвертым входом блока нормасо лизации, пятый вход которого соединен с второй группой выходов блока управления нормализацией, группа разрядных информационных входов которого соединена с четвертым выходом блока вычитания, а блок управления нормализацией содержит элемент ИЛИ, шифратор и (п-1) групп ячеек нормализации каждая из которых состоит из двух элементов И и элемента НЕ, причем в блоке упр вления нормализацией первые входы первого и второго элементов И

1

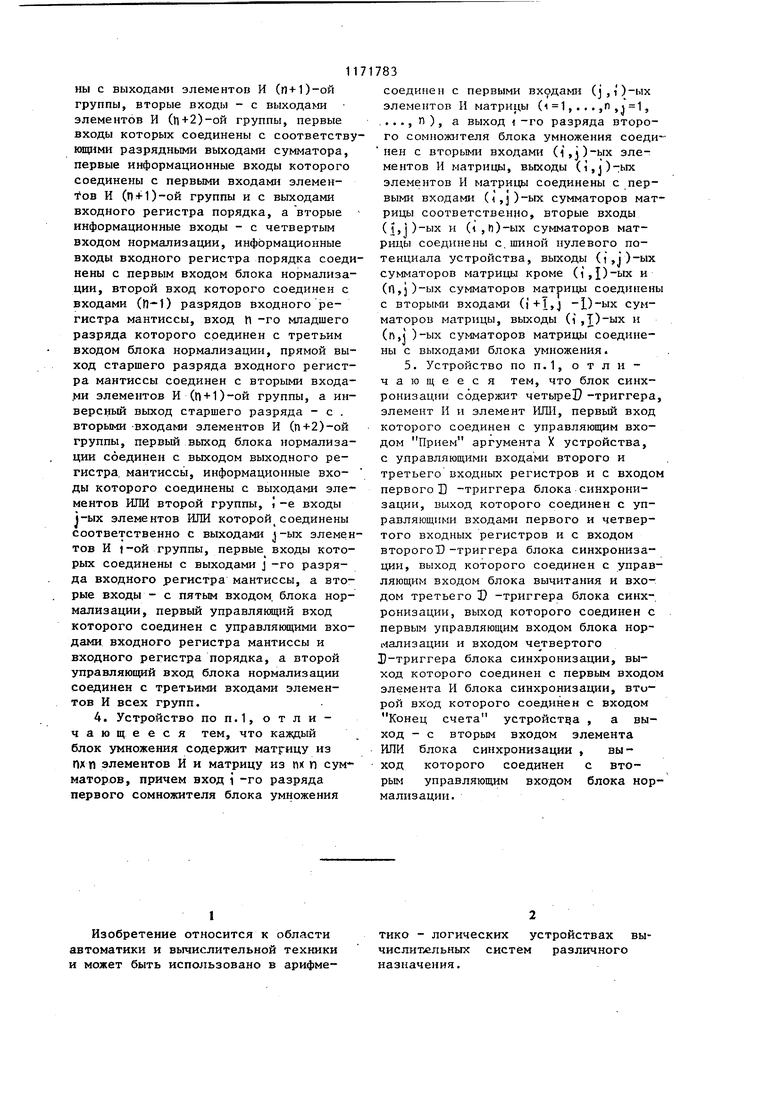

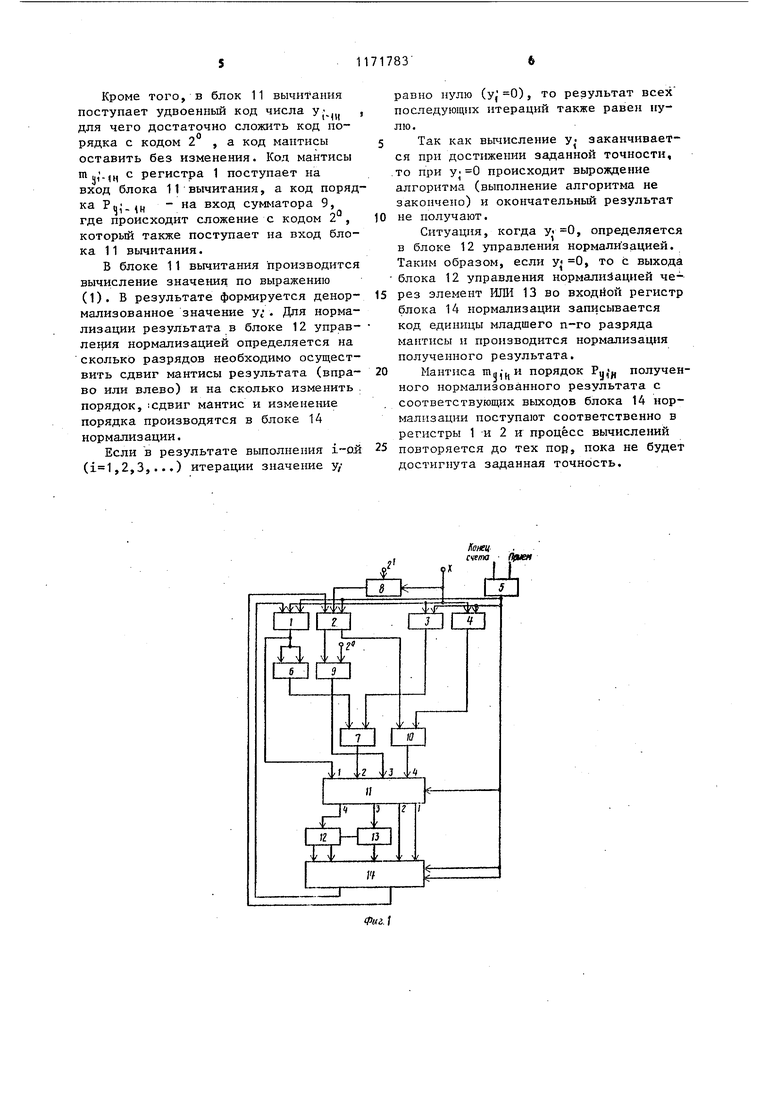

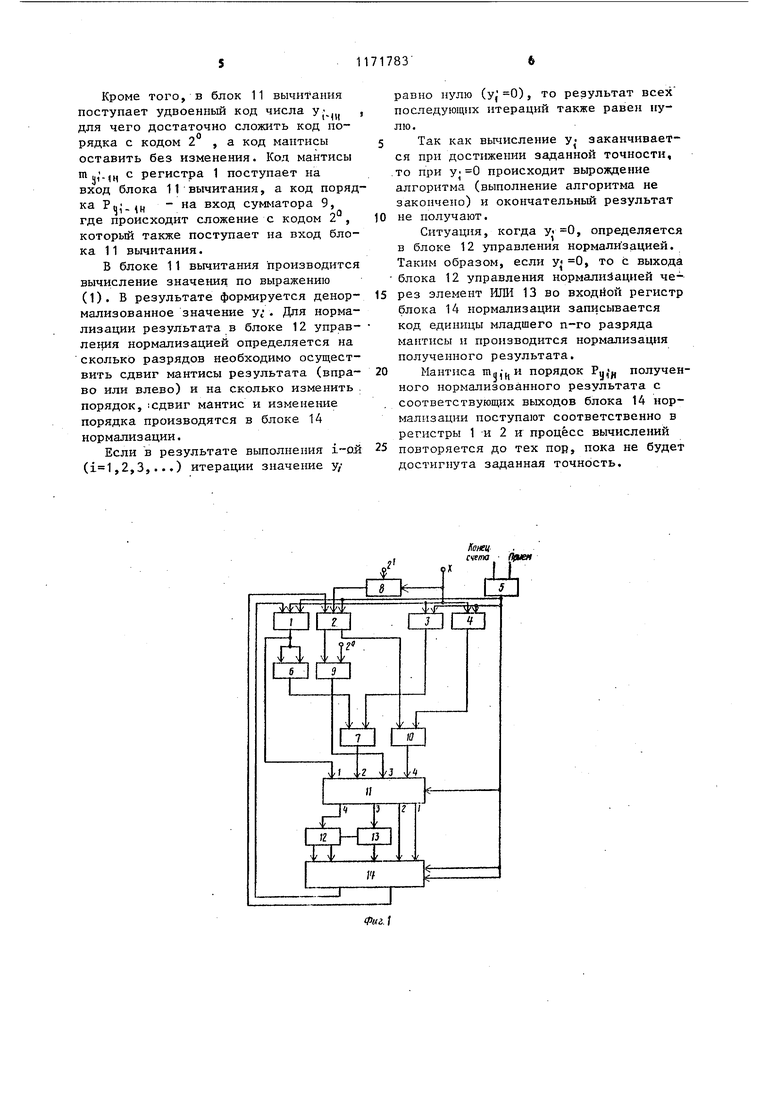

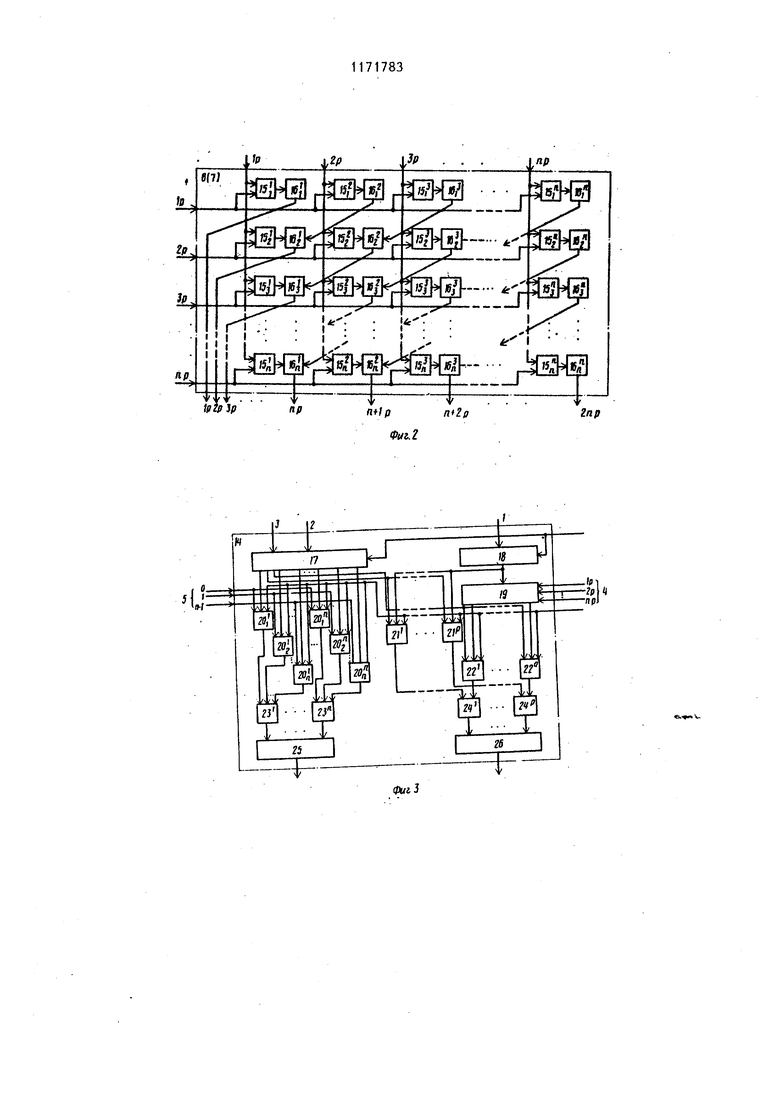

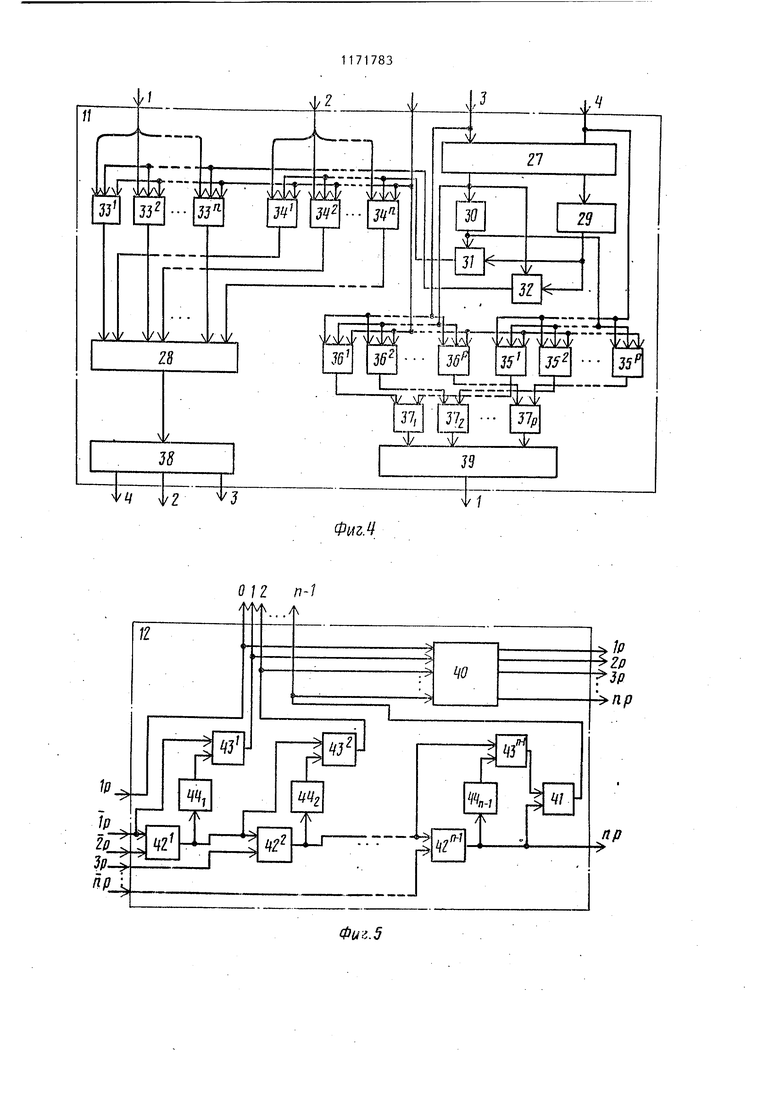

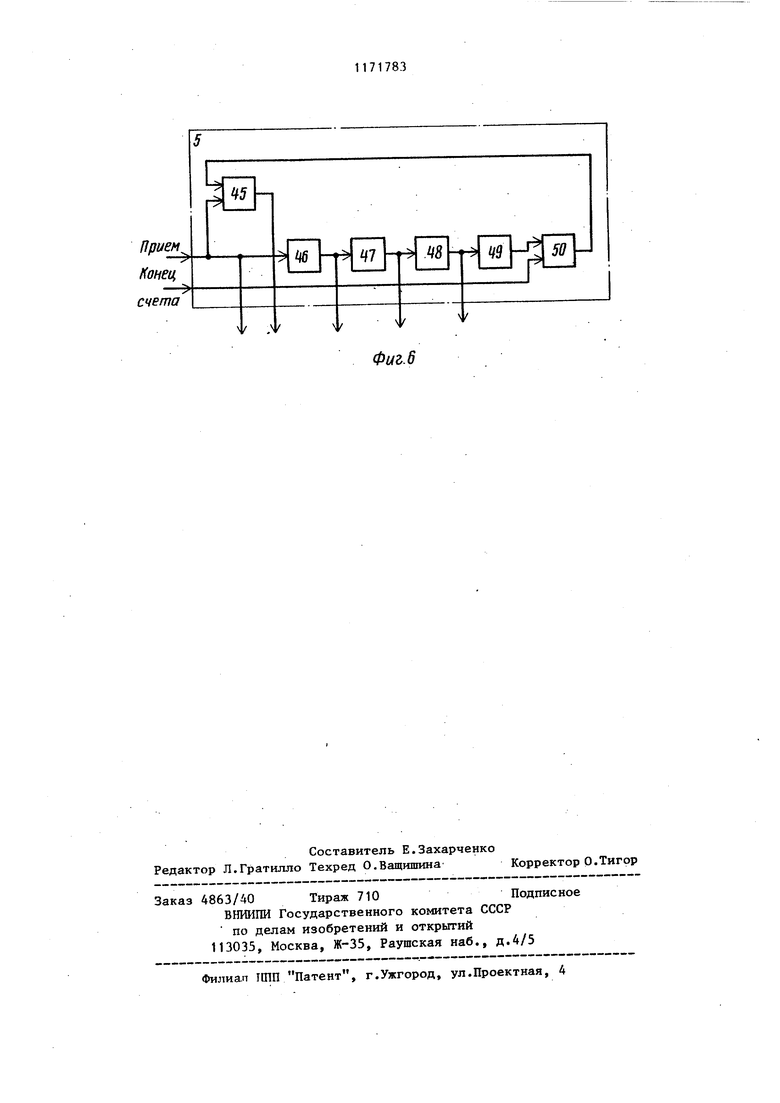

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в арифметико - логических устройствах вычислительных систем различного назначения. 3 Целью изобретения является повышение быстродействия устройства. На фиг,1 изображена структурная схема цифрового устройства для вычис ления обратной величины; на фиг.2 схема блока умножения} на фиг.З то же, нормализации, на фиг.4 - то же, вычитания; на фиг.З - то же, управления нормализациейJ на фиг.6 то же, синхронизации управления. Устройство (фиг.1) содержит входные регистры 1-4, блок 5 синхронизации, блоки 6 и 7 умножения, сумматоры 8-10, блок 11 вычитания, блок 12 управления нормализацией, элемент ИЛИ 13, блок 14 нормализации. Блоки 6 и 7 (фиг.2) содержат матрицу из пхп элементов И 15 и матрицу из пхп сумматоров 16. Блок 14 нормализации (фиг.З) содержит входные регистры мантиссы 17 и порядка 18, сум матор 19, П групп элементов И 20 и две группы элементов И 21 и 22, первую 23 и вторую 24 труппы элементов ИЛИ, выходные регистры мантисы 25 и порядка 26. Блок 11 вычитания (фиг.4) содеряда два сумматора 27 и 28, дешифратор 29 элемент НЕ 30, два элемента И 31 и 32, первую 33, вторую 34, третью 35, четвертую 36 группы элементов- И, группу элеме.нтов ИЛИ 37, выходные регистры мантисы 38 и порядка 39. Блок 12 управления нормализацией (фиг.5) содержит шифратор 40, элемент ИЛИ 41, (п-1) ячеек нормализаци из двух элементов И 42 и 43 и элемента НЕ 44. Блок 5 синхронизации (фиг.6) соде жит элемент ИЛИ 45, четыре В-триггер 46-49 и элемент И 50. Алгоритм работы основан на методе Ньютона, который состоит в вычислении обратной величины по итерацион ной формуле ., (2-у-.,-х),(1) где X - аргумент; у - обратная величинаi ,2... - номер итерации. При ,у - начальное приближени к обратной величине. Устройство работает следующим . Перед началом работы все регист ы находятся в нулевом состоянии. В 834 момент приема нормализованного аргумента X во входные регистры 3 и 4, в регистры 1 и 2 записываются мантиса и порядок начального приближения у к обратной величине у аргумента X . Мантиса начального приближения определяется по старшеьту первому разряду мантисы нормализованного аргумента 2 мантиса нормализованного аргумента х; РУК - порядок нормализованного аргумента х, и равна 10.00...0. 1.уон ,п 0.10..о В результате нормализации тц- получа 0.10...О, 10 Порядок начального приближения P(joH с учетом PL равен ) + IO и формируется в сумматоре 8. I Вычисление обратной величины осуществляется по вьфажению (1). Для вычисления квадрата нормализованного числа у .,к И. ч;-н-2),„ 2 (2) (в первой итерации у,-,,|,Уо(( ) необходимо вычислить квадрат мантисы ™4i-1H увеличить порядок в два раза. Вычисление квадрата мантисы производится в блоке 6 умножения, на первый и второй вход которого поступает нормализованная мантиса с регистра 1. Умножение порядка нормализованного числа Р( на два соответствует передаче со сдвигом его на один разряд влево. Следовательно, порядок PUJ.IH с регистра 2 на сумматор 10 выдается со сдвигом влево на один разряд. В блоке 7 умножения и сумматоре ТО производится перемножение квадрата нормализованного числа , и нор- мализованного аргумента х , т.е. У , X. н Умножение мантис осуществляется в блоке 7 умножения, а сложение порядков - в сумматоре 10. Мантиса и порядок числа поступают в блок 11 вычитания.

Кроме того, в блок 11 вычитания поступает удвоенный код числа У... для чего достаточно сложить код порядка с кодом 2° , а код маптисы оставить без изменения. Код мантисы 11 111-(Ч регистра 1 поступает на вход блока 11 вычитания, а код порядка Рц,. - на вход сумматора 9, где происходит сложение с кодом 2°, который также поступает на вход блока 11 вычитания.

В блоке 11 вычитания производится вычисление значения по выражению (1). В результате формируется денормализованное значение у;. Для нормализации результата в блоке 12 управлeIpiя нормализацией определяется на сколько разрядов необходимо осуществить сдвиг мантисы результата (вправо или влево) и на сколько изменить порядок, :сдвиг мЗнтис И измвнение порядка производятся в блоке 14 нор мализ ации.

Если в результате выполнения (,2,3,...) итерации значение у/

равно нулю (у, 0), то результат всех последующих итераций также равен пулю.

Так как вычисление у. заканчивается при достижении заданной точности, то при происходит вырождение алгоритма (выполнение алгоритма не закончено) и окончательный результат не получают.

Ситуация, когда у- 0, определяется в блоке 12 управления нормализацией. Таким образом, если у 0, то с выхода - блока 12 управления нормализацией через элемент HUli 13 во входйой регистр блока 14 нормализации записывается код единицы младшего п-го разряда мантисы и производится нормализация полученного результата.

0 Мантиса 1П|,, порядок Ру,;, полученного нормализованного результата с соответствующих выходов блока 14 нормализации поступают соответственно в регистры 1 и 2 и процесс вычислений

повторяется до тех пор, пока не будет достигнута заданная точность.

Конец

счета (faen

ttipjp

ЗР ...

on п-1

Фиг. 5

Фиг. 6

| Устройство псевдоделения | 1978 |

|

SU752337A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| СОЮЗНАЯ Iмшшда^'"""ЙИБЛИОТЕК^ | 0 |

|

SU331386A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1985-08-07—Публикация

1983-12-15—Подача