Изобретение относится к области автоматики и вычислительной техники и может быть использовано в распределенных отказоустойчивых управляющих системах АСУ ТП, использующих программный принцип управления и допускающих наращивание при расширении числа вы- Ьолняемых функций.

Цель изобретения - повышение быстродействия модуля за счет сокращения .

времени выполнения программы при отказе одного из управляющих модулей - и замене его на резервный.

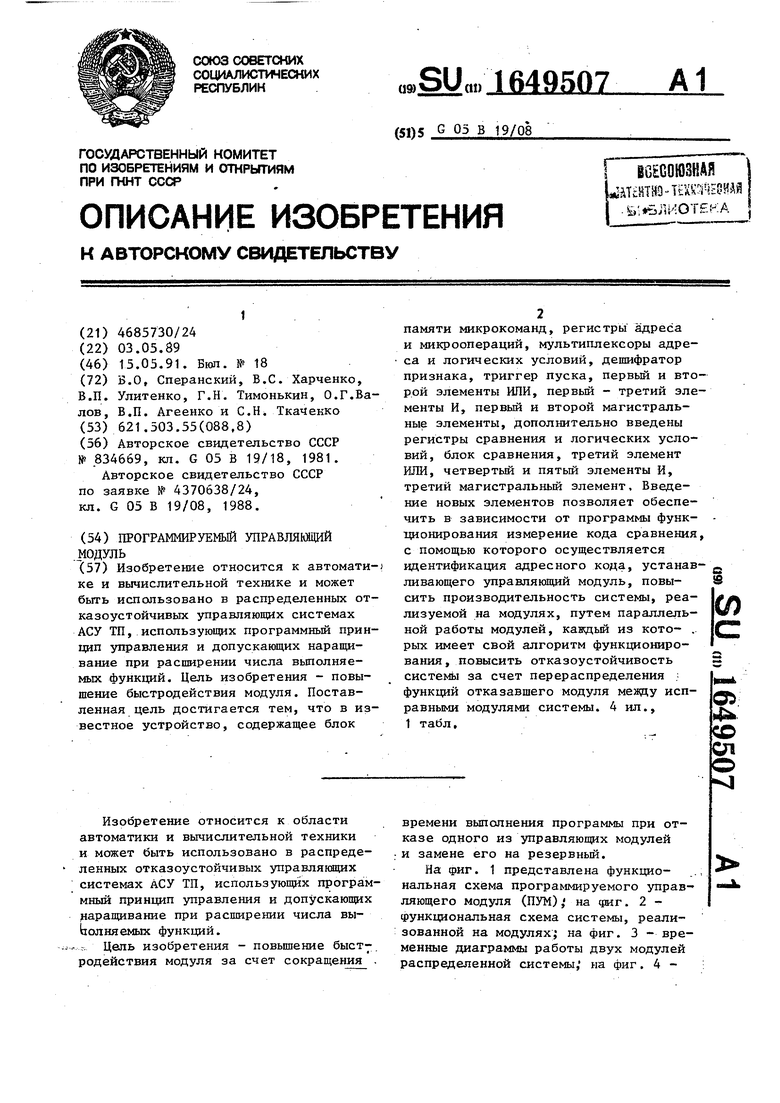

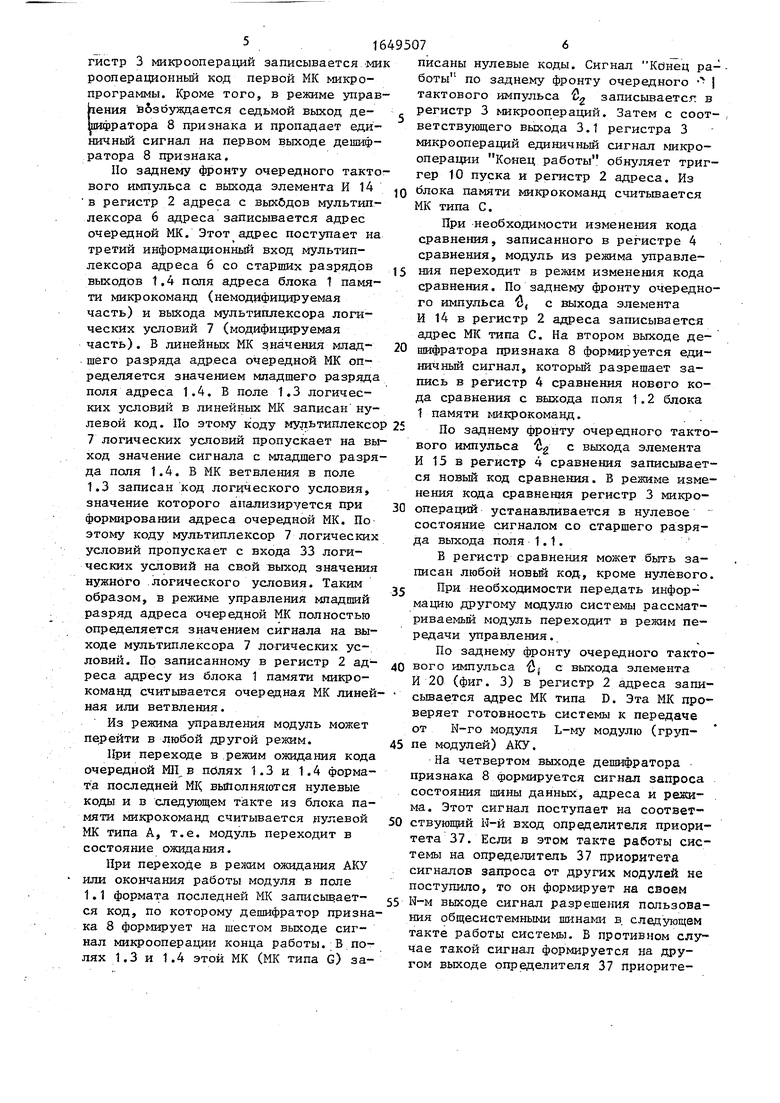

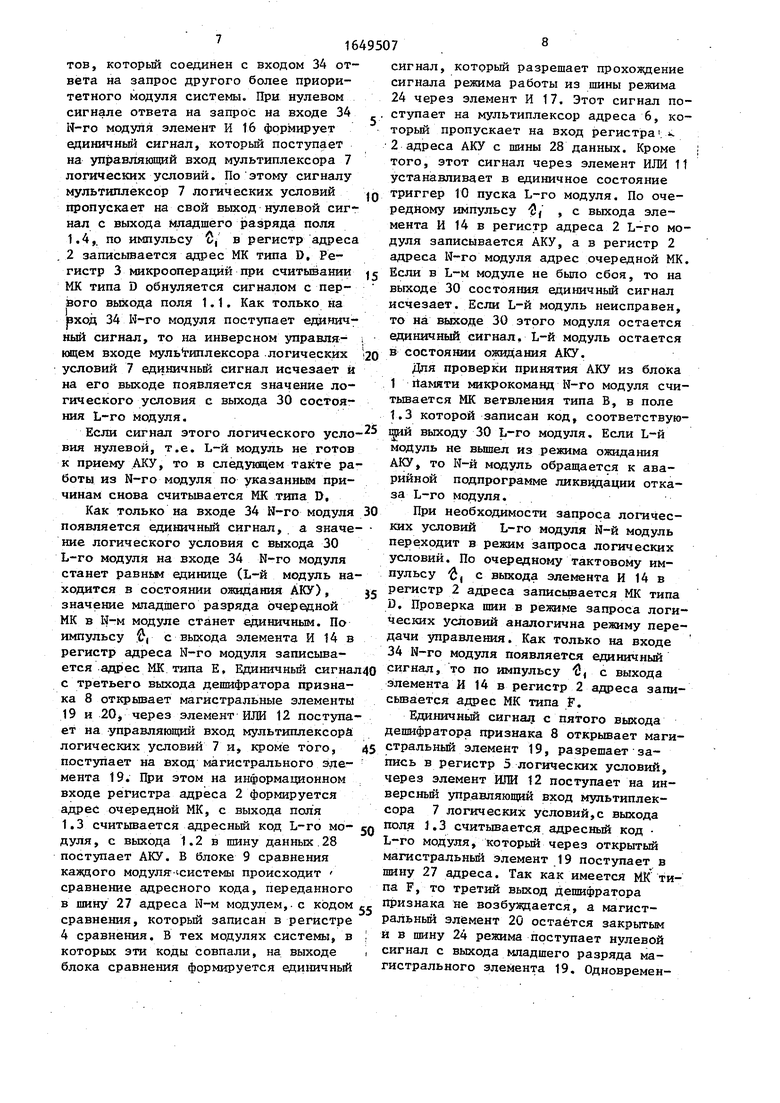

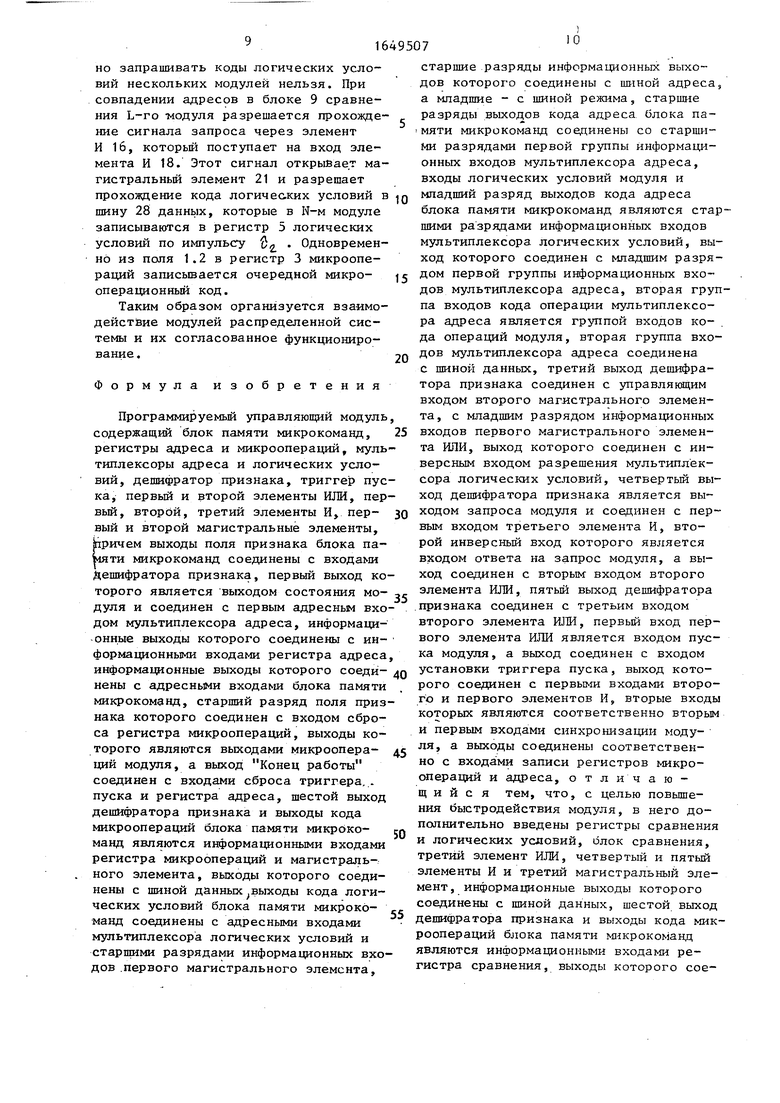

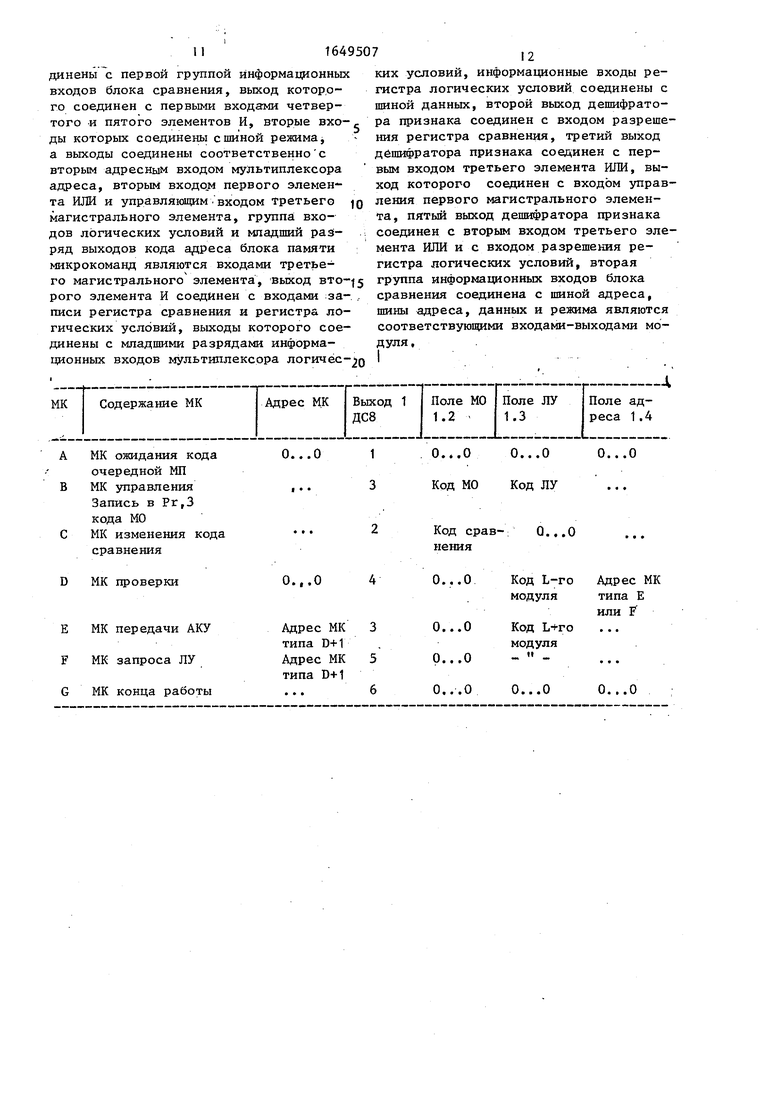

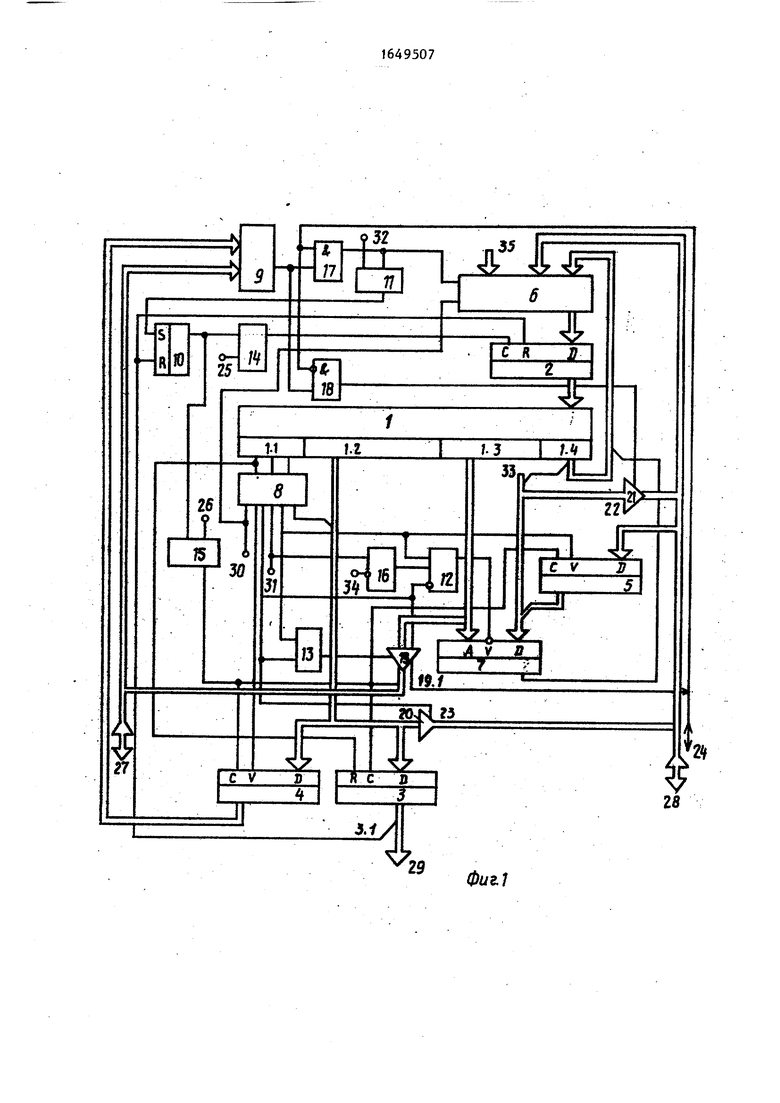

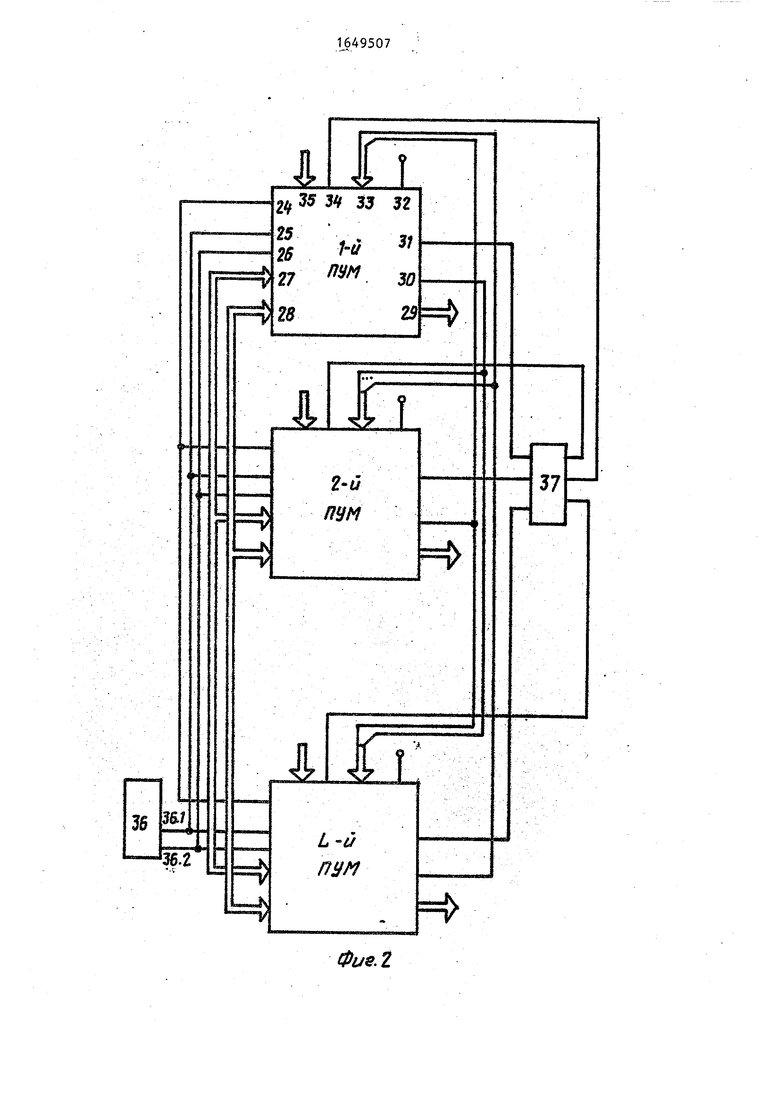

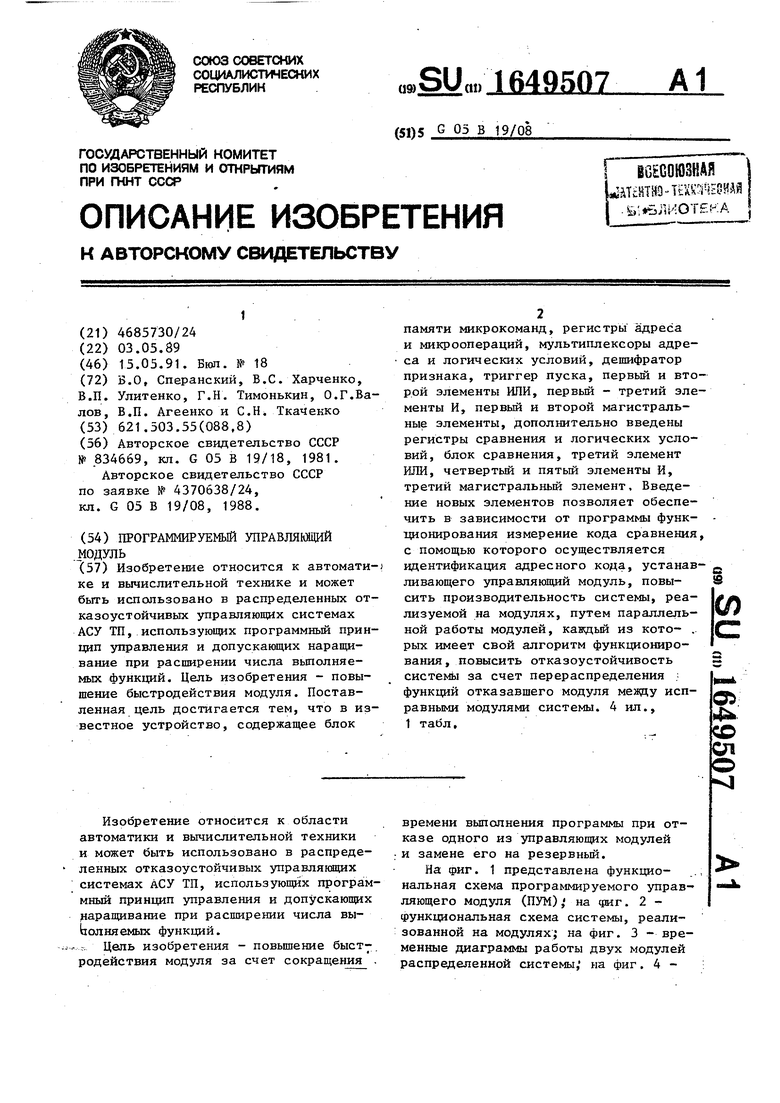

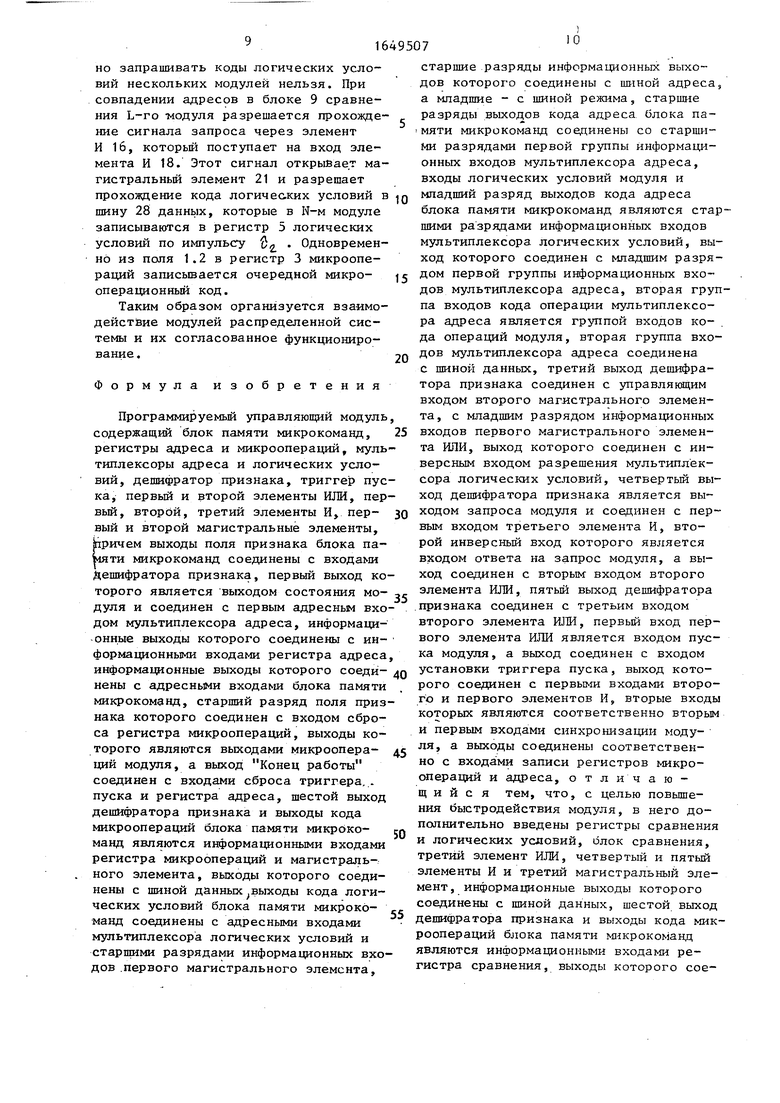

На фиг. 1 представлена функциональная схема программируемого управляющего модуля (ПУМ), на сриг. 2 - Функциональная схема системы, реализованной на модулях; на фиг. 3 - временные диаграммы работы двух модулей распределенной системы; на фиг. 4 блок-схема алгоритма функционирования модуля.

Модуль содержит блок 1 памяти микрокоманд с полями признака 1.1, кода микроопераций (МО) 1.2, кода логических условий (ЛУ) 1.3 и адреса 1.4, регистры адреса 2, микроопераций 3, сравнения 4 и логических условий 5, мультиплексоры адреса 6 и логических условий 7, дешифратор 8 признака, блок 9 сравнения, триггер 10 пуска, первый 11, второй 12 и третий 13 элементы ИЛИ, первый 14, второй 15, третий 16, четвертый 17 и пятый 18 эле- менты И, а также первый 19, второй 20 и третий 21 магистральные элементы и имеет информационный вход 22 магистрального элемента 21, выход 23 маги1

стрального элемента 20, вход-выход 24 2Q пуска хотя бы одного модуля системы.

шины режима, первый 25 и второй 26 входы синхронизации, вход-выход 27 шины адреса, вход-выход шины данных 28, выходы микроопераций 29, выход 30 состояния, выход 31 запроса, вход 32 пус-25 ка, вход 33 логических условий, вход 34 ответа на запрос и вход 35 кода операций.

Систему образуют генератор 36 тактовых импульсов и определитель 37 при-эд оритета.

Программируемый управляющий модуль в рамках распределенной системы работает следующим образом.

В исходном состоянии генератор 36 , тактовых импульсов вырабатывает на с своих выходах последовательности сдвинутых относительно друг друга тактовых импульсов, все модули находятся в исходном состоянии ожидания. Все 0 элементы памяти, кроме регистра 4 сравнения, установлены в нулевое состояние. Регистр 4 сравнения установлен в единичное состояние, т.е. в нем

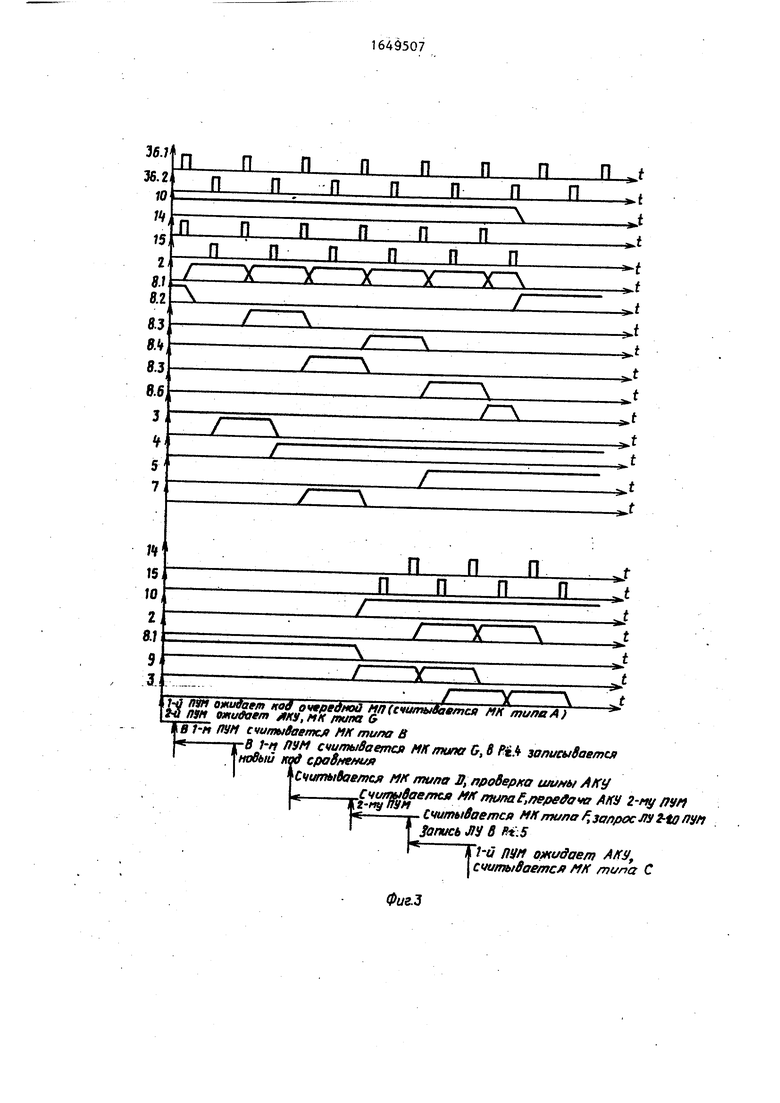

Каждый модуль может работать в сле дующих режимах: режим ожидания кода очередной МП} режим управления; режим изменения кода сравнения; режим передачи управления; режим запроса логических условий; режим ожидания АКУ.

Исходное состояние модуля равнозначно состоянию модуля в режиме ожидания АКУ.

Переход модуля в режцм ожидания ко да МП из исходного состояния осуществляется по сигналу Пуск, поступающе му с входа 32 через элемент ИЛИ 11 на установочный вход триггера 10 пуска. Сигнал с выхода триггера Ю пуска открывает элементы И 14 и 15, разрешая прохождение тактовых импульсов с выхо дов генератора 36 тактовых импульсов по соответствующим входам модуля.

Если к моменту появления на синхро входе регистра адреса 2 модуля задне го фронта первого тактового импульса (fc|) с выхода элемента И 14 на выходе 35 кода операций еще не появилось, то

записан единичный код. Из блока 1 па-;д5 в регистре 2 адреса меняется нулевой

$

реса, который пропускает на информационные входы регистра 2 адреса код операции с входа 35 модуля. Единичный код с выхода регистра сравнения 4 поступает на соответствующие информационные входы блока 9 сравнения, на другие входы которого с шины 27 адреса посту- пает нулевой код.Таким образом, блок 9 сравнения формирует на выходе нулевой сигнал, который запрещает прохождение через элементы И 12 и 17 сигналов режима работы шины 24 режима, Установка регистра 4 сравнения в единичное состояние приводит к тому, что модуль воспринимает нулевой код в шине 27 адреса как чужой. В таком состоянии управляющая система находится до поступления сигнала Пуск на вход 32

Каждый модуль может работать в следующих режимах: режим ожидания кода очередной МП} режим управления; режим изменения кода сравнения; режим передачи управления; режим запроса логических условий; режим ожидания АКУ.

Исходное состояние модуля равнозначно состоянию модуля в режиме ожидания АКУ.

Переход модуля в режцм ожидания кода МП из исходного состояния осуществляется по сигналу Пуск, поступающему с входа 32 через элемент ИЛИ 11 на установочный вход триггера 10 пуска. Сигнал с выхода триггера Ю пуска открывает элементы И 14 и 15, разрешая прохождение тактовых импульсов с выходов генератора 36 тактовых импульсов по соответствующим входам модуля.

Если к моменту появления на синхро- входе регистра адреса 2 модуля заднего фронта первого тактового импульса (fc|) с выхода элемента И 14 на выходе 35 кода операций еще не появилось, то

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649506A1 |

| Устройство для программного управления и контроля | 1991 |

|

SU1784943A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Программный управляющий модуль с контролем | 1990 |

|

SU1758634A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1476465A1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

Изобретение относится к автомати-) ке и вычислительной технике и может быть использовано в распределенных отказоустойчивых управляющих системах АСУ ТП, использующих программный принцип управления и допускающих наращивание при расширении числа выполняемых функций. Цель изобретения - повышение быстродействия модуля. Поставленная цель достигается тем, что в известное устройство, содержащее блок памяти микрокоманд, регистры адреса и микроопераций, мультиплексоры адреса и логических условий, дешифратор признака, триггер пуска, первый и второй элементы ИЛИ, первый - третий элементы И, первый и второй магистральные элементы, дополнительно введены регистры сравнения и логических условий, блок сравнения, третий элемент ИЛИ, четвертый и пятый элементы И, третий магистральный элемент, Введение новых элементов позволяет обеспечить в зависимости от программы функционирования измерение кода сравнения, с помощью которого осуществляется идентификация адресного кода, устанавливающего управляющий модуль, повысить производительность системы, реализуемой на модулях, путем параллельной работы модулей, каждый из кото- . рых имеет свой алгоритм функционирования , повысить отказоустойчивость системы за счет перераспределения функций отказавшего модуля между исправными модулями системы. 4 ил., 1 табл, 0& -U со ел

мяти микрокоманд считывается содержимое ячейки по нулевому адресу.

В таблице это микрокоманда (МК) типа А. В ее поле 1.1 записан нулевой код, который декодируется дешиф- ратором признака 8 как сигнал ожидания кода очередной МП. Этот единичный сигнал поступает на выход 30 состояjHHH МОДУЛЯ.

Кроме того, сигнал ожидания кода очередной МП с первого выхода дешифратора признака 8 поступает на второй управляющий вход мультиплексора 6 ададрес и из блока 1 памяти микрокоманд снова считывается МК типа А. Так как в ее поле 1.2 записан нулевой код, то по заднему фронту тактового импульса с выхода второго элемента И 15.регистр 3 микроопераций своего состояния не изменяет.

После появления кода МП на входе 35 модуля этот код через мультиплексор адреса 6 записывается в регистр 2 адреса и модуль переходит в режим управления .

Но заднему фронту тактового импульса г с выхода элемента И 15 в ре516495076

гистр 3 микроопераций записывается мик писаны нулевые коды. Сигнал КФнец ра- рооперационный код первой МК микро- боты по заднему фронту очередного Л | программы. Кроме того, в режиме управ- тактового импульса 52 записывается в

регистр 3 микроопераций. Затем с соответствующего выхода 3.1 регистра 3 микроопераций единичный сигнал микрооперации Конец работы обнуляет триггер 10 пуска и регистр 2 адреса. Из JQ блока памяти микрокоманд считывается МК типа С.

При необходимости изменения кода сравнения, записанного в регистре 4 сравнения, модуль из режима управле- 15 ния переходит в режим изменения кода сравнения. По заднему фронту очередного импульса Ј, с выхода элемента И 14 в регистр 2 адреса записывается адрес МК типа С. На втором выходе де- 20 шифратора признака 8 формируется единичный сигнал, который разрешает запись в регистр 4 сравнения нового кода сравнения с выхода поля 1.2 блока 1 памяти микрокоманд.

По заднему фронту очередного тактового импульса Јg с выхода элемента И 15 в регистр 4 сравнения записывается новый код сравнения. В режиме изменения кода сравнения регистр 3 микро- 30 операций устанавливается в нулевое состояние сигналом со старшего разряда выхода поля 1.1.

В регистр сравнения может быть записан любой новьй код, кроме нулевого.

При необходимости передать информацию другому модулю системы рассматриваемый модуль переходит в режим передачи управления.

По заднему фронту очередного тактоЬения вбзбуидается седьмой выход дешифратора 8 признака и пропадает единичный сигнал на первом выходе дешифратора 8 признака.

По заднему фронту очередного тактового импульса с выхода элемента И 14 в регистр 2 адреса с выходов мультиплексора 6 адреса записывается адрес очередной МК. Этот адрес поступает на третий информационный вход мультиплексора адреса 6 со старших разрядов выходов 1.4 поля адреса блока t памяти микрокоманд (немодифицируемая часть) и выхода мультиплексора логических условий 7 (модифицируемая часть). В линейных МК значения младшего разряда адреса очередной МК определяется значением младшего разряда поля адреса 1.4. В поле 1.3 логических условий в линейных МК записан нулевой код. По этому коду мультиплексор 25 7 логических условий пропускает на выход значение сигнала с младшего разряда поля 1.4. В МК ветвления в поле 1.3 записан код логического условия, значение которого анализируется при формировании адреса очередной МК. По этому коду мультиплексор 7 логических условий пропускает с входа 33 логических условий на свой выход значения нужного логического условия. Таким образом, в режиме управления младший разряд адреса очередной МК полностью определяется значением сигнала на выходе мультиплексора 7 логических ус35

ловий. По записанному в регистр 2 ад- 4д Вого импульса Ј; с выхода элемента реса адресу из блока 1 памяти микро- и 20 (фиг. 3) в регистр 2 адреса записывается адрес МК типа D. Эта МК прокоманд считывается очередная МК линейная или ветвления.

Из режима управления модуль может перейти в любой другой режим.

При переходе в режим ожидания кода очередной МП в пблях 1.3 и 1.4 формата последней МК, выполняются нулевые коды и в следующем такте из блока памяти микрокоманд считывается нулевой МК типа А, т.е. модуль переходит в состояние ожидания.

При переходе в режим ожидания АКУ или окончания работы модуля в поле 1.1 формата последней МК записывается код, по которому дешифратор признака 8 формирует на шестом выходе сигнал микрооперации конца работы. В полях 1.3 и 1.4 этой МК (МК типа G) заверяет готовность системы к передаче от N-го модуля L-му модулю (груп45 пе модулей) АКУ.

На четвертом выходе дешифратора признака 8 формируется сигнал запроса состояния шины данных, адреса и режима. Этот сигнал поступает на соответ

50 ствующий Ы-и вход определителя приоритета 37. Если в этом такте работы системы на определитель 37 приоритета сигналов запроса от других модулей не поступило, то он формирует на своем

55 Н-м выходе сигнал разрешения пользования общесистемными шинами в следующем такте работы системы. В противном случае такой сигнал формируется на другом выходе определителя 37 приорите25

35

веряет готовность системы к передаче от N-го модуля L-му модулю (группе модулей) АКУ.

На четвертом выходе дешифратора признака 8 формируется сигнал запроса состояния шины данных, адреса и режима. Этот сигнал поступает на соответ

ствующий Ы-и вход определителя приоритета 37. Если в этом такте работы системы на определитель 37 приоритета сигналов запроса от других модулей не поступило, то он формирует на своем

Н-м выходе сигнал разрешения пользования общесистемными шинами в следующем такте работы системы. В противном случае такой сигнал формируется на другом выходе определителя 37 приорите716

тов, который соединен с входом 34 ответа на запрос другого более приоритетного модуля системы. При нулевом сигнале ответа на запрос на входе 34 Ы-го модуля элемент И 16 формирует единичный сигнал, который поступает на управляющий вход мультиплексора 7 логических условий. По этому сигналу мультиплексор 7 логических условий пропускает на свой выход нулевой сигнал с выхода младшего разряда поля 1,4, по импульсу Ј, в регистр адреса 2 записывается адрес МК типа D, Регистр 3 микроопераций при считывании МК типа D обнуляется сигналом с первого выхода поля 1.1. Как только на рход 34 И-го модуля поступает единнч

ный сигнал, то на инверсном управляющем входе мультиплексора логических условий 7 единичный сигнал исчезает и на его выходе появляется значение логического условия с выхода 30 состояния L-ro модуля.

Если сигнал этого логического уело вия нулевой, т.е. L-й модуль не готов к приему АКУ, то в следующем такте работы из N-ro модуля по указанным причинам снова считывается МК типа D.

Как только на входе 34 Ы-го модуля появляется единичный сигнал, а значе ние логического условия с выхода 30 L-ro модуля на входе 34 N-ro модуля станет равным единице (L-й модуль на

ходится в состоянии ожидания АКУ), значение младшего разряда очередной МК в Ы-м модуле станет единичным. По импульсу Ј, с выхода элемента И 14 в регистр адреса Ы-го модуля записывается адрес МК типа Е, Единичный сигна с третьего выхода дешифратора признака 8 открывает магистральные элементы 19 и 20, через элемент ИЛИ 12 поступает на управляющий вход мультиплексора логических условии 7 и, кроме того, поступает на вход магистрального элемента 19. При этом на информационном входе регистра адреса 2 формируется адрес очередной МК, с выхода поля 1.3 считывается адресный код L-ro модуля, с выхода 1.2 в шину данных 28 поступает АКУ. В блоке 9 сравнения каждого модуля системы происходит сравнение адресного кода, переданного в шину 27 адреса Ы-м модулем, с кодом сравнения, который записан в регистре 4 сравнения. В тех модулях системы, в которых эти коды совпали, на выходе блока сравнения формируется единичный

8

10

15

20

3035

45

40 сигнал, который разрешает прохождение сигнала режима работы из шины режима 24 через элемент И 17. Этот сигнал поступает на мультиплексор адреса 6, который пропускает на вход регистра 2 адреса АКУ с шины 28 данных. Кроме того, этот сигнал через элемент ИЛИ 11 устанавливает в единичное состояние триггер 10 пуска L-ro модуля. По очередному импульсу Ј( , с выхода элемента И 14 в регистр адреса 2 L-ro модуля записывается АКУ, а в регистр 2 адреса W-ro модуля адрес очередной МК. Если в L-м модуле не было сбоя, то на выходе 30 состояния единичный сигнал исчезает. Если L-й модуль неисправен, то на выходе 30 этого модуля остается единичный сигнал. L-й модуль остается в состоянии ожидания АКУ.

Для проверки принятия АКУ из блока 1 памяти микрокоманд Ы-го модуля считывается МК ветвления типа В, в поле 1.3 которой записан код, соответствую- 25 пий выходу 30 L-ro модуля. Если L-й модуль не вышел из режима ожидания АКУ, то Ы-й модуль обращается к аварийной подпрограмме ликвидации отказа L-ro модуля.

При необходимости запроса логических условий L-ro модуля Ы-й модуль переходит в режим запроса логических условий. По очередному тактовому импульсу Ј, с выхода элемента И 14 в регистр 2 адреса записывается МК типа D. Проверка шин в режиме запроса логических условий аналогична режиму передачи управления. Как только на входе 34 Ы-го модуля появляется единичный сигнал, то по импульсу Ј, с выхода элемента И 14 в регистр 2 адреса записывается адрес МК типа F.

Единичный сигнал с пятого выхода дешифратора признака 8 открывает магистральный элемент 19, разрешает запись в регистр 5 логических условий, через элемент ИЛИ 12 поступает на инверсный управляющий вход мультиплексора 7 логических условий,с выхода поля J.3 считывается адресный код Lro модуля, который через открытый магистральный элемент 19 поступает в шину 27 адреса. Так как имеется МК типа F, то третий выход дешифратора признака не возбуждается, а магист50

ральный элемент 20 остается закрытым и в шину 24 режима поступает нулевой сигнал с выхода младшего разряда магистрального элемента 19. Одновременно запрашивать коды логических условий нескольких модулей нельзя. При совпадении адресов в блоке 9 сравнения L-ro модуля разрешается прохождение сигнала запроса через элемент И 16, который поступает на вход элемента И 18. Этот сигнал открывает магистральный элемент 21 и разрешает

прохождение кода логичес-ких условий в jg младший разряд выходов кода адреса

шину 28 данных, которые в N-м модуле записываются в регистр 5 логических условий по импульсу 2. Одновременно из поля 1.2 в регистр 3 микроопераций записывается очередной микрооперационный код.

Таким образом организуется взаимодействие модулей распределенной системы и их согласованное функционирование .

Формула изобретения

20

блока памяти микрокоманд являются с шими разрядами информационных входо мультиплексора логических условий, ход которого соединен с младшим раз г дом первой группы информационных вх дов мультиплексора адреса, вторая г па входов кода операции мультиплекс ра адреса является группой входов к да операций модуля, вторая группа в дов мультиплексора адреса соединена с шиной данных, третий выход дешифр тора признака соединен с управляющи входом второго магистрального элеме та, с младшим разрядом информационн входов первого магистрального элеме та ИЛИ, выход которого соединен с и версным входом разрешения мультипле сора логических условий, четвертый ход дешифратора признака является в ходом запроса модуля и соединен с п вым входом третьего элемента И, вто рой инверсный вход которого являетс входом ответа на запрос модуля, а в ход соединен с вторым входом второг элемента ИЛИ, пятый выход дешифрато признака соединен с третьим входом второго элемента ИЛИ, первый вход п вого элемента ИЛИ является входом п ка модуля, а выход соединен с входо

Программируемый управляющий модуль, содержащий блок памяти микрокоманд, 25 регистры адреса и микрооперации, мультиплексоры адреса и логических условий, дешифратор признака, триггер пуска, первый и второй элементы ИЛИ, первый, второй, третий элементы И, пер- 30 вый и второй магистральные элементы, Ьричем выходы поля признака блока памяти микрокоманд соединены с входами дешифратора признака, первый выход которого является выходом состояния модуля и соединен с первым адресным входом мультиплексора адреса, информационные выходы которого соединены с информационными входами регистра адреса,

г

35

45

информационные выходы которого соеди- 40 Устан°вки триггера пуска, выход кото- нены с адресными входами блока памяти микрокоманд, старший разряд поля признака которого соединен с входом сброса регистра микроопераций, выходы которого являются выходами микроопераций модуля, а выход Конец работы соединен с входами сброса триггера, . пуска и регистра адреса, шестой выход дешифратора признака и выходы кода микроопераций блока памяти микрокоманд являются информационными входами регистра микроопераций и магистрального элемента, выходы которого соединены с шиной данных выходы кода логических условий блока памяти микрокоманд соединены с адресными входами мультиплексора логических условий и старшими разрядами информационных входов первого магистрального элемента,

50

55

рого соединен с первыми входами второго и первого элементов И, вторые входы которых являются соответственно вторым и первым входами синхронизации модуля, а выходы соединены соответственно с входами записи регистров микроопераций и адреса, отличающийся тем, что, с целью повышения быстродействия модуля, в него дополнительно введены регистры сравнения и логических условий, блок сравнения, третий элемент ИЛИ, четвертый и пятый элементы И и третий магистральный элемент, информационные выходы которого соединены с шиной данных, шестой выход дешифратора признака и выходы кода мик рооперации блока памяти микрокоманд являются информационными входами регистра сравнения, выходы которого сое950710

старшие разряды информационных выходов которого соединены с шиной адреса, а младшие - с шиной режима, старшие разряды выходов кода адреса блока па- мяти микрокоманд соединены со старшими разрядами первой группы информационных входов мультиплексора адреса, входы логических условий модуля и

младший разряд выходов кода адреса

блока памяти микрокоманд являются старшими разрядами информационных входов мультиплексора логических условий, выход которого соединен с младшим разря- дом первой группы информационных входов мультиплексора адреса, вторая группа входов кода операции мультиплексора адреса является группой входов кода операций модуля, вторая группа входов мультиплексора адреса соединена с шиной данных, третий выход дешифратора признака соединен с управляющим входом второго магистрального элемента, с младшим разрядом информационных входов первого магистрального элемента ИЛИ, выход которого соединен с инверсным входом разрешения мультиплексора логических условий, четвертый выход дешифратора признака является выходом запроса модуля и соединен с первым входом третьего элемента И, второй инверсный вход которого является входом ответа на запрос модуля, а выход соединен с вторым входом второго элемента ИЛИ, пятый выход дешифратора признака соединен с третьим входом второго элемента ИЛИ, первый вход первого элемента ИЛИ является входом пуска модуля, а выход соединен с входом

Устан°вки триггера пуска, выход кото-

рого соединен с первыми входами второго и первого элементов И, вторые входы которых являются соответственно вторым и первым входами синхронизации модуля, а выходы соединены соответственно с входами записи регистров микроопераций и адреса, отличающийся тем, что, с целью повышения быстродействия модуля, в него дополнительно введены регистры сравнения и логических условий, блок сравнения, третий элемент ИЛИ, четвертый и пятый элементы И и третий магистральный элемент, информационные выходы которого соединены с шиной данных, шестой выход дешифратора признака и выходы кода микрооперации блока памяти микрокоманд являются информационными входами регистра сравнения, выходы которого соединены с первой группой информационных входов блока сравнения, выход которого соединен с первыми входам четвертого и пятого элементов И, вторые вхо-,. ды которых соединены с шиной режима, а выходы соединены соответственно с вторым адресным входом мультиплексора адреса, вторым входом первого элемента ИЛИ и управляющим входом третьего JQ магистрального элемента, группа входов логических условий и младший разряд выходов кода адреса блока памяти микрокоманд являются входами третьего магистрального элемента, выход BTO-JJ рого элемента И соединен с входами записи регистра сравнения и регистра логических условии, выходы которого соединены с младшими разрядами информационных входов мультиплексора логичес- Q

проверки

передачи АКУ

запроса ЛУ

конца работы

0...0

Адрес МК типа D+1 Адрес МК типа D+1

ких условий, информационные входы регистра логических условий соединены с шиной данных, второй выход дешифратора признака соединен с входом разрешения регистра сравнения, третий выход дешифратора признака соединен с первым входом третьего элемента ИЛИ, выход которого соединен с входом управления первого магистрального элемента, пятый выход дешифратора признака соединен с вторым входом третьего элемента ИЛИ и с входом разрешения регистра логических условий, вторая группа информационных входов блока сравнения соединена с шиной адреса, шины адреса, данных и режима являются соответствующими входами-выходами модуля.

0...0

0...0 0...0 0...0

Код L-ro Адрес МК модулятипа Е

или F

Код

модуля и

0...0

0. ..О

V

29

Фиг,1

Фие.2

Г/ч МП ожйает АКУ, считыбае/лся /iff mt/na С

( Начало Л

Ожидается AM и швы передачи свободны

| Устройство для автоматического раз-гОНА и ТОРМОжЕНия дВигАТЕля CTAHKA СпРОгРАММНыМ упРАВлЕНиЕМ | 1975 |

|

SU834669A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР по заявке № 4370638/24, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-05-15—Публикация

1989-05-03—Подача