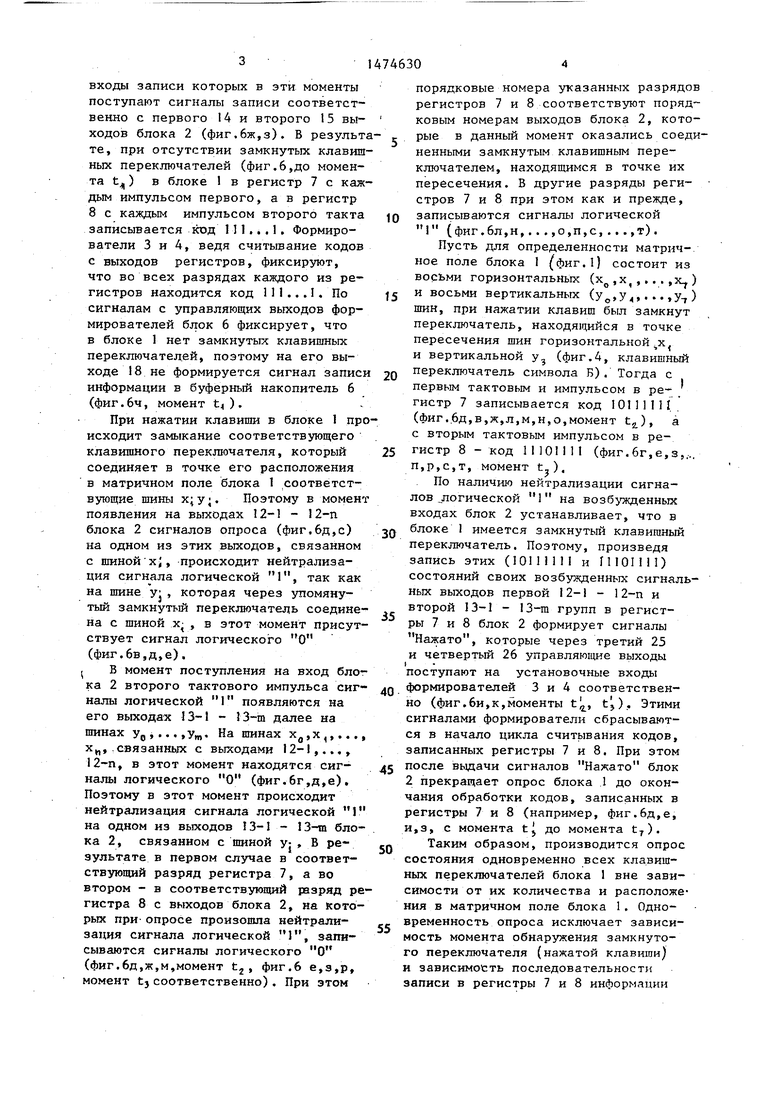

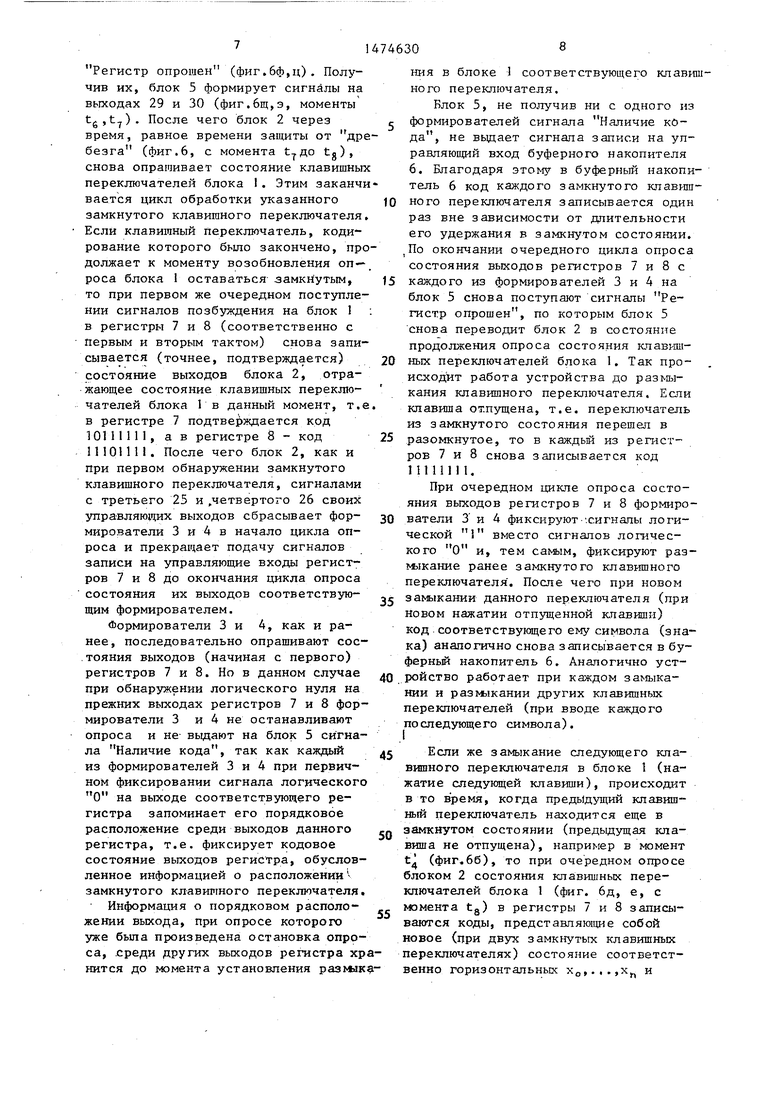

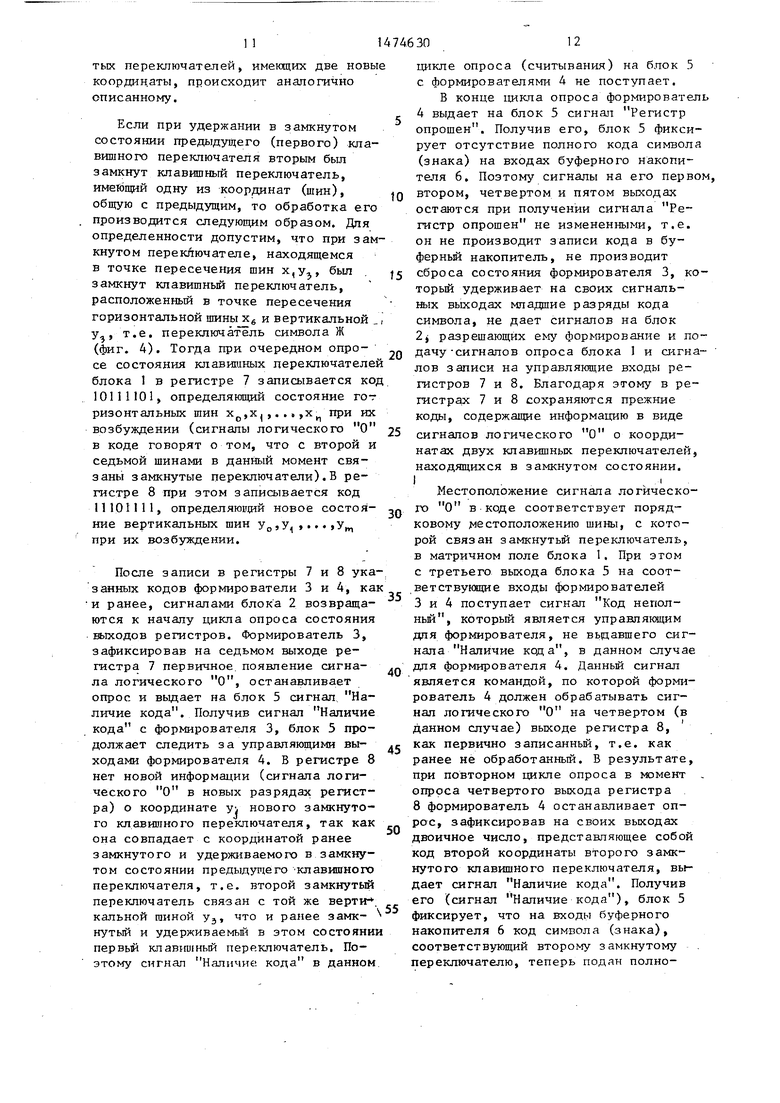

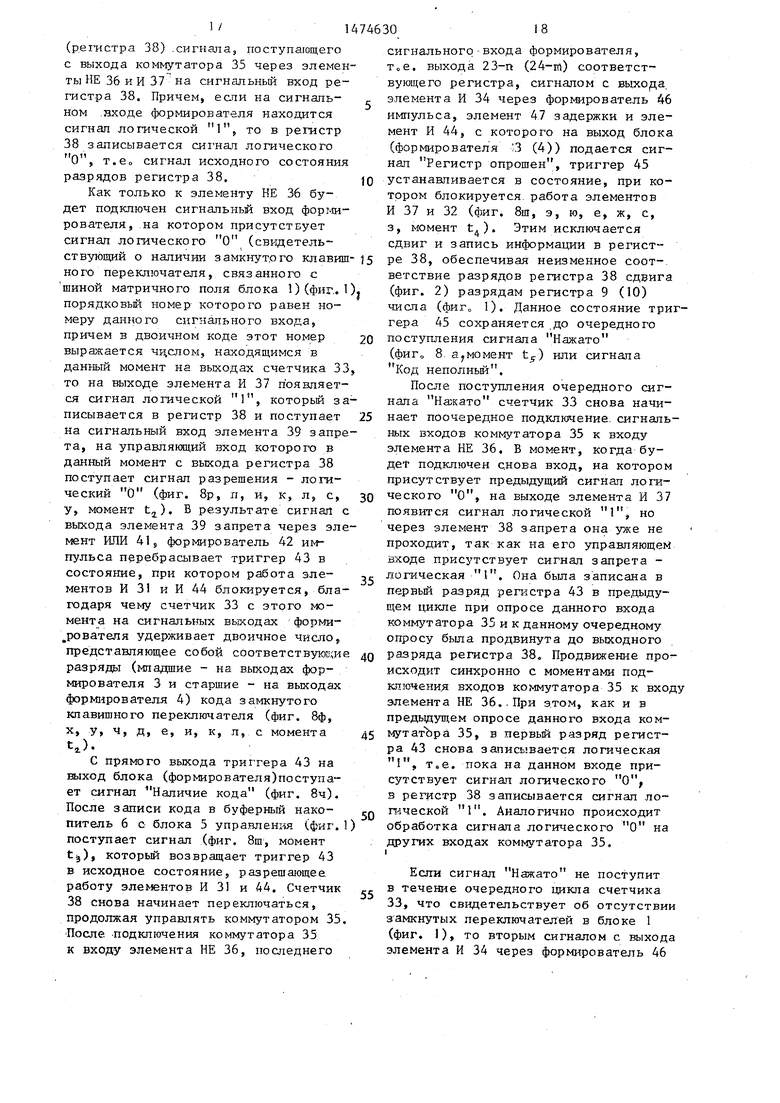

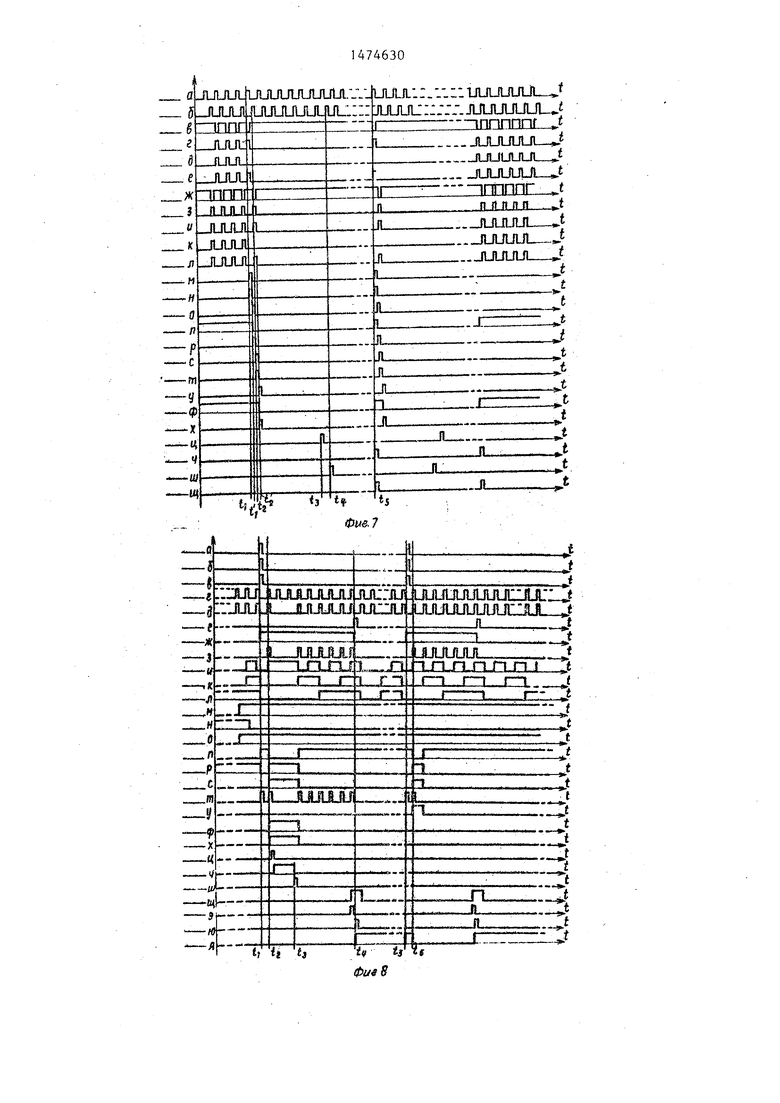

ствующий о наличии замкнутого клавиш-15 ре 38, обеспечивая неизменное соотного переключателя, связанного с шиной матричного поля блока 1)(фнг. порядкевый номер которого равен номеру данного сигнального входа, причем в двоичном коде этот номер выражается числом, находящимся в данный момент на выходах счетчика 3 то на выходе элемента И 37 появляется сигнал логической 1, которьй зписывается в регистр 38 и поступает на сигнальный вход элемента 39 запрта, на управляющий вход которого в данный момент с выхода регистра 38 поступает сигнал разрешения - логический О (фиг. 8р, л, и, к, л, с, у, момент t2). В результате сигнал выхода элемента 39 запрета через элмент ИЛИ 41, формирователь 42 импульса перебрасывает триггер 43 в состояние, при котором работа элементов И 31 к И 44 блокируется, благодаря чему счетчик 33 с этого момента на сигнальных вь;ходах форми- рователя удерживает двоичное число, представляющее собой соответствующи разряды (младшие - на выходах формирователя 3 и старшие - на выходах формирователя 4) кода замкнутого клавишного переключателя (фиг. 8ф, х, у, ч, д, е, и, к, л, с момента

ч.

С прямого выхода триггера 43 на выход блока (формирователя)поступа- ет сигнал Наличие коца (фиг. 8ч). После записи кода в буферный накопитель 6 с блока 5 управления (фиг. поступает сигнал (фиг. 8ш, момент t3), которьй возвращает триггер 43 в исходное состояние, разрешающее работу элементов И 31 и 44. Счетчик 38 снова начинает переключаться, продолжая управлять коммутатором 35 После подключения коммутатора 35 к входу элемента НЕ 36, последнего

0 ческого О 0

появится сигнал логической 1,

5

5

0

5

ветствие разрядов регистра 38 сдвига (фиг. 2) разрядам регистра 9 (10) числа (фигс 1). Данное состояние триггера 45 сохраняется до очередного поступления сигнала Нажато (фиг0 8 а момент tf) или сигнала Код неполный.

После поступления очередного сигнала Нажато счетчик 33 снова начинает поочередное подключение сигнальных входов коммутатора 35 к входу элемента НЕ 36, В момент, когда будет подключен снова вход, на котором присутствует предыдущий сигнал логи- п, на выходе элемента И 37

но

через элемент 38 запрета она уже не проходит, так как на его управляющем йкоде присутствует сигнал запрета - логическая 1. Она была записана в первый разряд регистра 43 в предыдущем цикле при опросе данного входа коммутатора 35 и к данному очередному опросу была продвинута до выходного разряда регистра 38. Продвижение происходит синхронно с моментами подключения входов коммутатора 35 к входу элемента НЕ 36. При этом, как и в предыдущем опросе данного входа коммутатора 35, в первый разряд регистра 43 снова записывается логическая 1, т«,е. пока на данном входе присутствует сигнал логического О, в регистр 38 записывается сигнал логической 1. Аналогично происходит обработка сигнала логического О на

других входах коммутатора 35, i

Если сигнал Нажато не поступит в течение очередного цикла счетчика 33, что свидетельствует об отсутствии замкнутых переключателей в блоке 1 (фиг. 1), то вторым сигналом с выхода элемента И 34 через формирователь 46

и элемент И 49 разряды регистра 38 будут установлены в исходное Состояние, т.е. обнулены. Работа элемента И 49 разрешена сигналом с выхода

триггера 48, который в это (разрешающее) состояние устанавливается сигг налом с выхода элемента 47 задержки в конце каждого цикла счетчика 33 При этом длительность задержки эле- мента 47 превыщает длительность импульса на выходе формирователя 46, чем обеспечивается срабатывание элемента И 49 только в том случае, если триггер 48 остается в разрешающем состоянии не менее двух циклов. В исходное состояние триггер 48 сбрасывается сигналом логической 1 с выхода элемента НЕ 36, которьй (сиг

нал логической 1)появляется в те-1 чение цикла счетчика 33 - в течение цикла опроса выходов регистра 7 (8) числа (фиг. 1) всегда, если хотя бы на одном сигнальном входе элемента 35 присутствует сигнал логического О, свидетельствующий о наличии замкнутого Переключателя.

При поступлении сигнала Код не полный разрешается работа элемента И 40, что позволяет сигналу с выхо- да элемента И 37, минуя элемент 39 запрета, установить триггер 43 в состояние Наличие кода. Далее работа каждого из формирователей кода (первого 3 и второго 4) происходит ана- ло гично.

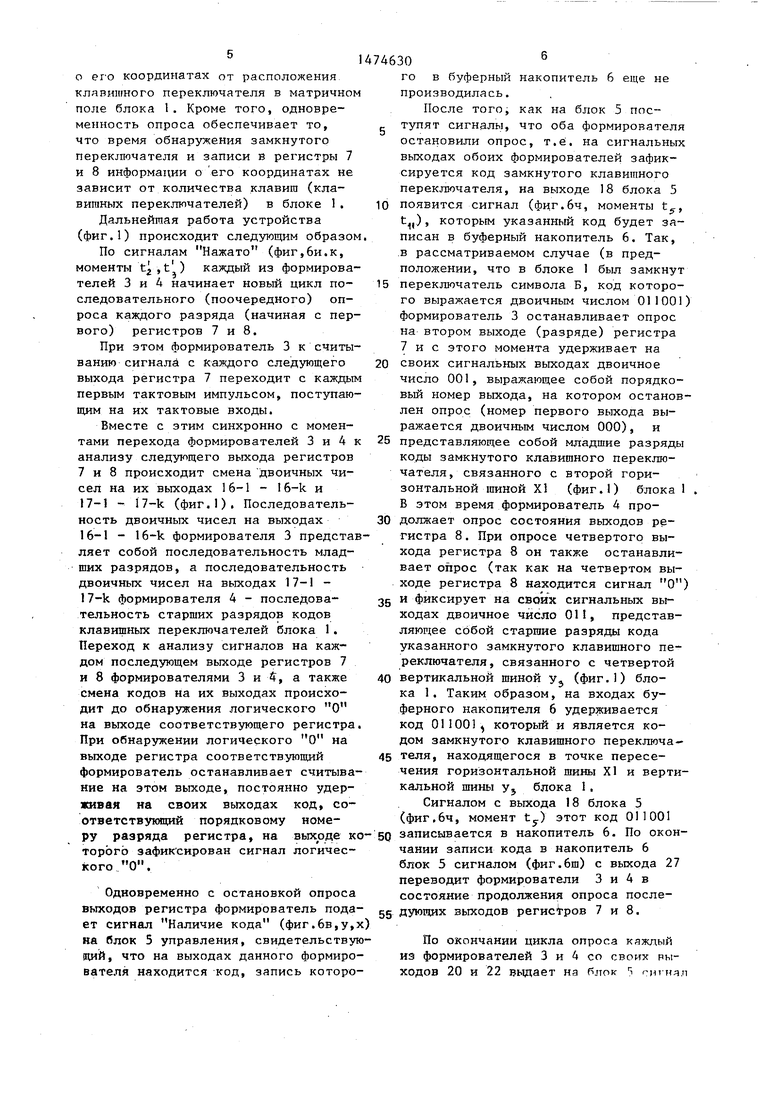

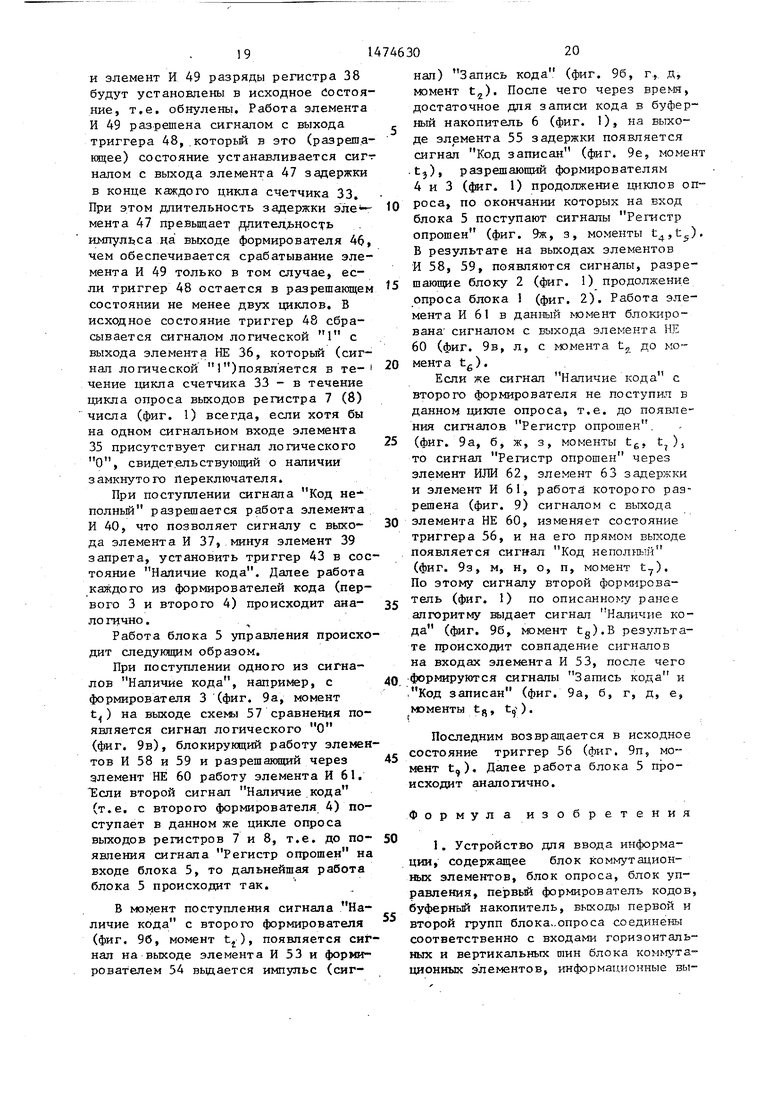

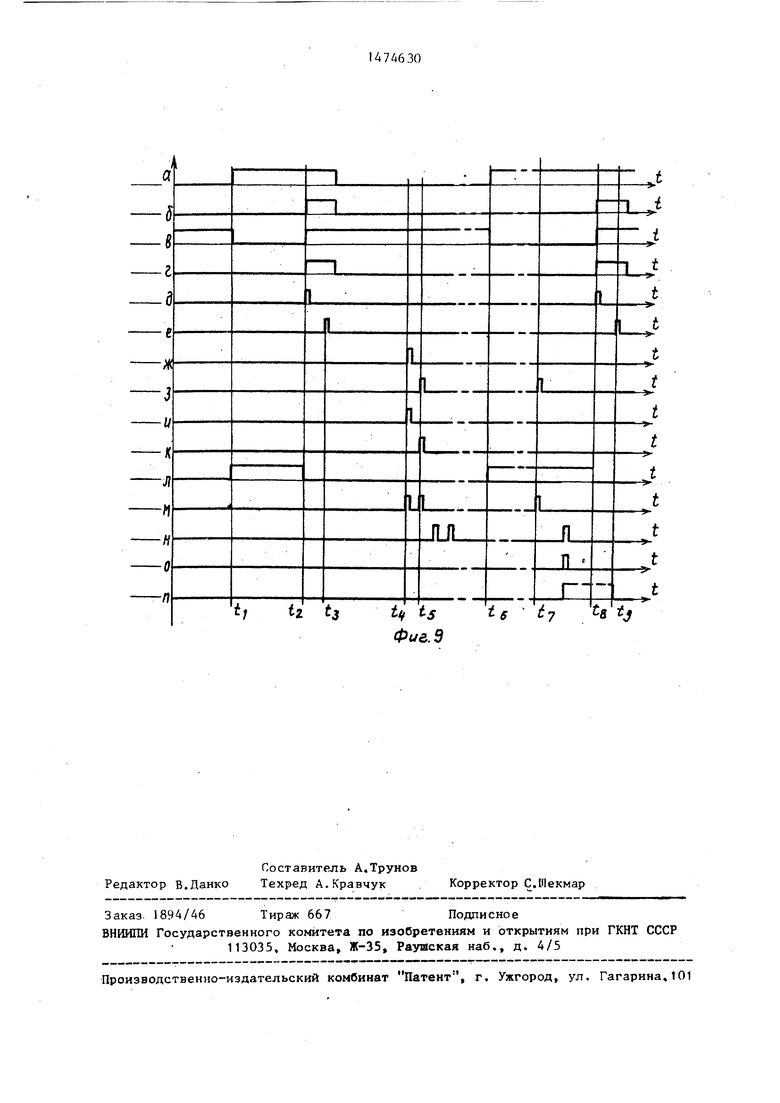

Работа блока 5 управления происходит следующим образом,

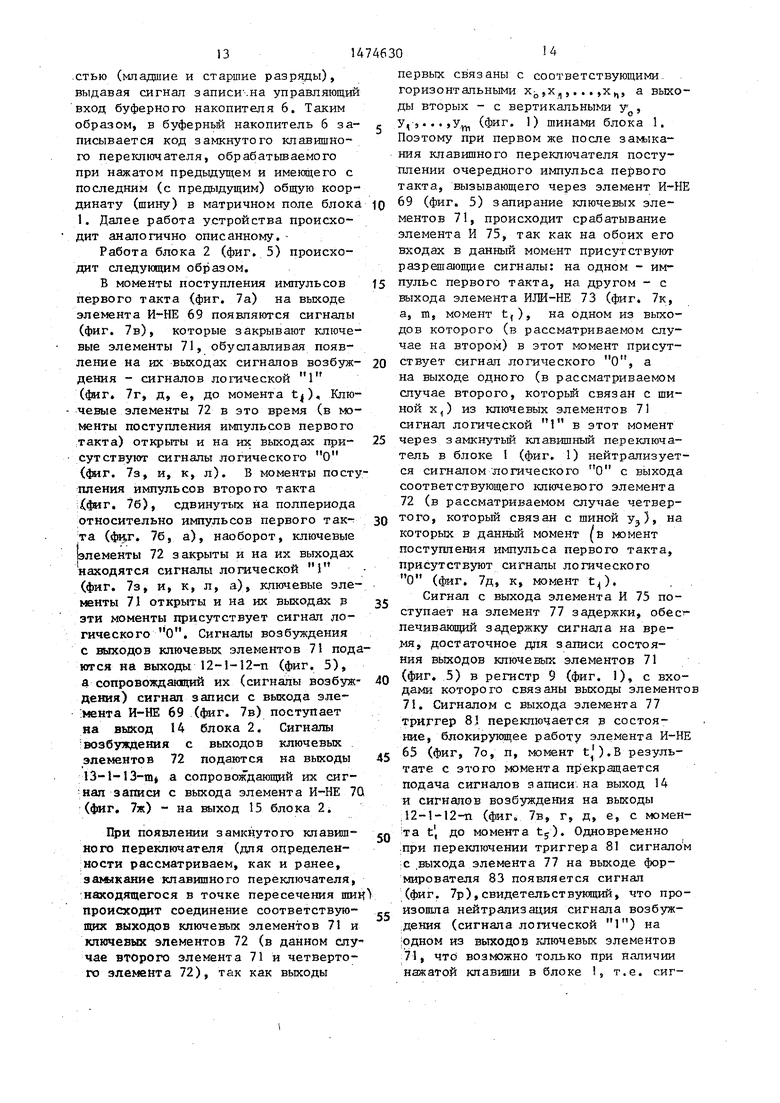

При поступлении одного из сигналов Наличие кода, например, с формирователя 3 (фиг. 9а, момент t) на выходе схемы 57 сравнения появляется сигнал логического О (фиг. 9в), блокирующий работу элемен

тов И 58 и 59 и разрешающий через элемент НЕ 60 работу элемента И 61. Если второй сигнал Наличие кода (т.е. с второго формирователя 4) поступает в данном же цикле опроса выходов регистров 7 и 8, т.е. до появления сигнала Регистр опрошен на входе блока 5, то дальнейшая работа блока 5 происходит так.

В момент поступления сигнала Наличие кода с второго формирователя (фиг. 96, момент tt), появляется сигнал на выходе элемента И 53 и формирователем 54 выдается импульс (сигД,

нал) Запись кода (фиг. 96, г, момент t2). После чего через время, достаточное для записи кода в буферный накопитель 6 (фиг. 1), на выходе элемента 55 задержки появляется сигнал Код записан (фиг. 9е, момент tj), разрешающий формирователям 4 и 3 (фиг. 1) продолжение циклов опроса, по окончании которых на вход блока 5 поступают сигналы Регистр опрошен (фиг. 9ж, з, моменты t4,t5). В результате на выходах элементов И 58, 59, появляются сигналы, разрешающие блоку 2 (фиг. 1) продолжение опроса блока (фиг. 2). Работа элемента И 61 в данный момент блокирована сигналом с выхода элемента НЕ 60 (фиг. 9в, л, с момента L7 до мо10Ш

5

30 5

0

5

0

5

20 мента tg).

Если же сигнал Наличие кода с второго формирователя не поступил в данном цикле опроса, т.е. до появления сигналов Регистр опрошен

(фиг. 9а, б, ж, з, моменты t6, t )s то сигнал Регистр опрошен через элемент ИЛИ 62, элемент 63 задержки и элемент И 61, работа которого разрешена (фиг. 9) сигналом с выхода элемента НЕ 60, изменяет состояние триггера 56, и на его прямом выходе появляется сигнал Код неполнкй (фиг. 9з, м, н, о, п, момент t). По этому сигналу второй формирователь (фиг. 1) по описанному ранее алгоритму выдает сигнал Наличие кода (фиг. 96, момент tg).B результате происходит совпадение сигналов на входах элемента И 53, после чего формируются сигналы Запись кода и Код записан (фиг. 9а, б, г, д, е, моменты tfi, t)

Последним возвращается в исходное состояние триггер 56 (фиг. 9п, момент t,). Далее работа блока 5 происходит аналогично.

Формула изобретения

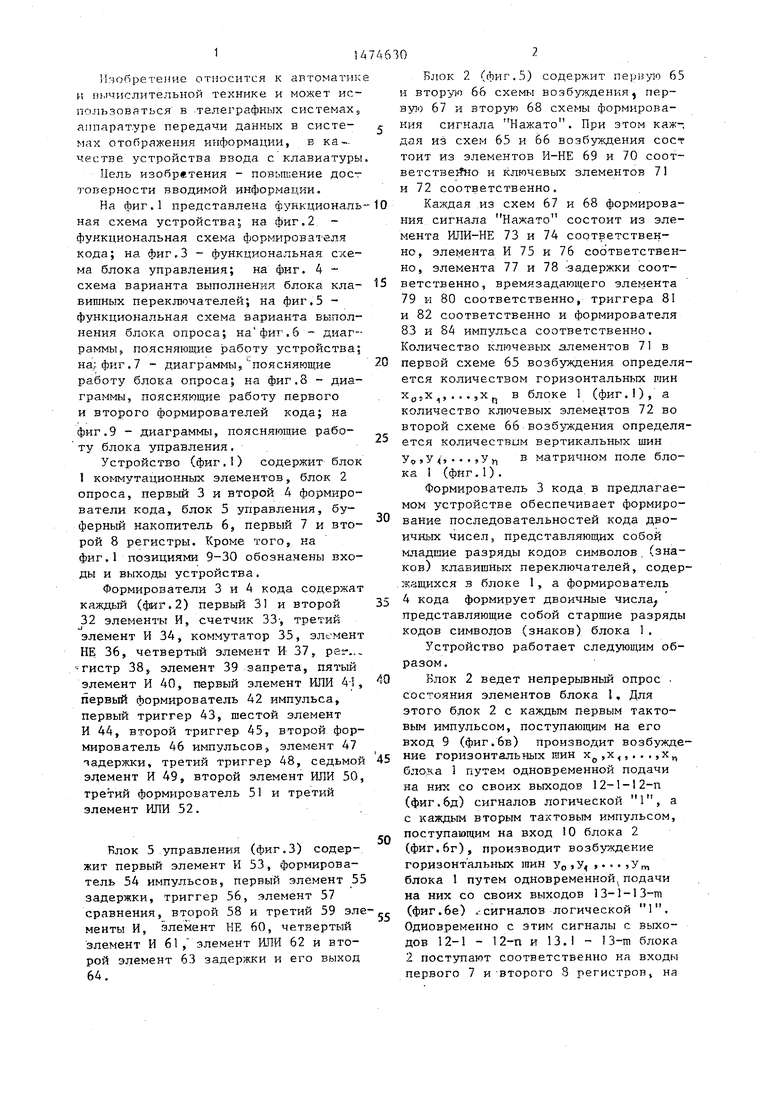

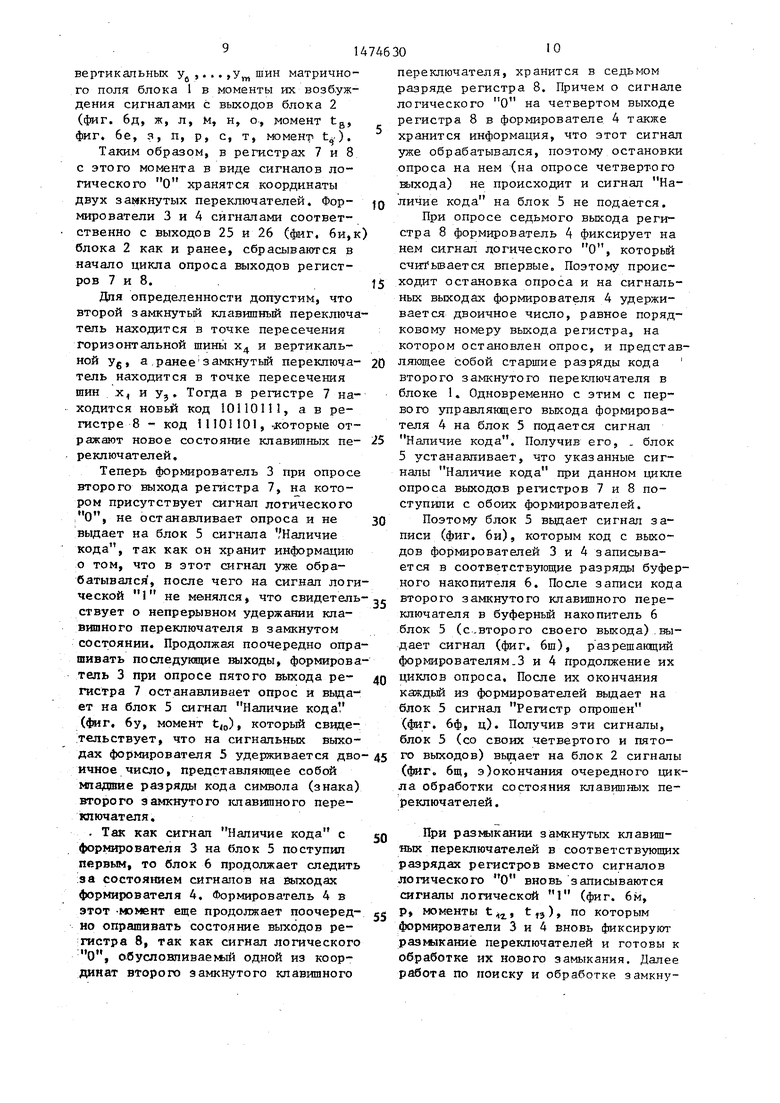

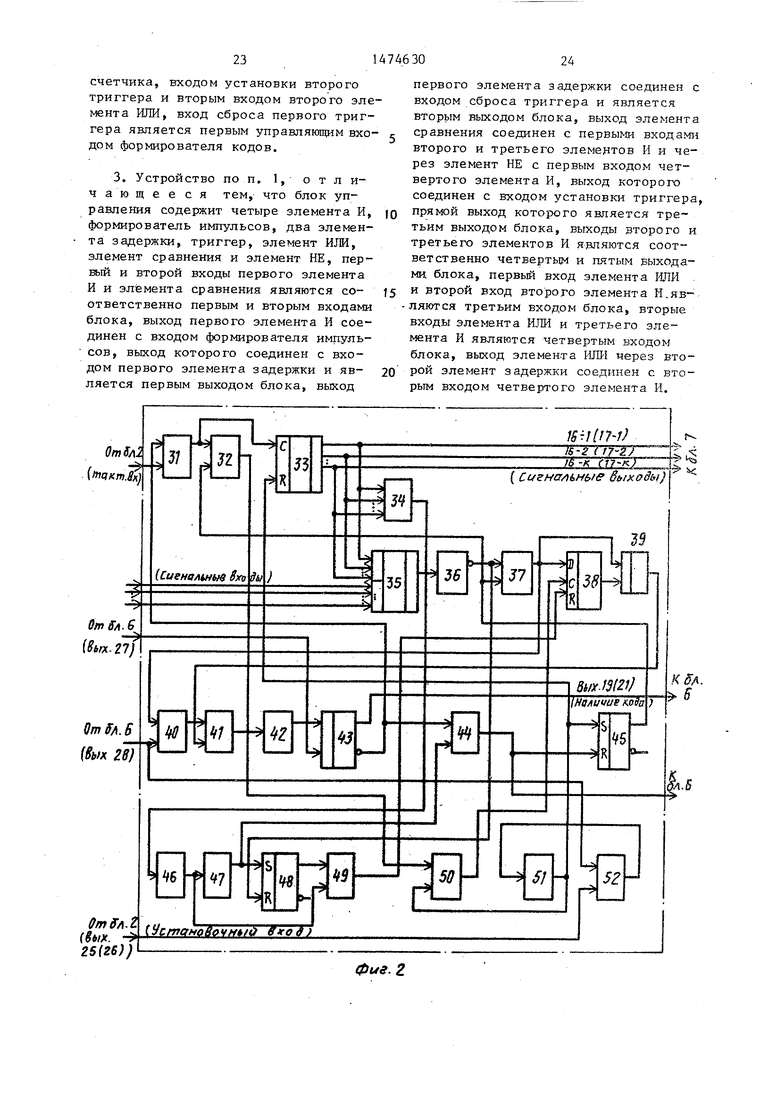

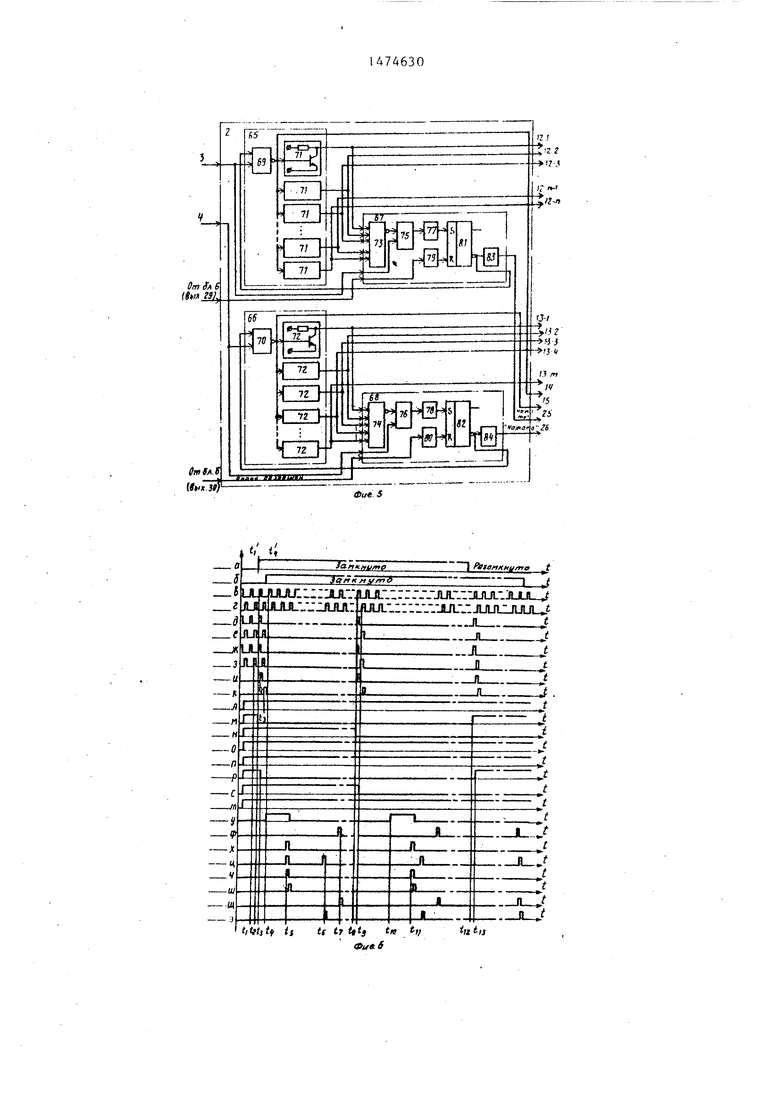

1. Устройство для ввода информации, содержащее блок коммутационных элементов, блок опроса, блок управления, первьй формирователь кодов, буферный накопитель, выходы первой и второй групп блока, опроса соединены соответственно с входами горизонтальных и вертикальных шин блока коммутационных элементов, информационные выходы первого формирователя кодов соединены с информационными входами первой группы буферного накопителя, выходы которого являются информаци- онными выходами устройства, отличающееся тем, что, с целью повышения достоверности вводимой информации, в него введены два регистра и второй формирователь кодов, информационные входы первого и второго регистров соединены соответственно с выходами первой и второй групп блока опроса, первый и второй выходы блока опроса соединены с вхо- дамп синхронизации соответственно первого и второго регистров, выходы которых соединены с информационными входами соответственно первого и второго формирователей кодов, третий и четвертый выходы блока опроса соединены с установочными входами соответственно перрого и второго формирователей кодов, информационные выходы второго формирователя кода соедине- ны с информационными входами второй группы буферного накопителя, вход записи которого соединен с первым выходом блока управления, второй и третий выходы которого соединены со- ответственно с первыми и вторыми управляющими входами формирователей кодов, третий и четвертый выходы блока управления соединены соответствей- но с первым и вторым управляющими

входами блока опроса, первые управляющие выходы первого и второго формрователей кода соединены соответст- венно с первым и вторым входами блока управления, вторые управляющие выходы первого и второго формирователей кода соединены соответственно с третьим и четвертым входами блока управления, первый вход синхронизации блока опроса и вход синхрониза- ции первого формирователя кода являются первым тактовым входом устройства, второй вход синхронизации блока опроса и вход синхронизации второго формирователя кода являются вторым тактовым входом устройства.

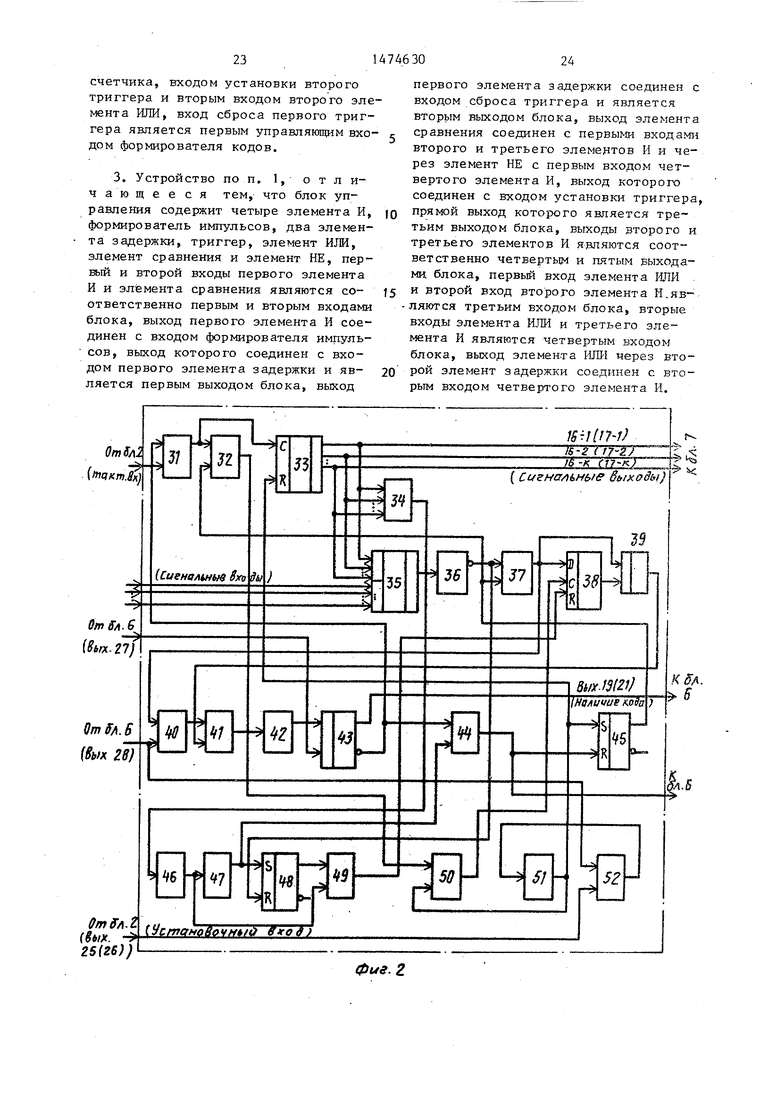

2. Устройство по п. 1, отличающееся тем, что каждый из формирователей кодов содержит семь элементов И, счетчик коммутатор, элемент НЕ, регистр, элемент запрета, три элемента ИЛИ,три триггера, три формирователя импульсов, элемент

задержки, первый вход первого элемента И является входом синхронизации формирователя кода, информационные входы коммутатора являются информационными входами формирователя, выход первого элемента И соединен с первым входом второго элемента И и со счетным входом счетчика, выходы которого соединены с входами третьего элемента И, адресными входами коммутатора и являются информациан- ными выходами формирователя, выход коммутатора через элемент НЕ соединен с первым входом четвертого элемента И и входом сброса третьего триггера, выход четвертого элемента И соединен с первым входом пятого элемента И, с первым входом элемента запрета и с информационным входом регистра, выход которого соединен с вторым входом элемента запрета, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен через первый формирователь импульсов с входом установки первого триггера, прямой выход которого является первым управляющим выходом формирователя кода, а инверсный- соединен с вторым входом первого элемента И и с первым входом шестого (элемента И, выход которого соединен с входом сброса второго триггера и является вторым управляющим эыходом формирователя кодов, прямой выход второго триггера соединен с вторыми входами второго и четвертого элементов И, первый вход третьего элемента ИЛИ является установочным входом формирователя кодов, вторые входы третьего элемента ИЛИ и пятого элемента И являются вторым управляющим входом формирователя кодов, выход третьего элемента И соединен с входом второго формирователя импульсов, выход которого соединен с первым входом седьмого элемента И и через элемент задержки с входом установки третьего триггера и вторым входом шестого элемента И, прямой выход третьего триггера соединен с вторым входом седьмого элемента И, выход которого соединен с входом сброса регистра, выход второго элемента И соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом синхронизации регистра, выход третьего элемента ИЛИ соединен через третий формирователь импульсов с входом сброса

счетчика, входом установки второго триггера и вторым входом второго элемента ИЛИ, вход сброса первого триггера является первым управляющим вхо- дом формирователя кодов.

3. Устройство по п. 1, отличающееся тем, что блок управления содержит четыре элемента И, формирователь импульсов, два элемента задержки, триггер, элемент ИЛИ, элемент сравнения и элемент НЕ, первый и второй входы первого элемента И и элемента сравнения являются со- ответственно первым и вторым входами блока, выход первого элемента И соединен с входом формирователя импульсов, выход которого соединен с входом первого элемента задержки и яв- ляется первым выходом блока, выход

первого элемента задержки соединен с входом сброса триггера и является вторым выходом блока, выход элемента сравнения соединен с первыми входами второго и третьего элементов И и через элемент НЕ с первым входом четвертого элемента И, выход которого соединен с входом установки триггера, прямой выход которого является третьим выходом блока, выходы второго и третьего элементов И являются соответственно четвертые и пятым выходами блока, первый вход элемента ИЛИ и второй вход второго элемента Н.являются третьим входом блока, вторые входы элемента ИЛИ и третьего элемента И являются четвертым входом блока, выход элемента ИЛИ через Второй элемент задержки соединен с вторым входом четвертого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 1997 |

|

RU2121754C1 |

| Устройство записи-воспроизведения многоканальной цифровой информации на магнитный носитель | 1991 |

|

SU1777176A1 |

| Коммутатор | 1985 |

|

SU1272494A1 |

| Устройство для запуска импульсных невзрывных источников сейсмических колебаний | 1987 |

|

SU1453348A1 |

| Устройство для контроля монтажа | 1985 |

|

SU1352505A1 |

| Преобразователь угла поворота вала в код | 1988 |

|

SU1522408A1 |

| Коммутатор | 1985 |

|

SU1265990A2 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1067453A1 |

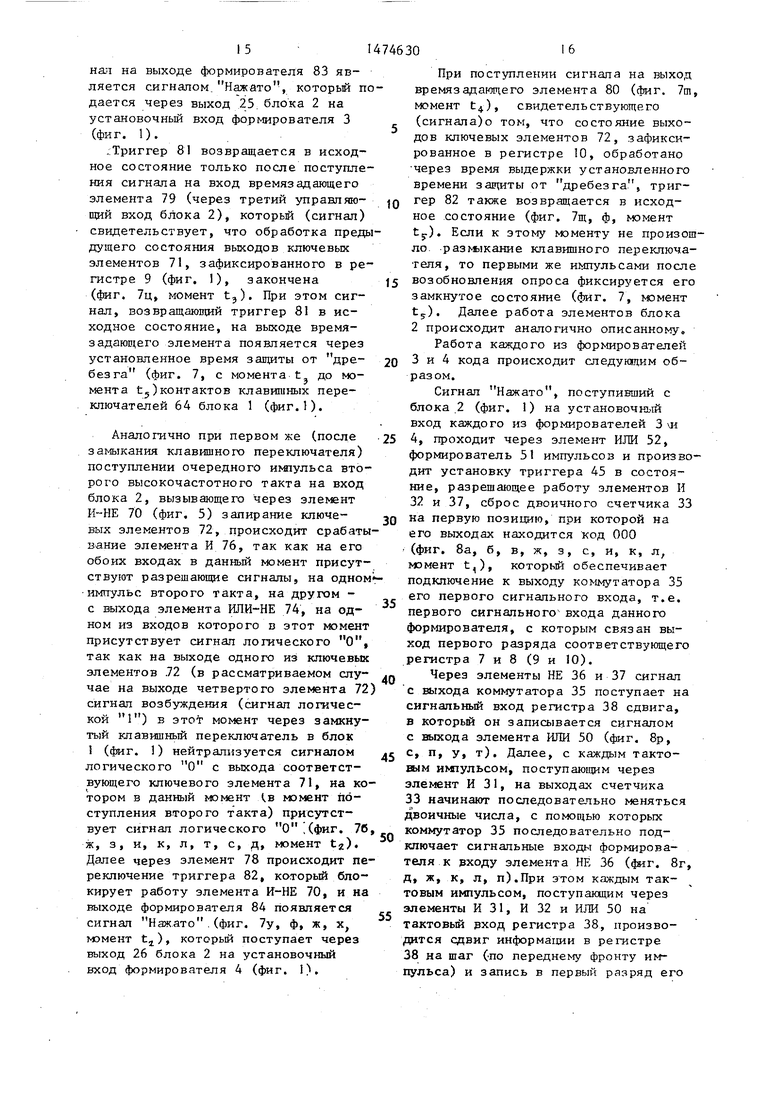

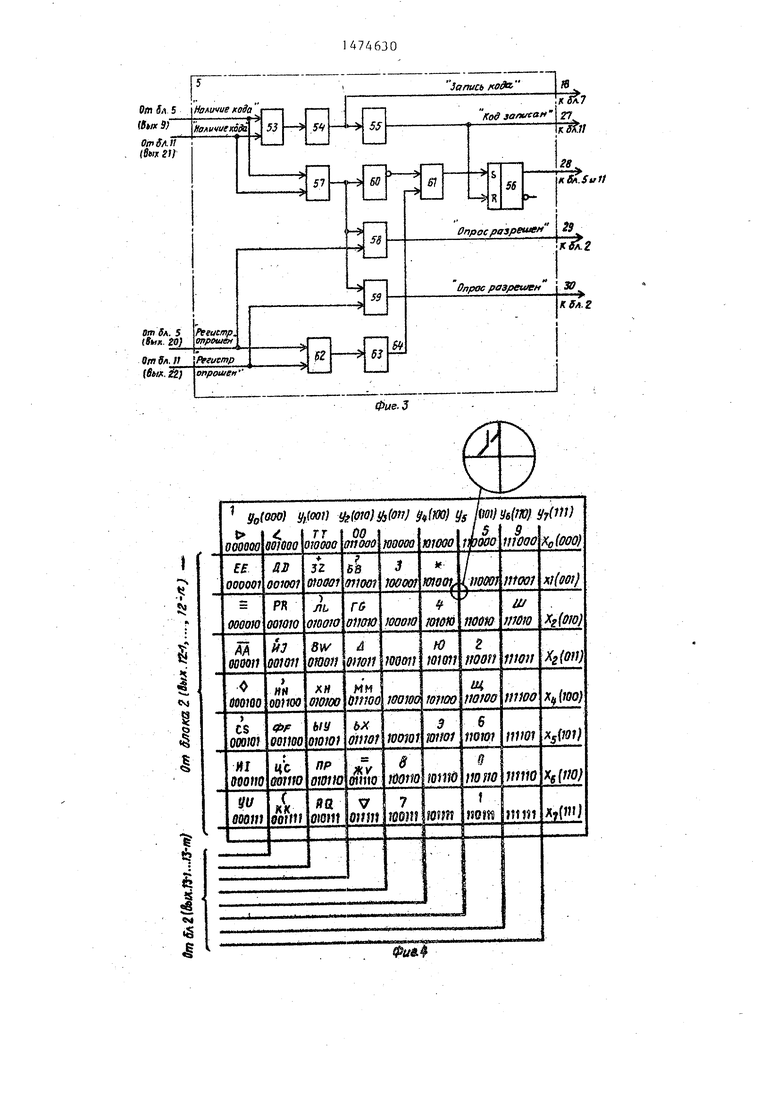

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в телеграфных системах, аппаратуре передачи данных, в системах отображения информации в качестве устройства ввода с клавиатуры. Целью изобретения является повышение достоверности вводимой информации. Устройство содержит блок 1 коммутационных элементов, блок 2 опроса, первый 3 и второй 4 формирователи кода, блок 5 управления, буферный накопитель 6, первый 7 и второй 8 регистры. Цель изобретения достигается за счет того, что блок 2 осуществляет одновременный опрос всех переключателей блока 1 вне зависимости от их расположения и количества в поле клавиатуры, а конструкция формирователей кодов 3 и 4 такова, что позволяет определить верную последовательность нажатия переключателей в блоке 1, если моменты нажатия отличались более чем на один период тактов высокой частоты.2 з.п. ф-лы, 9 ил.

От$л2 .3я)

Omff/t.6

(Sbn-Zlj

QmffA.B (А/х 2В)

OmSA.t (fax. -9 26(гб))

г-фиг. 2

Qtn 5л 5

ОтблП (ffwx гп

am ft. 5 (Вия ЯЦ

От 6л. Л (бык. Щ

М

1

I

«ь

«4

Ǥ

Кбл.5а11

Фи&$

ft A S ttuxJSb

Cm I

it

Фие 5

| Техника средств связи | |||

| Научно- технический сборник | |||

| Сер.ТПС, вып.7 ,(15), М., 1980, с.44-47. |

Авторы

Даты

1989-04-23—Публикация

1987-07-07—Подача