полнительного триггера результата, первый и второй входы и выхрд двенадцатого элемента И соединены соот-. ветственно с инверсным выходом триггера анализа четности, выходом пятого элемента И и первым входом второго элемента ИЛИ, второй вход которого пoдклfoчeн к входу начальной установки устройства, а выход второго элемента ИЛИ соединен с входами сброса триггера анализа четности, триггера запоминания результата, дополнительного триггера результата и вторым установочным входом триггера результа а.

| название | год | авторы | номер документа |

|---|---|---|---|

| Однобитовый процессор программируемого контроллера | 1986 |

|

SU1476464A1 |

| Программируемый контроллер | 1984 |

|

SU1453404A1 |

| Программируемый контроллер | 1985 |

|

SU1509887A2 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Многоканальный преобразователь код-частота | 1985 |

|

SU1267621A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Устройство для хранения информации с контролем | 1989 |

|

SU1691897A1 |

| Устройство для сопряжения датчиков с ЭВМ | 1985 |

|

SU1282108A1 |

| СИГНАТУРНЫЙ АНАЛИЗАТОР | 1991 |

|

RU2017209C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

ОДНОБИТОВОЕ ОПЕРАЦИОННОЕ УСТРО СТВО, содержащее триггер результата, триггер анализа четности, триггер запоминания результата, дополнительный триггер результата и семь элементов И, при этом первый и второй входы и выход первого элемента И соединены соответственно с входом бита состояния устройства, выходом второго элемента И и входом сброса триггера результата, выход которого подключен к информационному входу триггера запоминания результата и информационному выходу устройства, первые входы второго и третьего элементов И соединены с первым синхровходом устройства, второй вход третьего элемента И и первый вход четвертого элемента И подключены к входу кода операции устройства, второй вход второго элемента И соединен с входом кода операиии устройства/второй вход четвертого элемента- И и первый вход пятого элемента И подключены к второму синхровходу устройства, второй вход пятого элемента И соединен с входом кода операиии устройства, первый, второй и третий входы и выход uiecToro элемента И подключены соответственно к выходу третьего элемента И, выходу дополнительного триггера результата, входу конца ветви устройства и первому установочному входу триггера результата, первый и второй входы и выход седьмого элемента И соединены соответственно с выходом четвертого элемента И, входом конца ветви устройства и входом сброса дополнительного триггера результата, отличающееся тем, что, с целью расширения функииональных возможностей при обработке электрических цепей с параллельными ветвями, оно содержит дополнительно пять элементов И, два элемента ИЛИ и элемент И-НЕ, первый и второй входы и выход которого подключены соответственно к входу начала ветви устройства, выходу четвертого элемента И и синхровходу триггера анализа четности, инверсный выход которого соединен с информа1ионным входом этого триггера, i первый, второй и третий входы и выход восьмого элемента И подключены (Л соответственно к прймому выходу триггера анализа четности, входу начала ветви устройства, выходу четвертого элемента И и синхровходу триггера результата, первый и второй входы и выход девятого элемента И соединены соответственно с выходом триггера запоминания результата, j входом начала ветви устройства и информационным входом триггера pesy-V льтата, первый, второй и третий вхоЧ ды и выход десятого элемента И подО ключены соответственно к выходу третьего элемента И, входу начала ветви :л устройства, инверсному выходу триг4 гера анализа четности и синхровходу триггера запоминания результата, ND первый, второй и третий входы и выход одиннадцатого элемента И соедине-i ны соответственно с выходом третьего | элемента И, входом начала ветви устройства, прямым выходом триггера анализа четности и синхровходом дополнительного триггера результата, первый и второй входы и выход первого элемента ИЛИ подключены соответственно к выходу триггера результата, «ыходу дополнительного триггера результата и информационному входу до

Изобретение относится к вычислительной технике и предназначено для построения программируемых контроллеров (ПК). В программируемых контроллерах программа работы управляемого объек та задается в виде инструкций, пред ставляющих последовательность, воспроизводящую ступенчатую электричес кую схему управляемого объекта. Сту пенчатай электрическая схема строит ся из элементов ВХОД, ВЫХОД, ВЕТВЬ, К элементам ВХОД относится нормально разомкнутый или нормально замкнутый кбнтакт, соответствующий датчику, кнопке, включателю управляемого объ екта, к элементам ВЬТХОД - обмотка реле, пускателя, лампочка индикации Ступенчатая электрическая схема состоит из ряда электрических цепей. При этом каждая цепь состоит из одного или нескольких элементов ВХОД и заканчивается одним элементом ВЫХОД. Элементы ВХОД могут строиться в параллельные электрические ветви. Для этого используются элементы ВЕТВЬ. Ступенчатая электрическая схема в ПК обрабатывается с помощью однобитового Нулевого операционного устройства. Известно однобитовое операционное устройство, содержащее элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два триггера, элемен ты И и ИЛИ, которое позволяет обрабатывать электрические цепи, постро енные из элементов ВХОД, ВЕТВЬ и ВЫХОД. При этом каждая электрическа цепь может содержать параллельные ветви с одним элементом ВХОД Ц. Недостатком известного устройства являются ограниченные функционал ьные возможности, обусловленные не возможностью обработки сложных элек трических пепей, например цепей, содержащих более одного элемента ВХОД в параллельной ветви. Наиболее близким по технической сущности к предлагаемому является однобитовое операционное устройство, содержащее четыре триггера, семь элементов И и имеющее два синхровхода, вход бита состояния, вход приема сигналов НАЧАЛО ВЕТВИ и КОНЕЦ ВЕТВИ и трехразрядный вход кода oneраиии. Первый из разрядов кода операиии обусловлен формированием сигналов НАЧАЛО ВЕТВИ (НВТ) или КОНЕЦ ВЕТВИ (КВТ), второй обусловлен приемом бита состояния элемента ВХОД, и третий - формированием сигнала ВЫХОД после установки или очистки бита состояния элемента ВЫХОД. При этом вход сброса первого триггера, являющегося триггером результата, соединен с выходом первого элемента И, первый вход которого соединен с входом приема бита состояния элемента ВХОД, а второй вход - с входом второго элемента И, первый вход которого соединен с вторым разрядом входа кода операции устройства, а второй вход - с первым входом третьего элемента И и первым синхровходом устройства, второй вход третьего элемента И соединен с первым, входом четвертого элемента И и с первым разрядом входа кода операции устройства, второй вход четвертого эл лента И соединен с первым входом пятого элемента И и вторым синхровходом устройства, второй вход пятого элемента И соединен с третьим разрядом входа кода операции устройства, выход третьего элемента И соединен с первым входом шестого элемента И, второй вход которого соединен с выходом четвертого триггера, а третий вход - с первым входом седьмого элемента И и с входом конца ветви устройства , второй вход седьмого эле- мента И соединен с выходом четвертого элемента К, а выход - с первым входом сброса четвертого триггера, . второй вход сбрс1са которого соединен с входами сброса второго и третьего триггеров и первым установочным входом первого триггера, второй установочный вход которого соединен с выходом шестого элемента И. В известном устройстве второй триггер обеспечивает прием сигналов НАЧАЛО ВЕТВИ или КОНЕЦ ВЕТВИ и подключение входа бита состояния устройства к третьему триггеру вместо.

первого. Четвертый триггер обеспечивает перезапись информации с третьего триггера, если происходит обработка последующей ветви t2I,.

Известное однобитовое операиионное устройство имеет ограниченные функциональные возможности. Устройство может обрабатывать только цепи, заканчивающиеся одним элементом ВЫХОД,, однако в практике построения ступенчатых электрических схем часто образуются электрические цепи, заканчивающиеся параллельными вет-j вями, в каждой из которых содержатся элементы ВЫХОД, что обуславливает необходимость построения других дополнительных цепей, которые, оно может обрабатывать. Кроме того, устройство не может обрабатывать параллельные ветви, в которых последняя из параллельных ветвей содержит в себе новые параллельные ветви.

Цель изобретения - расширение функциональных возможностей устройства при обработке электрических цепей с параллельными ветвями.

/

Поставленная цель достигается

тем, что в однобитовое операционное устройство, содержащее триггер результата, триггер анализа четности, триггер запоминания результата, дополнительный триггер результата и семь элементов И, при этом первый и второй входы и выход первого элемента И соединены соответственно с входом бита состояния устройства, выходом второго элемента И и входом сброса триггера результата, выход которого подключен к информационному входу триггера запоминания резултата и информационному выходу устройства, первые входы второго и третьего элементов И соединены с первым синхровходом устройства, вход третьего элемента И и первый вход четвертого элемента И подключены к входу кода операции устройства, второй вход второго элемента соединен с входом кода операции устройства, второй вход четвертого элмента И и первый вход пятого элемента И подключены к второму синхровходу устройства, второй вход пятог элемента И соединен с входом кода операции устройства, первый, второй и третий входы и выход шестого элемента И подключены соответственно к выходу третьего элемента И, выходу дополнительного-триггера результата входу конца ветви устройства и первому установочному входу триггера результата, первый и второй входы и выход седьмого элемента И соединены соответственно с выходом четвертого элемента И, входом конца ветви устройства и входом сброса дополнительного триггера результата, введены дополнительно пять элементов И,два

элемента ИЛИ и элемент И-НЕ, первый, и второй входы и выход которого подключены соответственно к входу йачала ветви устройства, выходу четвёртого элемента И, синхровходу тригге5 ра анализа четности, инверсный выход которого соединен с информационным входом этого триггера, первый, второй и третий входы и выход восьмого элемента И подключены соответ10 ственно к прямому выходу триггера анализа четности, входу начала ветви устройства, выходу четвертого элемента И и синх{6овходу триггера ререзультата, первый и второй входы 5 и выход девятого элемента И соединены соответственно с выходом триггера запоминания результата, входом начала ветви устройства и информационным входом триггера результата, первый, второй и третий входы и выход,

0 десятого элемента И подключены соответственно к выходу третьего элемента И, входу начала ветви устройства, инверсному выходу триггера анализа четности и синхровходу 5 триггера запоминания результата, первый, второй и третий входы и выход одиннадцатого элемента И соединены соответственно с выходом третьего элемента И, входом начала ветви уст0 ройства, прямым выходом триггера анализа четности и синхровходом дополнительного триггера результата, первый и второй входы и выход первого элемента ИЛИ подключены соответ5 ственно к выходу триггера результата, выходу дополнительного триггера результата и информационному входу дополнительного триггера результата, первый и второй входы и выход двенадцатого элемента И соединены соответственно с инверсным выходом триггера анализа четн сти, выходом пятого элемента И и первым входом второго элемента или, второй вход которого подключен к входу начальной уста5 новки устройства, а выход второго

элемента ИЛИ соединен с входами сброса триггера анализа четности, триггера запоминания результата, дополнительного триггера результата и

0 вторым установочным входом триггера результата.

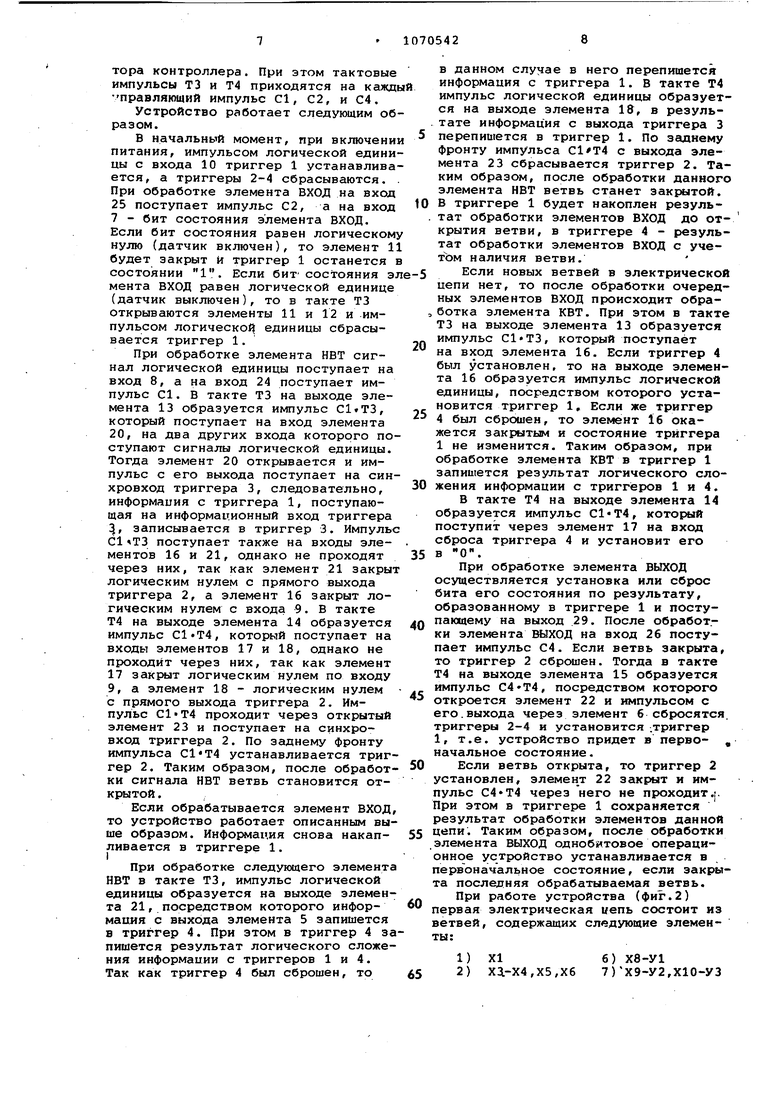

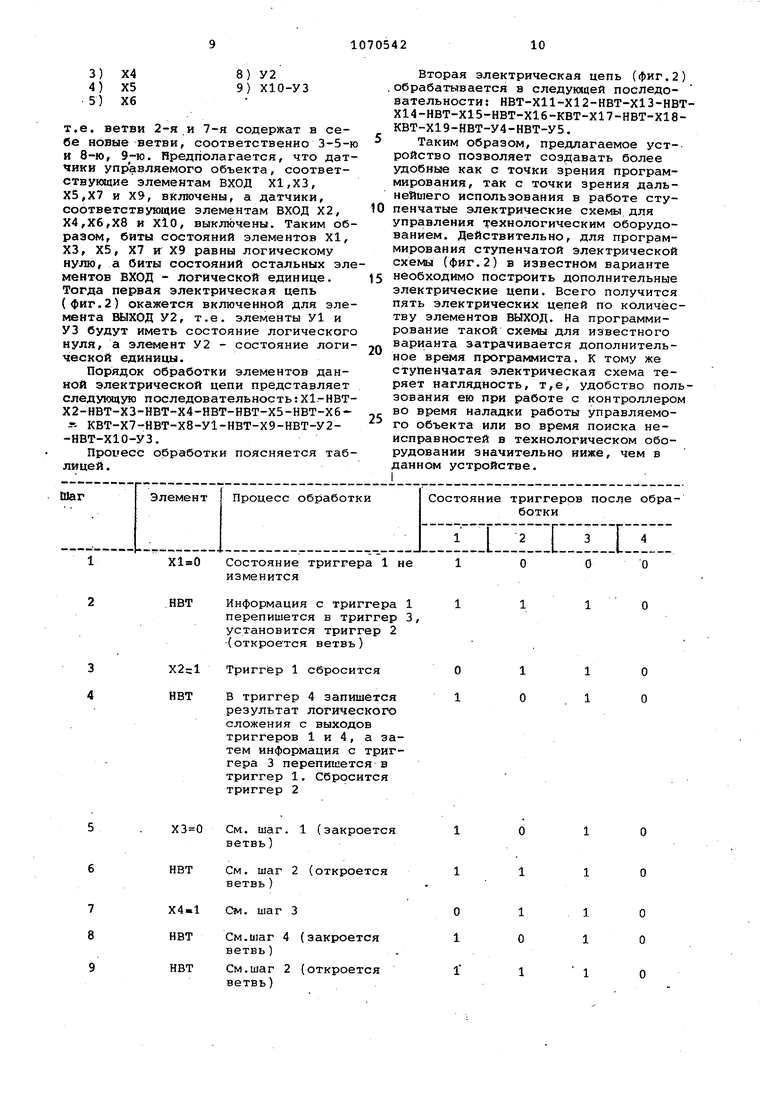

На фиг.1 представлена функциональная схема однобитового операционного устройства; на фиг.2 - ступенчатая

5 электрическая схема из двух цепей, которые может обрабатывать данное устройство.

Устройство содержит триггер 1 результата, триггер 2 анализа четности, триггер 3 запоминания резуль тата, дополнительный триггер 4 результата, элементы ИЛИ 5 и 6, и имеет вход 7 бита состояния, вход 8 начала ветви, вход 9 конца ветви, вход 10 начальной установки. Устрой5 ство также содержит элементы И 1122, элемент И-НЕ 23 и имеет трехраэрядные входы 24,25 и 26 кода операции, первый и втррой синхровходы 27 и 28, информационный выход 29.

Вход .сброса триггера 1 соединен с выходом элемента 11, первый вход которого, соединен с входом 7 устройства , а второй вход - с выходом элемента 12, первый вход которого соединен с входом 25 устройства, а второй вход - с первым входом элемента 13 и входом 27 устройства. Второй вход элемента 13 соединен с входом 24 устройства и первым входом элемента 14, второй вход которого соединен с входом 28 устройства и первым входом элемента 15, второй вход которого соединен с входом 26 устройства. Выход элемента 14 соединен с первым входом элемента 23 и первым входом элемента 18. Второй вход элемента 23 соединен с первыми входами элементов 19-21,, вторым входом элемента 18 и входом 8 устройства. Выход элемента 23 соединен с синхровходом триггера 2, прямой выход которого соединен с вторым iBходом элемента 21 и третьим входом элемента 18, а инверсный выход с информационным входом триггера 2-f первым входом элемента 22 и вторым входом элемента 20, третий вход которого соединен с третьим входом элемента 21, первым входом элемента 16 и выходом элемента 13. Выход элемента 20 соединен с синхровходом триггера 3, а выход элемента 21 с синхровходом триггера 4, прямой выход которого соединен с первым входом элемента 5 и вторым входом элемента 16, третий вход которого соединен с первым входом элемента 17 и входом 9 устройства. Выход элемента 15 соединен с вторым входом элемента 22, а выход элемента 14 - с вторым входом элемента 17. Выход элемента 17 соединен с первым входом сброса триггера 4, второй вход сброса которого соединен с входами сброса триггеров 1 и 2, первым входом установки триггера 1 и выходом элемента 6. Первый вход элемента 6 соединен с выходом элемента 22, а второй вход - с входом 10 устройства. Выход элемента 16 соединен с вторым входом установки триггера 1,-синхровход которого соединен с выходом элемента 18, а информационный вход с выходом элемента 19, второй вход которого соединен с прямым выходом триггера 3. Прямой выход триггера 1 соединен с выходом 29 устройства, информационным входом триггера 3 и вторым входом элемента 5, выход которого соединен с информационным входом триггера 4.

Однобитовое операционное устройство по входам и выходам соответствует устройству Г23. Отличие заключается в назначений триггеров 1-4, связях между ними и в функционировании самого устройства,.что составляет сущность изобретения.

Триггер 1 является триггером результата. В нем накапливается результат обработки элементов электрической цепи. Триггер 2, выполненный в виде триггера со счетным входом,, определяет, открыта или закрыта ветв электрической цепи, т.е. производит анализ элемента НАЧАЛО ВЕТВИ (НВТ) на его четность в электрической . При этом если при обработке электрической цепи появляется нечетный элемент НАЧАЛО ВЕТВИ, то ветвь открывается, а если четный, то ветвь закрывается. Триггер 3 является дополнительной ячейкой памяти для запоминания результата обработки, полученного в триггере 1, когда происходит открытие ветви. Триггер 4 является второй дополнительной ячейкой памяти-для накопления результата обработки, полученного в триггере 1 с учетом предыдущих результатов обработки ветвей, когда происходит закрытие ветви.

На вход 7 поступает бит состояния элемента ВХОД, который образуется в программируемом контроллере путем анализа состояния датчика,соответствующего данному элементу ВХОД, в зависимости от типа элемента ВХОД: нормально разомкнутый или нормально замкнутый контакт. Если анализируется нормально разомкнутый контакт и состояние датчика соответствует сигналу логической единицы (включено), то бит состояния элемента ВХОД будет иметь значение логического нуля. Если же анализируется нормально разомкнутый контакт и состояние датчика соответствует сигналу логического нуля (выключено), то бит состояния элемента ВХОД будет иметь значение логическое единицы и на вход 7 поступит сигнал логической единицы. На входы 8 и 9 поступают синалы соответственно НАЧАЛО ВЕТВИ (НВТ) и КОНЕЦ ВЕТВИ (КВТ), которые образуются в контроллере при считывании инструкции с элементом НВТ или КВТ. На вход 24 поступает импульс С1 логическая единица, формирующийся при считывании инструкции, например, с элементами НВТ и КВТ. На вход 25 поступает импульс С2 логической единицы, формирующийся при приеме бита состояния.элемента ВХОД На вход 26 поступает ийпульс С4 ло, гической единицы, образующийся при формировании результата однобитовой обработки после установки или очистки бита состояния элемента ВЫХОД. На входы-27 и 28 поступают тактовые импульсы ТЗ и Т4 с тактового генератора контроллера. При этом тактовые импульсы ТЗ и Т4 приходятся на кажды правляющий импульс С1, С2, и С4.

Устройство работает следующим образом.

В начальный момент, при включении питания, импульсом логической единицы с входа 10 триггер 1 устанавливается, а триггеры 2-4 сбрасываются. . При обработке элемента ВХОД на вход 25 поступает импульс С2, а на вход 7 - бит состояния элемента ВХОД. Если бит состояния равен логическому нулю (датчик включен), то элемент 11 будет закрыт И триггер 1 останется в состоянии 1. Если бит состояния эл мента ВХОД равен логической единице (датчик выключен), то в такте ТЗ открываются элементы 11 и 12 и импульсом логической единицы сбрасывается триггер 1.

При обработке элемента НЕТ сигнал логической единицы поступает на вход 8, а на вход 24 поступает импульс С1. В такте ТЗ на выходе элемента 13 образуется импульс С1«ТЗ, который поступает на вход элемента 20, на два других входа которого поступают сигналы логической единицы. Тогда элемент 20 открывается и им пульс с его выхода поступает на синхровход триггера 3, следовательно, информация с триггера 1, поступающая на информационный вход триггера 5, записывается в триггер 3. Импульс поступает также на входы элементов 16 и 21, однако не проходят через них, так как элемент 21 закрыт логическим нулем с прямого выхода триггера 2, а элемент 16 закрыт логическим нулем с входа 9. В такте Т4 на выходе элемента 14 образуется импульс С1«Т4, который поступает на входы элементов 17 и 18, однако не проходит через них, так как элемент 17 закрыт логическим нулем по входу 9, а элемент 18 - логическим нулем с прямого выхода триггера 2. Импульс С1«Т4 проходит через открытый элемент 23 и поступает на синхровход триггера 2. По заднему фронту импульса С1«Т4 устанавливается триггер 2. Таким образом, после обработки сигнала НВТ ветвь становится открытой .

Если обрабатывается элемент ВХОД, то устройство работает описанным выше образом. Информация снова накапливается в триггере 1.

При обработке следующего элемента НВТ в такте ТЗ, импульс логической единицы образуется на выходе элемента 21, посредством которого информация с выхода элемента 5 запишется в триггер 4. При этом в триггер 4 запишется результат логического сложения информации с триггеров 1 и 4. Так как триггер 4 был сброшен, то

в данном случае в него перепишется информация с триггера 1. В такте Т4 импульс логической единицы образуется на выходе элемента 18, в результате информация с выхода триггера 3 перепишется в триггер 1. По заднему фронту импульса с выхода элемента 23 сбрасывается триггер 2. Таким образом, после обработки данного элемента НВТ ветвь станет закрытой. В триггере 1 будет накоплен результат обработки элементов ВХОД до открытия ветви, в триггере 4 - результат обработки элементов ВХОД с учетЪм наличия ветви.

Если новых ветвей в электрической цепи нет, то после обработки очередных элементов ВХОД происходит обработка элемента КВТ. При этом в такте ТЗ на выходе элемента 13 образуется импульс С1«ТЗ, который поступает на вход элемента 16. Если триггер 4 был установлен, то на выходе элемента 16 образуется импульс логической единицы, посредством которого установится триггер 1, Если же триггер 4 был сброшен, то элемент 16 окажется закрытым и состояние триггера 1 не изменится. Таким образом, при обработке элемента КВТ в триггер 1 запишется результат логического сложения информации с триггеров 1 и 4.

В такте Т4 на выходе элемента 14 образуется импульс С1«Т4, который поступит через элемент 17 на вход сброса триггера 4 и установит его в О.

При обработке элемента ВЫХОД осуществляется установка или сброс бита его состояния по результату, образованному в триггере 1 и поступающему на выход ,29. После обработ.ки элемента ВЫХОД на вход 26 поступает импульс С4. Если ветвь закрыта, то триггер 2 сброшен. Тогда в такте Т4 на выходе элемента 15 образуется импульс , посредством которого откроется элемент 22 и импульсом с его.выхода через элемент 6 сбросятся триггеры 2-4 и установится -.триггер 1, т.е. устройство придет в первоначальное состояние.

Если ветвь открыта, то триггер 2 установлен, элемент 22 закрыт и импульс С4Т4 через него не проходит.i. При этом в триггере 1 сохраняется результат обработки элементов данной цепи. Таким образом, после обработки элемента ВЫХОД однобитовое операционное устройство устанавливается в первЪначальное состояние, если закрыта последняя обрабатываемая ветвь.

При работе устройства (фиг.2) первая электрическая цепь состоит из ветвей, содержащих следующие элементы:

6) Х8-У1

1)XI 7)Х9-У2,Х10-УЗ

2)ХД.-Х4,Х5,Х6

8)У2

Х4 Х5

9)Х10-УЗ Х6

Т.е. ветви 2-я и 7-я содержат в себе новые ветви, соответственно 3-5-ю и 8-ю, 9-ю. Предполагается, что датчики управляемого объекта, соответствующие элементам ВХОД Х1,ХЗ, Х5,Х7 и Х9, включены, а датчики, соответствующие элементам ВХОД Х2, Х4,Хб,Х8 и Х10, выключены. Таким образом, биты состояний элементов Х1, ХЗ, Х5, Х7 к Х9 равны логическому нулю, а биты состояний остальных элементов ВХОД - логической единице. Тогда первая электрическая цепь (фиг.2) окажется включенной для элемента КЛХОД У2, т.е. элементы У1 и УЗ будут иметь состояние логического нуля, а эланент У2 - состояние логической единицы.

Порядок обработки элементов данной электрической цепи представляет следующую последовательность:Х1-HBTX2-HBT-XЗ-HBT-X4-HBT-HBT-X5-HBT-X6л КВТ-Х7-НВТ-Х8-У1-НВТ-Х9-НВТ-У2-НВТ-Х10-УЗ.

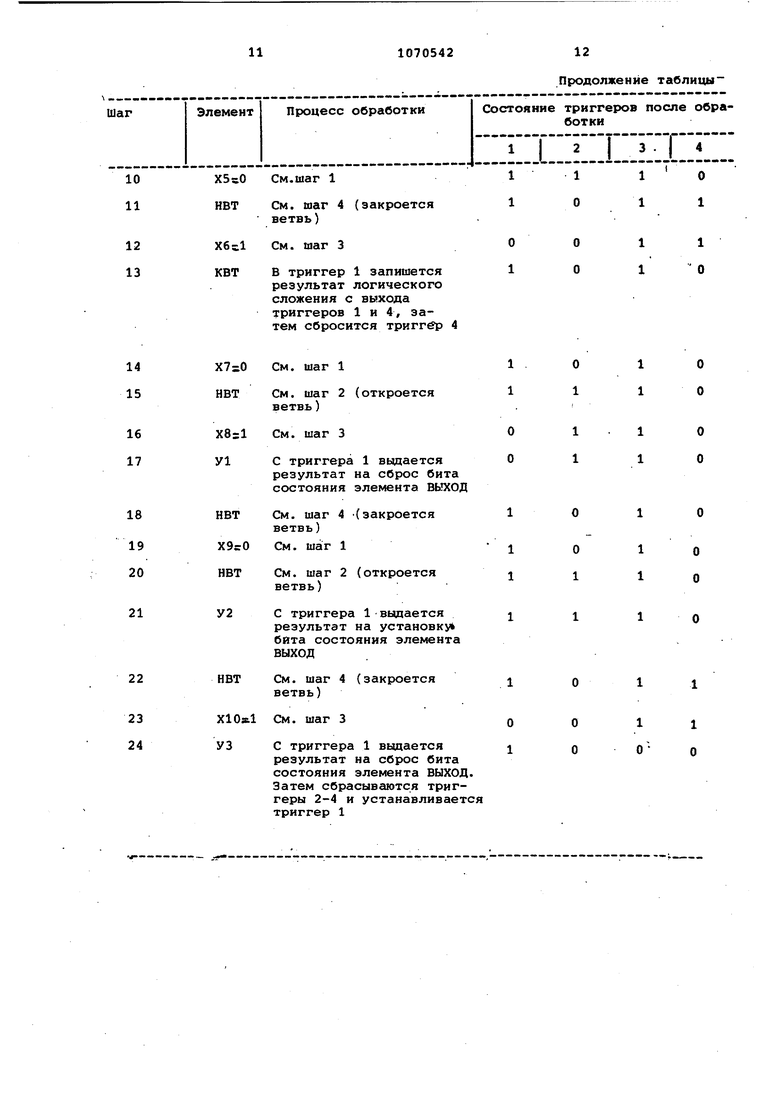

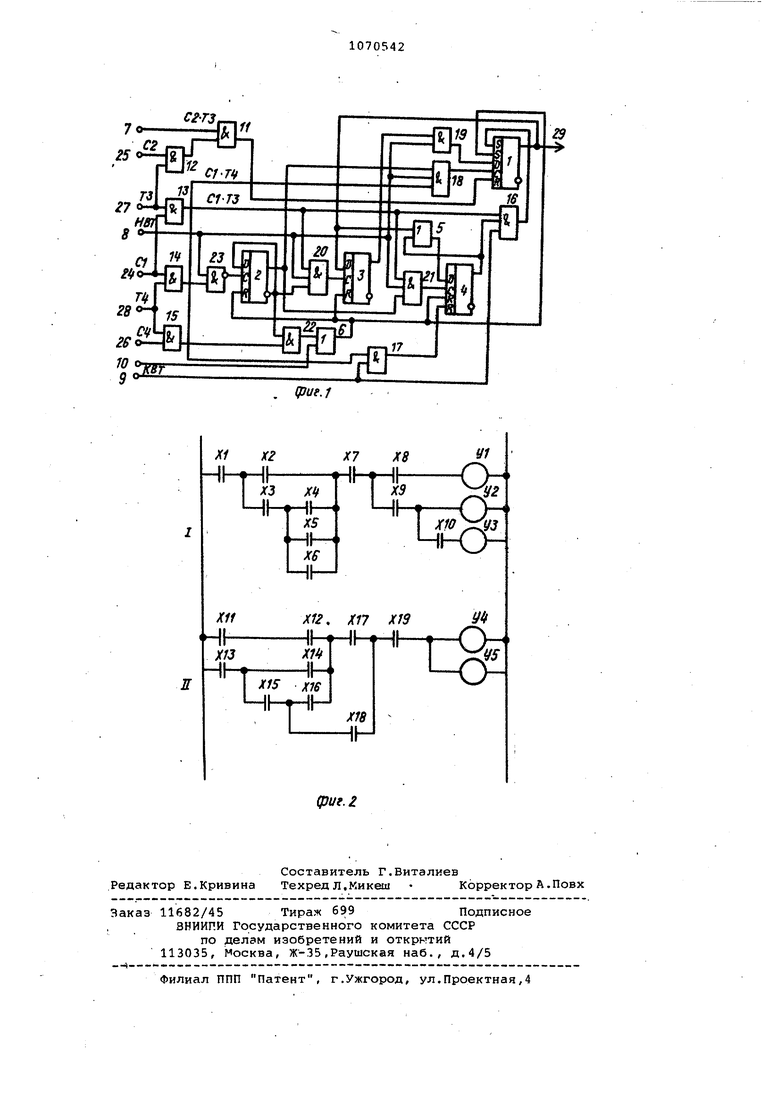

Проиесс обработки поясняется таблицей .

XleO Состояние триггера 1 не изменится

,НВТ Информация с триггера 1 перепишется в триггер 3, установится триггер 2 (откроется ветвь)

Х2с1 Триггер 1 сбросится

НВТ В триггер 4 запишется результат логического сложения с выходов триггеров 1 и 4, а затем информация с триггера 3 перепишется в триггер 1. Сбросится триггер 2

См. шаг. 1 (закроется ветвь)

НВТ См. шаг 2 (откроется ветвь )

Х4«1 См. шаг 3

НВТ См.шаг 4 (закроется ветвь)

НВТ См.шаг 2 (откроется ветвь)

Вторая электрическая цепь (фиг.2) обрабатывается в следующей последовательности: НВТ-Х11-Х12-НВТ-Х13-НВТХ14-НВТ-Х15-НВТ-Х16-КВТ-Х17-НВТ-Х18КВТ-Х19-НВТ-У4-НВТ-У5.

Таким образом, предлагаемое устройство позволяет создавать более удобные как с точки зрения программирования, так с точки зрения дальнейшего использования в работе ступенчатые электрические схемы для управления технологическим оборудованием. Действительно, для программирования ступенчатой электрической схемы (фиг.2) в известном варианте 5 необходимо построить дополнительные электрические цепи. Всего получится пять электрических цепей по количеству элементов ВЫХОД. На программирование такой схемы для известного варианта затрачивается дополнительное время программиста. К тому же ступенчатая электрическая схема теряет наглядность, т,е, удобство пользования ею при работе с контроллером во время наладки работы управляемого объекта или во время поиска неисправностей в технологическом оборудовании значительно ниже, чем в данном устройстве. I

О

1

О 1

О О

О

О

1

1 о

О 1

ветвь)

У2 С триггера 1 выдается результат на установку бита состояния элемента ВЫХОД

НВТ См. шаг 4 (закроется ветвь)

См. шаг 3

УЗ С триггера 1 вьщается

результат на сброс бита состояния элемента ВЫХОД. Затем сбрасываются триггеры 2-4 и устанавливается триггер 1

Продолжение таблицы

О О

1 О

О 1

1 О

сг-тз

Ipue.j

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3810118, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3942158, кл.340-172.5, опублик | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| . | |||

Авторы

Даты

1984-01-30—Публикация

1982-12-15—Подача