3

Изобретение относится к цифровой вычислительной технике и может быть использовано для обмена между процессорными элементами в мультипроцессорных системах.

Цель изобретения - повышение производительности вычислительной системы за счет обеспечения одновременной работы каждого канала в режимах приема и передачи.

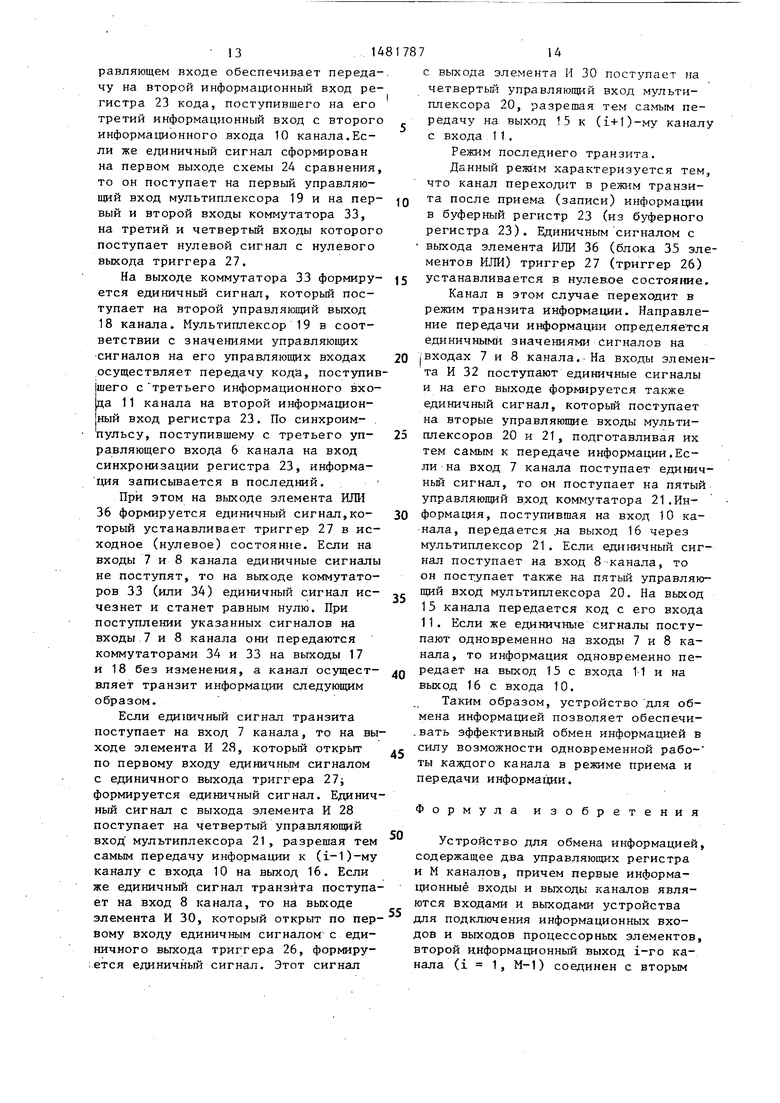

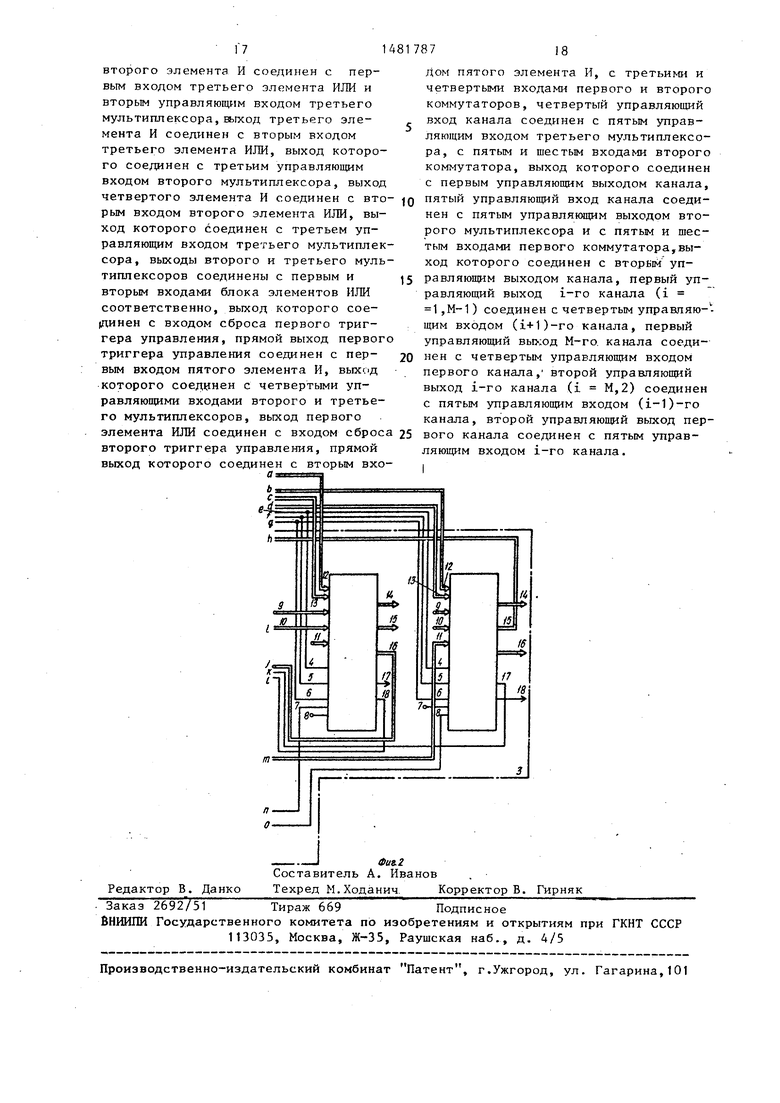

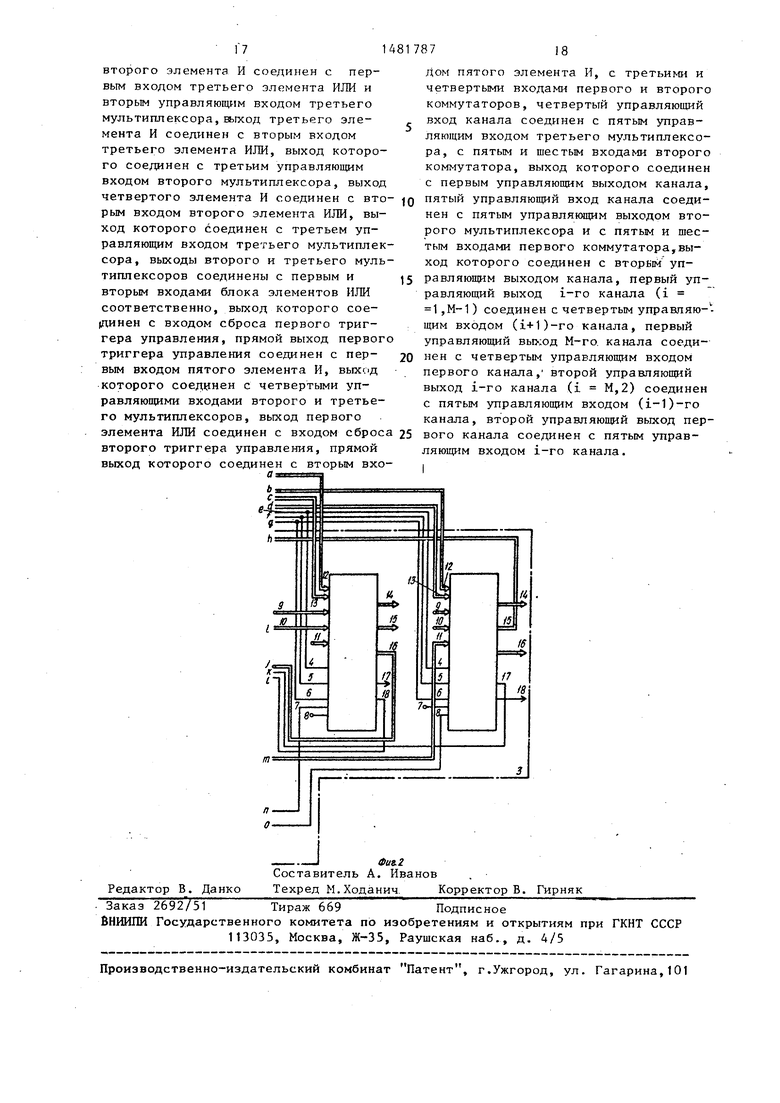

На фиг.1 и 2 представлена функциональная схема устройства для обмена информацией.

Устройство для обмена информацией содержит первый и второй управляющие регистры 1 и 2 соответственно, об- менник 3 информацией, состоящий из М каналов, первый - пятый управляющие входы 4-8 соответственно каналов, первый - третий информационные входы 9-11 соответственно каналов, вход 12 задания режима обмена,вход 13 разрешения записи информации, первый - третий информационные выходы 14-16 соответственно каналов,первый и второй выходы 17 и 18 соответственно, кроме того, каждый канал содержит первый - четвертьй мультиплексоры 19-22 соответственно, буферный регистр 23, схему 24 сравнения адресов, схему 25 формирования собственного адреса канала, первый и второй триггеры 26 и 27 управления соответственно, первый - пятый элементы И 28-32 соответственно,первый и второй коммутаторы 33 и 34 соответственно, блок 35 элементов ИЛИ, первый - третий элементы ИЛИ 36-38.

Регистр 1 предназначен для записи и хранения кодов адресов каналов передатчиков (кодов адресов каналов, которые являются источниками информации), и кодов адресов каналов приемников (кодов адресов каналов), в которые информация должна быть пе редана.

Регистр 2 предназначен для записи и хранения кодов адресов каналов приемников (кодов адресов тех каналов, в которые информация должна быть записана) и кодов адресов каналов передатчиков (кодов адресов тех каналов, из которых информация передается) .

Обменник 3 информацией состоит из

М каналов и предназначен для осуществления связи между процессорными элементами вычислительной системы.

Первый управляющий вход 4 1-го канала предназначен для управления

записью информации, поступающей из 1-го процессорного элемента в 1-й канал.

Второй управляющий вход 5 1-го канала предназначен для управления

записью информации, поступающей из выбранного канала.

Третий управляющий вход 6 1-го канала предназначен для передачи в канал сигналов синхронизации записи

информации.

Четвертый управляющий вход 7 1-го канала предназначен для трансляции сигналов управления переводом каналов в режим передачи информации от 1-го канала к (1-1)-му каналу.

Пятый управляющий вход 8 1-го канала предназначен для трансляции сигналов управления переводом кана

лов в режим передачи информации от

1-го канала к Ц+1)-му каналу.

Первый информационный вход 9 1-го канала предназначен для передачи ийформации и ч i-ro процессорного элемента .

Второй информационный вход 10 1-г канала предназначен для передачи информации из (i+1)-ro канала.

Третий информационный вход 11 1-г канала предназна чен для передачи информации 13 (i-1)-ro канала.

Четвертый информационный вход 12 1-го канала предназначен для передачи информации из первого управляющего регистра 1.

Пятый информационный вход 13 1-го канала предназначен для передачи информации из второго управляющего регистра 2.

Первый информационный выход 14 1-го канала предназначен для передачи информации в i-й процессорный элемент.

Второй информационный выход 15 1-го канала предназначен для передачи информации в (1+1)-й канал.

Третий информационный выход 16 1-го канала предназначен для передачи информации в (1-1)-й канал.

Первый управляющий выход 17 1-го канала предназначен для передачи сигналов перевода (i+1)-ro канала в режим транзита информации в i-й канал.

Второй управляющий выход 18 1-го канала предназначен для передачи сигнала перевода (i-1)-ro канала в режим транзита информации в i-й канал

Первый мультиплексор 19 1-го канала предназначен для передачи соответствующей информации, поступающей из (i+1)-ro и из (i-1)-ro каналов в регистр 23.

Bt-орой мультиплексор 20 1-го канала предназначен для передачи соответствующей информации в (1+1)-й канал.

Третий мультиплексор 21 1-го канала предназначен для передачи соответствующей информации в (1-1)-и канал.

Четвертый мультиплексор 22 i-ro канала предназначен для передачи информации, поступающей из первого и второго управляющих регистров 1 и 2 соответственно в схему 24 сравнения.

Буферный регистр 23 1-го канала предназначен для хранения информации, поступающей в i-й канал.

Схема 24 1-го канала сраврения адресов предназначена для сравнения кодов адресов каналов приемников и

0

5

0

передатчиков информации, участвующих в сеансе обмена с i-м каналом, и формирования сигналов управления выбором направлений приема или передачи информации.

Схема 25 формирования собственного адреса 1-го канала предназначена для формирования кода собственного адреса 1-го канала.

Первый триггер 26 управления 1-го канала предназначен для его перево- .да в режим передачи информации.

Второй триггер 27 управления 1-го канала предназначен для его перевода в режим приема информации.

Элемент И 28 1-го канала предназначен для формирования сигнала управления транзитом информации из (i+1)-го канала в (1-1)-й канал.

Элемент И 29 1-го канала предназначен для формирования сигналов управления передачей информации из регистра 23 в (1+1)-й канал и управле- 5 ния транзитом информации из (i+1)-ro в ()-й канал.

Элемент И 30 1-го канала предназначен для формирования сигнала управления транзитом из (i-l)-ro канала в (1+1)-й канал.

Элемент И 31 1-го к анала предназначен для формирования сигналов управления передачей информации из регистра 23 в (1-1)-й канал и управления транзитом информации из (i-1)- го в (i+O-й канал.

Элемент И 32 1-го канала предназначен для формирования сигнала транзита.

Блок 35 элементов ИЛИ 1-го канала предназначен для формирования сигнала перевода второго триггера 27 в исходное состояние после выдачи информации в соответствующие каналы.

Элемент ИЛИ 36 1-го канала пред- . назначен для формирования сигнала перевода первого триггера 26 в исходное состояние.

Элемент ИЛИ 37 предназначен для передачи сигналов управления транзитом информации из (i-1)-ro в (i+1)-й канал.

Элемент ИЛИ 38 предназначен для передачи сигналов управления транзитом информации из (i+1)-ro в (Ј-1)-й канал.

При подаче питания (цепи включения питания условно не показаны) на устройства для обмена информацией

0

0

5

0

5

регистры 1 и 2, триггеры 2& и 27 каналов, а также их буферные регистры 23 устанавливаются в нулевое состояние (цепи установки элементов памяти в нуль на фиг.1 не показаны).

В регистры 1 и 2 записывается из устройства управления информация об активных передатчиках и соответствующих им активных приемниках,участвующих в сеансе обмена.

При записи информации из 1-го процессорного элемента в канал соответствующий код поступает на первый информационный вход 9 1-го канала и далее на соответствующий информа- ционный вход буферного регистра 23. На разрешающий вход регистра 23 поступает единичный сигнал с первого управляющего входа 4 канала. По заднему фронту синхроимпульса, поступившего на третий управляющий вход 6 канала, информация записывается в регистр 23.

При считывании из канала в соответствующий процессорный элемент информация поступает на первый информационный выход 14 с входа регистра 23.

Кроме рассмотренных режимов функционирования каждый канал может функционировать в режиме собственно транзита, а также в режиме активного передатчика, активного приемника и в режиме последующего транзита.Ниже приводятся кратко алгоритмы работы устройства во всех перечисленных режимах.

Режим транзита характеризуется тем, что канал участвует в передаче информации, циркулирующей в обменни- ке 3, путем прямой ее трансляции с второго информационного входа 10 на третий информационный выход 16 либо с информационного входа 11 на второй информационный выход 15 канала.

Для реализации такого режима работы триггеры 26 и 27 канала устанавливаются в нулевое состояние.

На выходе элемента И 32 формируется единичный сигнал, поступающий на управляющие входы мультиплексоров 21 и 20 с целью разрешения передачи информации на соответствующий выход канала.

Направление передачи информации определяется единичным значением сигналов, поступающих на входы 7 и 8 канала. Единичный сигнал на входе

0

5

7канала свидетельствует о необходимости передачи информации на выход 16 канала. Единичный сигнал на входе

8канала свидетельствует о необходимости передачи информации на выход 15 канала. В этом случае при наличие на входах 7 и 8 единичных сигналов канал может осуществлять одновременно передачу информации в направлениях (д-1)-го и (i+O-ro каналов.

Режим последующего транзита в канале организуется следующим образом.

После записи (или считывания) информации в буферный регистр 23 (из буферного регистра 23) в режиме активного приемника (активного передатчика) происходит установка триггера 27(26) в исходное (нулевое) состояние. При этом элемент И 32 канала формирует сигнал транзита. Работа канала в дальнейшем не отличается от работы канала в режиме транзита информации .

Режим активного передатчика.

Этот режим характеризуется тем, что при поступлении информации на четвертый информационный вход 12 канала значение младшего разряда кода равно единице. Триггер 26 устанавливается в единичное состояние. На схему 24 сравнения кодов адресов поступает код соответствующего канала приемника. Сравнение кодов адресов передатчика и приемника позволяет определить направление передачи информации

Если существует отношение между кодом адреса канала приемника и кодом адреса канала передатчика, то информация-с выхода регистра 23 поступает через мультиплексор 21 на выход 16 канала.

Если же существует отношение между указанными кодами, то информация с выхода регистра 23 поступает через мультиплексор 20 на второй информационный выход 15 канала.

Независимо от направления выдачи информации в канале происходит уста- 0 новка триггера 26 в исходное нулевое состояние. После этого канал переходит в режим работы последующего транзита. Работа канала повторяется.

При работе 1-го канала в режиме 5 активного приемника младший разряд кода, поступающего на пятый информационный вход 13 канала, имеет единичное значение. В результате этого

0

5

0

5

триггер 27 переходит в единичное состояние и единичным сигналом с единичного выхода переводит канал в режим приема информации. При этом информация в канал может поступать как на третий информационный вход 11, так и на второй информационный вход 10. Выбор направления приема информации осуществляется схемой 24 сравнения адресов. На его входы поступают коды адреса канала передатчика и собственного адреса. При формировании единичного сигнала на выходе информация с входа 11 канала поступает через мультиплексор 19 на второй информационный вход регистра 23.

В противном случае в регистр 23 записывается информация, поступившая с входа 10 канала.

При этом выдается сигнал транзита информации на выход 18 в первом случае и на выход 17 во втором случае.

После записи информации в регистр 23 происходит установка триггера 27 в нулевое состояние. Канал переходит в режим последующего транзита. В зависимости от значений сигналов, поступающих на входы 7 и 8 канала, на его выходах 17 и 18 также формируются единичные сигналы.

Работа канала продолжается по .описанному алгоритму.

,

Устройство для обмена информацией работает следующим образом.

В исходном состоянии все элементы памяти .находятся в нулевом состоянии Цепи установки в нуль и цепи питания на фиг.1 условно не показаны. Протокол обмена информацией между каналами, а также между процессорными элементами и соответствующими каналами задается устройством управления путем записи в регистры 1 и 2 соответствующей информации, а также путем подачи на входы 4-6 каналов управляющих сигналов.

Рассмотрим последовательно функционирование устройства для обмена ин фармацией в режимах записи информации из процессорного элемента (в процессорные элементы), активного передатчика, активного приемника, транзита информации и в режиме последующего транзита информации.

Режим записи информации из процессорного элемента.

10

15

20

25

30

35

40

45

50

55

На вход 4 канала поступает единичный сигнал, который поступает на соответствующий разрешающий вход регистра 23. На первый информационный вход 9 канала поступает код с выхода соответствующего процессорного элемента. По заднему фронту синхроимпульса, поступающего на третий управляющий вход 6 канала, информация записывается в регистр 23.

Режим записи информации в про- цессорный элемент.

Данный режим характеризуется отсутствием на входе канала как управляющих, так и информационных сигналов. Код, записанный з регистр 23, выдается непрерывно на первый информационный выход 14 канала.

Режим активного передатчика.

Этот режим характеризуется тем, что в регистр 1 поступает код, который содержит информацию об адресах каналов передатчиков и адресах каналов приемников.

Признаком активности канала в режиме передачи информации служит единичное значение младшего разряда кода, поступающего на четвертый информационный вход 12 канала. В остальных разрядах кода содержится код адреса канала приемника. Единичным сигналом младшего разряда кода с входа 12 триггер 26 переводится в единичное состояние. На его единичном выходе появляется единичный сигнал,который поступает на первые входы элементов И 29 и 31, а также на первый управляющий вход мультиплексора 22.

Информация с входа 12 канала rfoc- /гупает через мультиплексор 22 на первый вход схемы 24 сравнения. На ее второй вход поступает код собственного адреса канала. В зависимости от результата сравнения формируется единичный сигнал на первом или втором ее выходах. Единичный сигнал на первом выходе схемы 24 сравнения появляется в том случае, если код адреса приемника меньше кода адреса ка- лала, передающего информацию. Единичный сигнал на втором выходе схемы 24 сравнения адресов появляется в,том случае, если код адреса канала Приемника информации больше кода .адреса канала передатчика информации. При появлении единичного сигнала на втором выходе схемы 24 он поступает на управляющие входы мультиплексоров

19 и 21, а также на второй вход коммутатора 34, на третий вход которого поступает единичный сигнал с нулевого выхода триггера 27, и на выходе коммутатора 34 формируется единичный сигнал который поступает на первый управляющий выход 17 канала. По единичному сигналу, -поступившему на первый управляющий вход мультиплексора 21, последний осуществляет передачу на выход кода, поступившего на его второй информационный вход с выхода буферного регистра 23. Информация с выхода мультиплексора 21 поступает на первый информационный вход блока 35 элементов ИЛИ и на третий информационный выход 16 канала.

На выходе блока 35 элементов ИЛИ формируется единичный сигнал, который поступает на вход установки в нуль триггера 26 и переводит его в нулевое состояние. В результате этого канал переходит в исходное состояние.

В том случае, если единичный сиг- нал сформирован на первом выходе схемы 24, он поступает на соответствующие управляющие входы мультиплексоров 20 и 19 и на первый и второй входы коммутатора 33. На третий вход коммутатора 33 поступает единичный сигнал с нулевого выхода триггера 27. На выходе коммутатора 33 формируется единичный сигнал, который поступает на выход 18 канала. Единичный сигнал, поступивший на первый управляющий вход мультиплексора 20, разрешает передачу на выход 15 канала информации информации, поступившей на его второй информационный вход с выхода буферно- го регистра 23.

В том случае, если код адреса канала приемника информации меньше кода адреса канала, передающего инфор- мацию, последний канал может осуществлять одновременно и передачу информации в режиме транзита в от (i-H)-r по М-й каналы. В этом случае единичный сигнал с единичного выхода триггера 26 поступает на первые входы элементов И 29 и 31 и открывает их. Если единичный сигнал поступает на вход 7 канала, то на выходе элемента И 31 формируется единичный сигнал которьй поступает на четвертый управляющий вход мультиплексора 20. В результате этого на выход 15 канала будет передан код с входа 11 канала

0 j 0

,

0

5

одновременно с передачей на выход 16 информации, записанной в регистр 23.

Если код адреса канала приемника информации больше кода адреса канала, передающего информацию,то последний канал может осуществлять одновременно и передачу информации в от (i-1)-ro по 1-й каналы.

В этом случае единичный сигнал с единичного входа триггера 26 поступает на первые входы элементов И 29 и 31 и открывает их.

Если единичный сигнал поступает на вход 8 канала, то на выходе элемента И 29 формируется единичный сигнал, который поступает на третий управляющий вход мультиплексора 21 и на четвертый управляющий вход мультиплексора 20. В результате этого одновременно на выходы 16 и 15 канала будет передана соответствующая информация.

Режим активного приемника канала.

В этом случае единичным значением младшего разряда кода, поступающего на пятый информационный вход 13 канала, триггер 27 переходит в единичное состояние. Единичный сигнал с единичного выхода триггера 27 поступает на второй управляющий вход мультиплексора 22 и обеспечивает тем самым передачу на вход схемы 24 кода адреса соответствующего канала передатчика .

Единичный сигнал с выхода триггера 27 поступает на третий управляющий вход мультиплексора (Обеспечивая тем самым передачу либо по его первому, либо по второму информационному входу.

На второй вход схемы 24 поступает код адреса собственного канала и сравнивается с кодом адреса канала передатчика. Если код адреса канала передатчика больше кода адреса канала, то на втором выходе схемы 24 появляется единичный сигнал, который поступает на управляющий вход мультиплексора 19 и на первый и второй входы коммутатора 34, на третий вход которого поступает единичный сигнал с нулевого выхода триггера 27. На

выходе коммутатора 34 формируется, единичный сигнал, который поступает .на первый управляющий выход 17 канала. Мультиплексор 19 в соответствии с единичным сигналом на втором уп13

равляющем входе обеспечивает передачу на второй информационный вход регистра 23 кода, поступившего на его третий информационный вход с второго информационного входа 10 канала.Если же единичный сигнал сформирован на первом выходе схемы 24 сравнения, то он поступает на первый управляющий вход мультиплексора 19 и на первый и второй входы коммутатора 33, на третий и четвертый входы которого поступает нулевой сигнал с нулевого выхода триггера 27.

На выходе коммутатора 33 формируется единичный сигнал, который поступает на второй управляющий выход 18 канала. Мультиплексор 19 в соответствии с значениями управляющих сигналов на его управляющих входах осуществляет передачу кода, поступившего с третьего информационного входа 11 канала на второй информационный вход регистра 23. По синхроим- пульсу, поступившему с третьего управляющего входа 6 канала на вход синхронизации регистра 23, информация записывается в последний.

При этом на выходе элемента ИЛИ 36 формируется единичный сигнал,который устанавливает триггер 27 в исходное (нулевое) состояние. Если на входы 7 и 8 канала единичные сигналы не поступят, то на выходе коммутаторов 33 (или 34) единичный сигнал исчезнет и станет равным нулю. При поступлении указанных сигналов на входы 7 и 8 канала они передаются коммутаторами 34 и 33 на выходы 17 и 18 без изменения, а канал осуществляет транзит информации следующим образом.

Если единичный сигнал транзита поступает на вход 7 канала, то на выходе элемента И 28, который открыт по первому входу единичным сигналом с единичного выхода триггера 27; формируется единичный сигнал. Единичный сигнал с выхода элемента И 28 поступает на четвертый управляющий вход мультиплексора 21, разрешая тем самым передачу информации к (1-1)-му каналу с входа 10 на выход 16. Если же единичный сигнал транзита поступает на вход 8 канала, то на выходе элемента И 30, который открыт по первому входу единичным сигналом с единичного выхода триггера 26, формируется единичный сигнал. Этот сигнал

178714

с выхода элемента И 30 поступает на четвертый управляющий вход мультиплексора 20, разрешая тем самым пе- редачу на выход 15 к (1+1)-му каналу с входа 11.

Режим последнего транзита. Данный режим характеризуется тем, что канал переходит в режим транзиjg та после приема (записи) информации в буферный регистр 23 (из буферного регистра 23). Единичным сигналом с - выхода элемента ИЛИ 36 (блока 35 элементов ИЛИ) триггер 27 (триггер 26)

15 устанавливается в нулевое состояние.

Канал в этом случае переходит в режим транзита информации. Направление передачи информации определяется единичными значениями сигналов на

20 ,входах 7 и 8 канала. На входы элемента И 32 поступают единичные сигналы и на его выходе формируется также единичный сигнал, который поступает на вторые управляющие входы мульти25 плексоров 20 и 21, подготавливая их тем самым к передаче информации.Если на вход 7 канала поступает единичный сигнал, то он поступает на пятый управляющий вход коммутатора 21.Ин30 формация, поступившая на вход 10 канала, передается на выход 16 через мультиплексор 21. Если единичный сигнал поступает на вход 8 канала, то он поступает также на пятый управляющий вход мультиплексора 20. На выход 15 канала передается код с его входа 11. Если же единичные сигналы поступают одновременно на входы 7 и 8 канала, то информация одновременно пе40 редает на выход 15 с входа 11 и на выход 16 с входа 10.

Таким образом, устройство для обмена информацией позволяет обеспечивать эффективный обмен информацией в , силу возможности одновременной рабо- ты каждого канала в режиме приема и передачи информации.

35

Формула изобретения

Устройство для обмена информацией, содержащее два управляющих регистра и М каналов, причем первые информационные входы и выходы каналов являются входами и выходами устройства для подключения информационных входов и выходов процессорных элементов, второй информационный выход 1-го канала (, M-1) соединен с вторым

15148

информационным входом (i+1)-ro канала, р.торой информационный выход М-го канала соединен с вторым информационным входом первого канала, третий информационный выход 1-го канала (i М,2) соединен с третьим информационным входом (i-1)-ro канала,третий информационный выход первого канала соединен с третьим информационным входом М-го канала, вход записи информации управления устройства соединен с входами записи первого и второго управляющих регистров, вход за

16

равляюшими входами буферного регистра и входом его синхронизации, о т- личающееся тем, что, с целью повышения производительности вычислительной системы за счет обеспечения одновременной работы каждого канала в режимах приема и передачи, з каждый канал дополнительно введены четвертый мультиплексор, блок элементов ИЛИ, схема сравнения адресов, блок формирования собственного адреса канала, первый и второй триггеры управления, первый и второй

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для программного управления технологическими процессами | 1990 |

|

SU1784940A1 |

| Многоканальное устройство для обмена управляющей информацией в вычислительной системе | 1988 |

|

SU1566362A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Модуль матричного коммутатора | 1990 |

|

SU1793436A2 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Модуль однородной вычислительной структуры | 1987 |

|

SU1495809A1 |

| Многоканальное устройство для обмена информацией | 1988 |

|

SU1564637A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для обмена между процессорными элементами в мультипроцессорных системах. Целью изобретения является повышение производительности вычислительной системы за счет обеспечения одновременной работы каждого канала в режимах приема и передачи. Устройство для обмена информацией содержит первый и второй управляющие регистры 1 и 2 соответственно, обменник 3 информацией, состоящей из каналов с их связями, кроме того, каждый канал содержит четыре мультиплексора 19÷22 соответственно, буферный регистр 23, схему 24 сравнения, схему 25 формирования собственного адреса, первый 26 и второй 27 управляющие триггеры, пять элементов И 28÷32, первый 33 и второй 34 коммутаторы, блок 35 элементов ИЛИ, три элемента ИЛИ 36÷38 соответственно. 2 ил.

дания режима обмена устройства соеди- г коммутаторы, пять элементов И и три

20

25

30

35

нен с информационным входом первого управляющего регистра, выходы соответствующих групп разрядов которого соединены соответственно с четвертыми информационными входами с первого по М-й каналов, вход записи разрешения информации устройства соединен с информационным входом второго управляющего регистра, выходы соответствующих групп разрядов которого соединены соответственно с пятыми информационными входами с первого по М-й каналов, вход задания направления обмена устройства соединен с первыми управляющими входами всех каналов, вход разрешения записи устройства соединен с вторыми управляющими входами всех каналов, вход синхронизации устройства соединен с третьими управляющими входами всех каналов, каждый из которых содержит три мультиплексора и буферный регистр информации, причем первый информационный вход канала соединен с первым информационным входом буферного регистра, второй информационный вход канала соединен с первыми информационными входами первого и второго мультиплексоров, третий информационный вход канала соединен с вторым информационным входом первого мультиплексора и первым информационным входом третьего мультиплексора, выход первого мультиплексора соединен с вторым информационным входом буферного регистра, выход которого соединен с первым информационным выходом канала и с вторыми информационными входами второго и третьего мультиплексоров,выходы которых соединены соответственно с вторым и третьим информационными выхо- 55 дами канала, первый, второй и третий входы управления канала соединены соответственно с первым и вторым уп40

45

50

элемента ИЛИ, причем в каждом канале четвертый и пятый информационные входы канала соединены соответственно с первым и вторым информационными входами четвертого мультиплексора, выход которого соединен с первым входом схемы сравнения адресов, выход блока формирования собственного адреса канала соединен с. вторым входом схемы сравнения адресов, первый выход которой соединен с первыми управляющими входами первого и второго мультиплексоров и первым и вторым входами первого коммутатора, второй выход схемы сравнения адресов соединен с первым и вторым управляющими входами первого и третьего мультиплексоров, первым и вторым входами второго коммутатора, младшие разряды четвертого и пятого

-входов канала соединены с входами установки первого и второго триггеров управления соответственно, единичный выход первого триггера управления соединен с первым управляющим входом четвертого мультиплексора и первыми входами первого и второго элементов И, единичный выход второго триггера управления соединен с первыми входами третьего и четвертого элементов И, вторым управляющим входом четвертого мультиплексора и третьим управляющим входом первого мультиплексора, выход которого соеди нен с входами первого элемента ИЛИ, четвертый управляющий вход канала со динен с вторыми входами второго и четвертого элементов И, пятый управляющий вход канала соединен с вторыми входами первого и третьего элемен тов И, выход первого элемента И сое.динен с первым входом второго элемента ИЛИ и вторым управляющим входом второго мультиплексора, выход

0

5

0

5

5

0

5

0

элемента ИЛИ, причем в каждом канале четвертый и пятый информационные входы канала соединены соответственно с первым и вторым информационными входами четвертого мультиплексора, выход которого соединен с первым входом схемы сравнения адресов, выход блока формирования собственного адреса канала соединен с. вторым входом схемы сравнения адресов, первый выход которой соединен с первыми управляющими входами первого и второго мультиплексоров и первым и вторым входами первого коммутатора, второй выход схемы сравнения адресов соединен с первым и вторым управляющими входами первого и третьего мультиплексоров, первым и вторым входами второго коммутатора, младшие разряды четвертого и пятого

-входов канала соединены с входами установки первого и второго триггеров управления соответственно, единичный выход первого триггера управления соединен с первым управляющим входом четвертого мультиплексора и первыми входами первого и второго элементов И, единичный выход второго триггера управления соединен с первыми входами третьего и четвертого элементов И, вторым управляющим входом четвертого мультиплексора и третьим управляющим входом первого мультиплексора, выход которого соединен с входами первого элемента ИЛИ, четвертый управляющий вход канала соединен с вторыми входами второго и четвертого элементов И, пятый управляющий вход канала соединен с вторыми входами первого и третьего элементов И, выход первого элемента И сое.динен с первым входом второго элемента ИЛИ и вторым управляющим входом второго мультиплексора, выход

второго элемента И соединен с первым входом третьего элемента ИЛИ и вторым управляющим входом третьего мультиплексора,выход третьего элемента И соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с третьим управляющим входом второго мультиплексора, выход четвертого элемента И соединен с вторым входом второго элемента ИЛИ, выход которого соединен с третьем управляющим входом третьего мультиплексора, выходы второго и третьего мультиплексоров соединены с первым и вторым входами блока элементов ИЛИ соответственно, выход которого сое- (динен с входом сброса первого триггера управления, прямой выход первого триггера управления соединен с первым входом пятого элемента И, выход которого соединен с четвертыми управляющими входами второго и третьего мультиплексоров, выход первого

20 иен с четвертым управляющим входом первого канала,1 второй управляющий выход 1-го канала (i M,2) соединен с пятым управляющим входом (i-1)-ro канала, второй управляющий выход пер

элемента ИЛИ соединен с входом сброса 25 вого канала соединен с пятым улраввторого триггера управления, прямой

выход которого соединен с вторым вхоа

Редактор В. Данко

Фиг. 2 Составитель А. Иванов

Техред М.Ходанич Корректор В. Гирняк

дом пятого элемента И, с третьими и четвертыми входами первого и второго коммутаторов, четвертый управляющий вход канала соединен с пятым управляющим входом третьего мультиплексора, с пятым и шестым входами второго коммутатора, выход которого соединен с первым управляющим выходом канала,

пятый управляющий вход канала соединен с пятым управляющим выходом второго мультиплексора и с пятым и шестым входами первого коммутатора,выход которого соединен с вторым управляющим выходом канала, первый управляющий выход 1-го канала (i 1 ,М-1) соединен с четвертым управляю-- щим входом (i+O-ro канала, первый управляющий выход М-го канала соедииен с четвертым управляющим входом первого канала,1 второй управляющий выход 1-го канала (i M,2) соединен с пятым управляющим входом (i-1)-ro канала, второй управляющий выход первого канала соединен с пятым улравляющим входом 1-го канала.

I

| Патент CDIA № 3514860, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Устройство для обмена информацией | 1983 |

|

SU1118997A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1987-08-03—Подача