Изобретение относится к автоматике и вычислительной технике и может быть использовано, например, в системах управления шаговым приводом.

Цель изобретения - повышение достоверности преобразования при изменении веса входных импульсов.

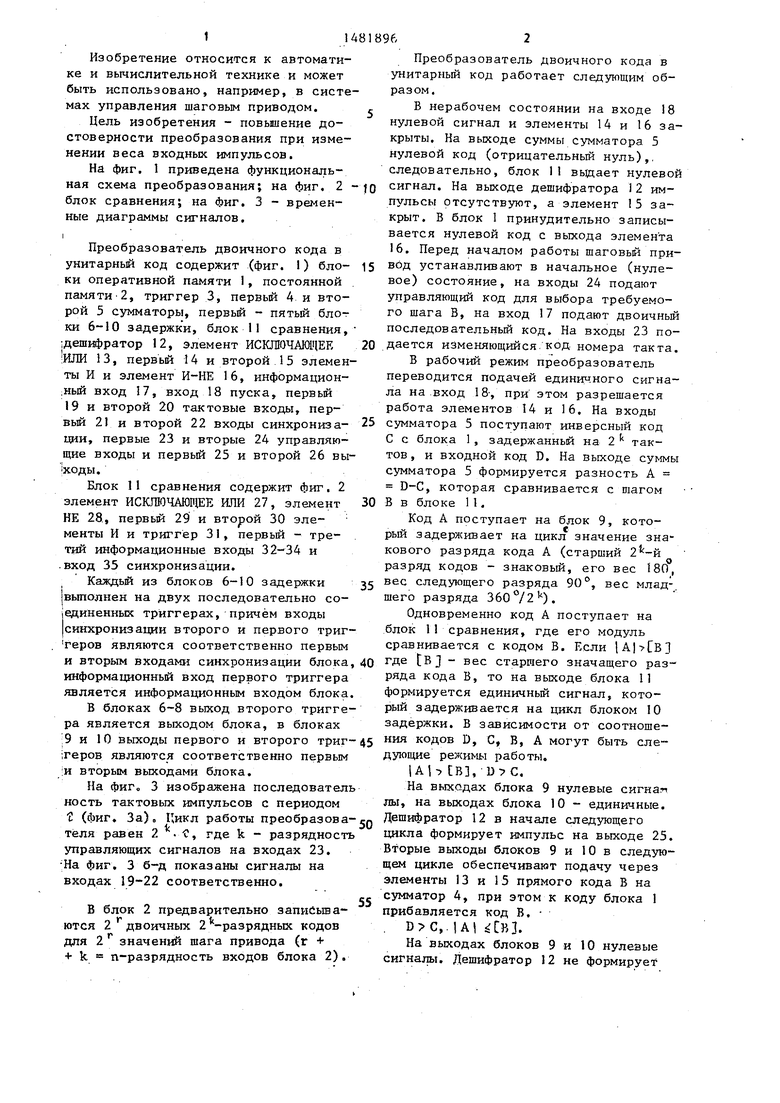

На фиг. 1 приведена функциональПреобразователь двоичного кода в унитарный код работает следующим образом.

В нерабочем состоянии на входе 18 нулевой сигнал и элементы 14 и 16 закрыты. На выходе суммы сумматора 5 нулевой код (отрицательный нуль),, следовательно, блок 11 выдает нулевой ная схема преобразования; на фиг. 2 - ю сигнал. На выходе дешифратора 12 им- блок сравнения; на фиг. 3 - времен- пульсы отсутствуют, а элемент 15 за- ные диаграммы сигналов.крыт. В блок 1 принудительно записывается нулевой код с выхода элемента

Преобразователь двоичного кода в 6. Перед началом работы шаговьй при- унитарньй код содержит (фиг. I) бло- 15 В°Д устанавливают в начальное (нуле- ки оперативной памяти 1, постоянной вое) состояние, на входы 24 подают

управляющий код для выбора требуемого шага В, на вход 17 подают двоичный последовательный код. На входы 23 подается изменяющийся код номера такта.

В рабочий режим преобразователь переводится подачей единичного сигнала на вход 18-, при этом разрешается

памяти-2, триггер 3, первый А и второй 5 сумматоры, первый - пятый блоки 6-10 задержки, блок 11 сравнения, дешифратор 12, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13, первый 14 и второй 15 элементы И и элемент И-НЕ 16, информацион- .ный вход 17, вход 18 пуска, первый 19 и второй 20 тактовые входы, пер20

работа элементов 14 и 16. На входы

вый 21 и второй 22 входы синхрониза- 25 сумматора 5 поступают инверсный код ции, первые 23 и вторые 24 управляю-С с блока 1, задержанньй на 2 k тактов , и входной код D. На выходе суммы сумматора 5 формируется разность А

щие входы и первый 25 и второй 26 вы- ходы.

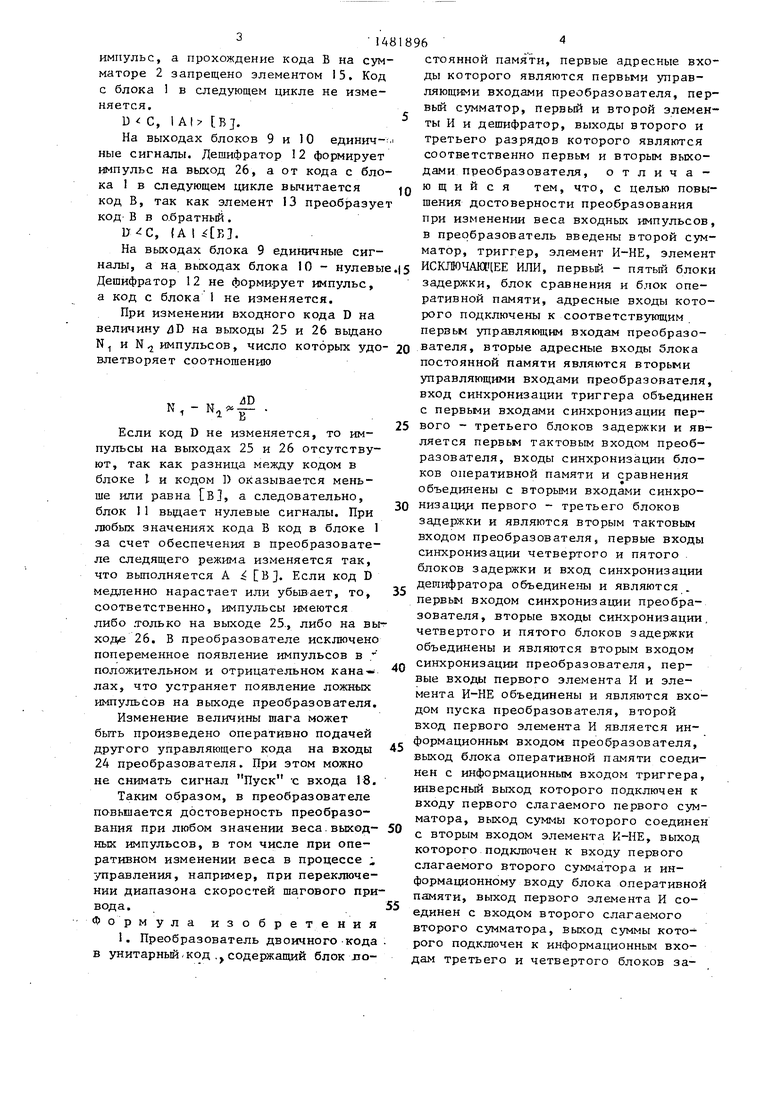

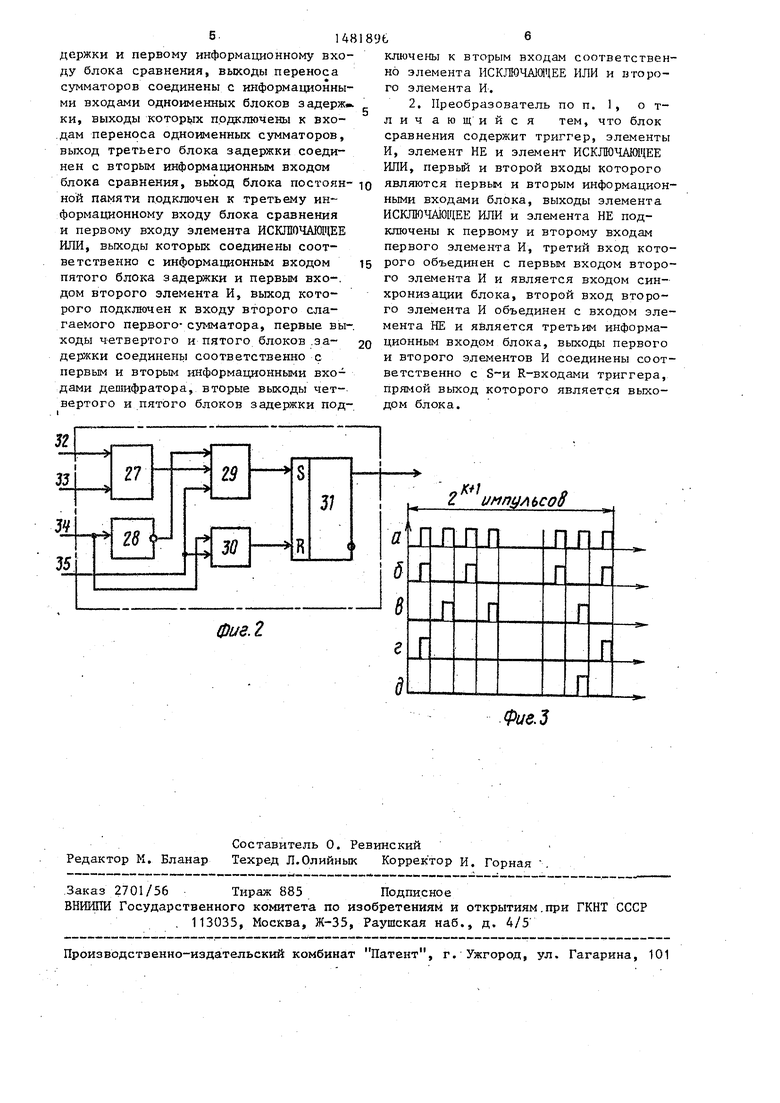

Блок 11 сравнения содержит фиг. 2 элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 27, элемент НЕ 28, первьй 29 и второй 30 элементы И и триггер 31, первьй - третий информационные входы 32-34 и .вход 35 синхронизации.

Каждый из блоков 6-10 задержки выполнен на двух последовательно соединенных триггерах, причём входы синхронизации второго и первого триг D-C, которая сравнивается с шагом 30 В в блоке 11.

Код А поступает на блок 9, который задерживает на цикл значение знакового разряда кода А (старший разряд кодов - знаковый, его вес 180, 25 вес следующего разряда 90°, вес млад-. шего разряда 360°/2).

Одновременно код А поступает на блок 11 сравнения, где его модуль

геров являются соответственно первымсравнивается с кодом В. Если

и вторым входами синхронизации блока, 40 гДе tBJ - вес старшего значащего раз- информационный вход первого триггераРяДа кода В, то на выходе блока 11

является информационным входом блока. формируется единичный сигнал, кото- В блоках 6-8 выход второго тригге- РЫЙ задерживается на цикл блоком 10 ра является выходом блока, в блокахзадержки. В зависимости от соотноше9 и 10 выходы первого и второго триг-45 ния К°Д°В ° с в А могут быть сле- ;геров являются соответственно первым дующие режимы работы. и вторым выходами блока.

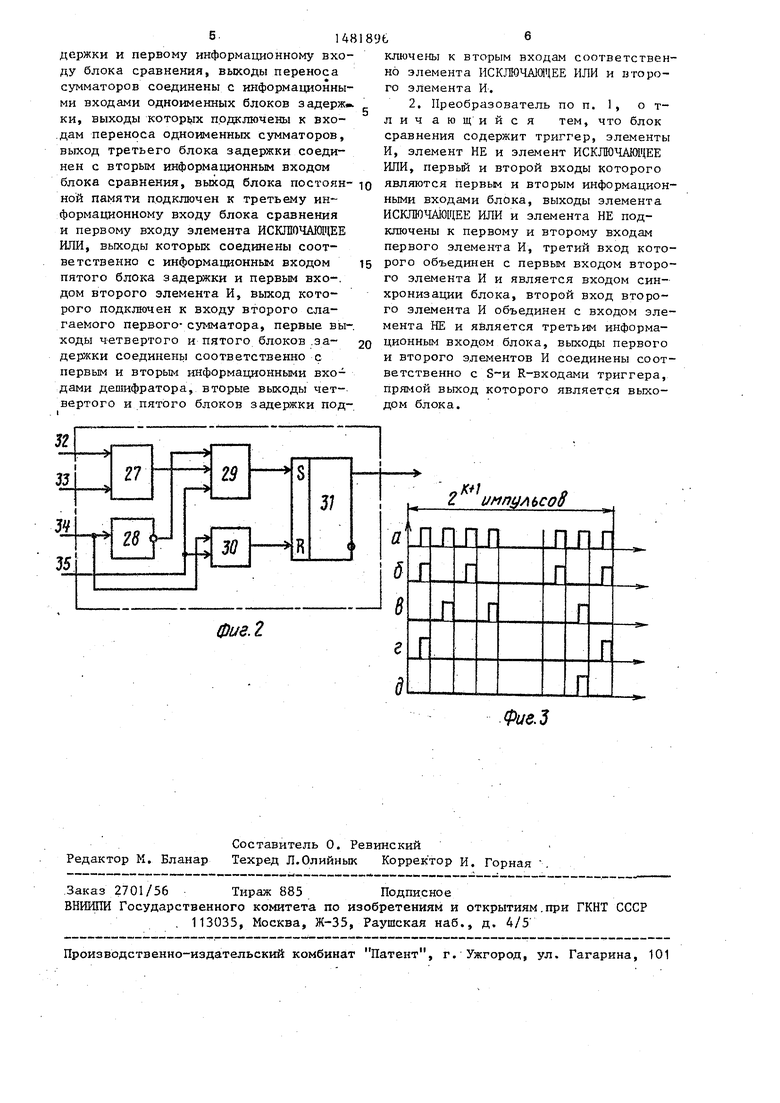

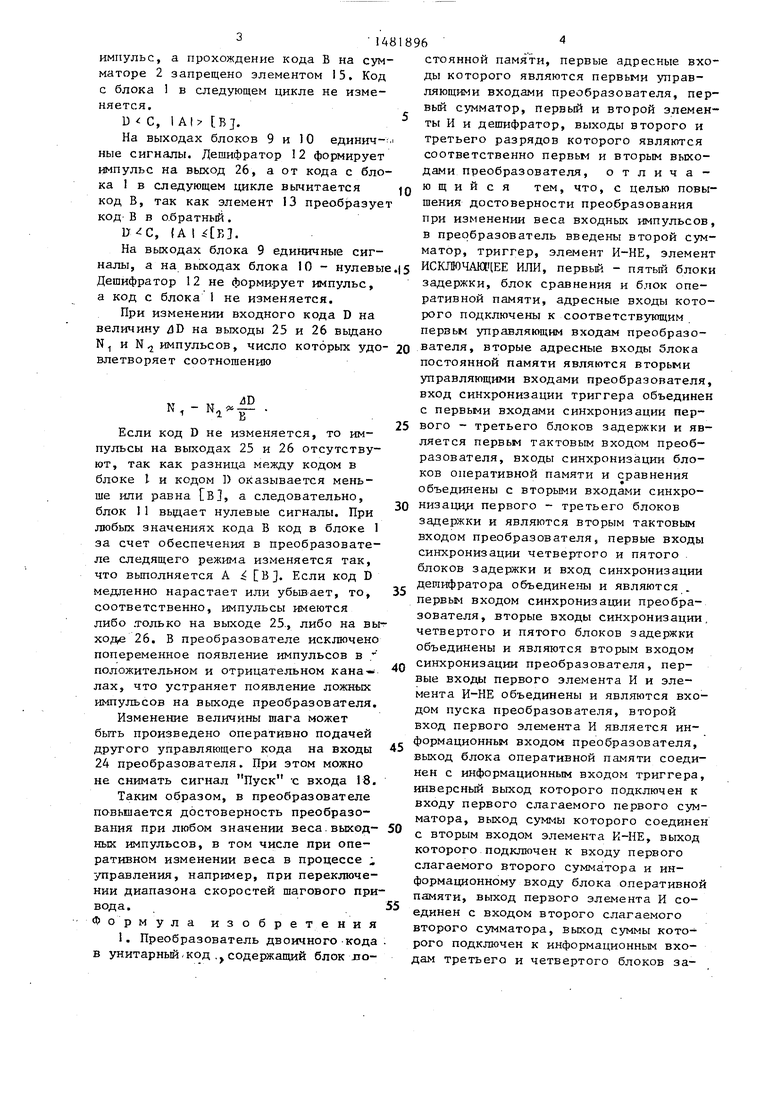

На фиг. 3 изображена последователь ность тактовых импульсов с периодом 1 (фиг. За), Цикл работы преобразова-зд теля равен 2 . , где k - разрядность управляющих сигналов на входах 23.

|А1- В, .

На выходах блока 9 нулевые сигна-п лы, на выходах блока 10 - единичные. Дешифратор 12 в начале следующего цикла формирует импульс на выходе 25. Вторые выходы блоков 9 и 10 в следующем цикле обеспечивают подачу через элементы 13 и 15 прямого кода В на сумматор 4, при этом к коду блока 1 прибавляется код В.

На фиг. 3 б-д показаны сигналы на входах 19-22 соответственно.

В блок 2 предварительно записываются 2гдвоичных 2 -разрядных кодов для 2 г значений шага привода (г + + k n-разрядность входов блока 2).

работа элементов 14 и 16. На входы

D-C, которая сравнивается с шагом 30 В в блоке 11.

Код А поступает на блок 9, котония К°Д°В ° с в А могут быть сле- дующие режимы работы.

|А1- В, .

На выходах блока 9 нулевые сигна-п лы, на выходах блока 10 - единичные. Дешифратор 12 в начале следующего цикла формирует импульс на выходе 25. Вторые выходы блоков 9 и 10 в следующем цикле обеспечивают подачу через элементы 13 и 15 прямого кода В на сумматор 4, при этом к коду блока 1 прибавляется код В.

,. 1А| .

На выходах блоков 9 и 10 нулевые сигналы. Дешифратор 12 не формирует

импульс, а прохождение кода В на сумматоре 2 запрещено элементом 15. Код с блока 1 в следующем цикле не изменяется.

U С, I At В.

На выходах блоков 9 и 10 единич- ные сигналы. Дешифратор 12 формирует импульс на выход 26, а от кода с блока 1 в следующем цикле вычитается код В, так как элемент 13 преобразует код В в обратный.

V С, {А I ЛВ.

На выходах блока 9 единичные сигналы, а на выходах блока 10 - нулевые Дешифратор 12 не формирует импульс, а код с блока 1 не изменяется.

При изменении входного кода D на величину 4D на выходы 25 и 26 выдано N, и N .j импульсов, число которых удо- влетворяет соотношению

N,4D

Если код D не изменяется, то импульсы на выходах 25 и 26 отсутствуют, так как разница между кодом в блоке I и кодом ) оказывается меньше или равна Гв, а следовательно, блок 11 выдает нулевые сигналы. При любых значениях кода В код в блоке 1 за счет обеспечения в преобразователе следящего режима изменяется так, что выполняется А В. Если код D медленно нарастает или убывает, то, соответственно, импульсы имеются либо .только на выходе 25, либо на выходе 26. В преобразователе исключено попеременное появление импульсов в - положительном и отрицательном каналах, что устраняет появление ложных импульсов на выходе преобразователя.

Изменение величины шага может быть произведено оперативно подачей другого управляющего кода на входы 24 преобразователя. При этом можно не снимать сигнал Пуск с входа 18.

Таким образом, в преобразователе повшается достоверность преобразования при любом значении веса выходных импульсов, в том числе при оперативном изменении веса в процессе „ управления, например, при переключении диапазона скоростей шагового привода. Формула изобретения

1. Преобразователь двоичного кода в унитарный -кодf содержащий блок ло

10

)5

0

5

0

5

0

5

5

0

стоянкой памяти, первые адресные входы которого являются первыми управляющими входами преобразователя, первый сумматор, первый и второй элементы И и дешифратор, выходы второго и третьего разрядов которого являются соответственно первым и вторым выходами преобразователя, отличающийся тем, что, с целью повышения достоверности преобразования при изменении веса входных импульсов, в преобразователь введены второй сумматор, триггер, элемент И-НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый - пятый блоки задержки, блок сравнения и блок оперативной памяти, адресные входы которого подключены к соответствующим перзьм управляющим входам преобразователя, вторые адресные входы блока постоянной памяти являются вторыми управляющими входами преобразователя, вход синхронизации триггера объединен с первыми входами синхронизации первого - третьего блоков задержки и является первым тактовым входом преобразователя, входы синхронизации блоков оперативной памяти и сравнения объединены с вторыми входами синхро- низацди первого - третьего блоков задержки и являются вторым тактовым входом преобразователя, первые входы синхронизации четвертого и пятого блоков задержки и вход синхронизации дешифратора объединены и являются . первым входом синхронизации преобразователя, вторые входы синхронизации четвертого и пятого блоков задержки объединены и являются вторым входом синхронизации преобразователя, первые входы первого элемента И и элемента И-НЕ объединены и являются входом пуска преобразователя, второй вход первого элемента И является информационным входом преобразователя, выход блока оперативной памяти соединен с информационным входом триггера, инверсный выход которого подключен к входу первого слагаемого первого сумматора, выход суммы которого соединен с вторым входом элемента К-НЕ, выход которого подключен к входу первого слагаемого второго сумматора и информационному входу блока оперативной памяти, выход первого элемента И соединен с входом второго слагаемого второго сумматора, выход суммы которого подключен к информационным входам третьего и четвертого блоков задержки и первому информационному входу блока сравнения, выходы переноса сумматоров соединены с информационными входами одноименных блоков задерж ки, выходы которых подключены к входам переноса одноименных сумматоров, выход третьего блока задержки соединен с вторым информационным входом блока сравнения, выход блока постоян- ной памяти подключен к третьему информационному входу блока сравнения и первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых соединены соответственно с информационным входом пятого блока задержки и первым входом второго элемента И, выход которого подключен к входу второго слагаемого первого- сумматора, первые выходы четвертого и пятого блоков за- держки соединены соответственно с первым и вторым информационными входами дешифратора, вторые выходы четвертого и пятого блоков задержки подключены к вторым входам соответственно элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второго элемента И.

2. Преобразователь по п. 1, о т- лич ающийся тем, что блок сравнения содержит триггер, элементы И, элемент НЕ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого являются первым и вторым информационными входами блока, выходы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента НЕ подключены к первому и второму входам первого элемента И, третий вход которого объединен с первым входом второго элемента И и является входом синхронизации блока, второй вход второго элемента И объединен с входом элемента НЕ и является третьим информационным входом блока, выходы первого и второго элементов И соединены соответственно с R-входами триггера, прямой выход которого является выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Многоканальный преобразователь код-частота | 1985 |

|

SU1267621A1 |

| Преобразователь двоичного кода | 1984 |

|

SU1208607A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1990 |

|

SU1793548A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

| Устройство для контроля и регулирования параметров | 1984 |

|

SU1249491A1 |

| Устройство для моделирования деятельности человека-оператора | 1987 |

|

SU1545226A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

Изобретение относится к автоматике и вычислительной технике. Его использование в системах управления шаговым приводом позволяет повысить достоверность преобразования при изменении веса входных импульсов. Преобразователь содержит блок 2 постоянной памяти, сумматор 4, элементы И 14, 15 и дешифратор 12. Благодаря введению блока 1 оперативной памяти, триггера 3, сумматора 5, блоков 6-10 задержки, блока 11 сравнения, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 и элемента И-НЕ 16 в преобразователе обеспечивается следящий режим формирования унитарного кода. 1 з.п. ф-лы, 3 ил.

Фие.З

| Приборы и техника эксперимента, 1987, № 4, с | |||

| Стиральная машина для войлоков | 1922 |

|

SU210A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1983 |

|

SU1124282A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-05-23—Публикация

1987-07-13—Подача