314

Изобретение относится к вычислительной технике и может быть использовано в системах автоматического управления.

Цель изобретения - расширения динамического диапазона рабочих частот входных импульсов.

Поставленная цель достигается тем что дополнительно задаются граничные значения преобразованного входного сигнала и, в процессе пр образова- ния временного интервала в сигнал, регистрируют его уровень, а затем изменяют опорную частоту, уменьшая ее в случае недостижения нижнего граничного значения сигнала, или увеличивая - в случае достижения или превышения верхнего граничного значения сигнала и используют ее для преобразования входного временного интервала в его следующем периоде.

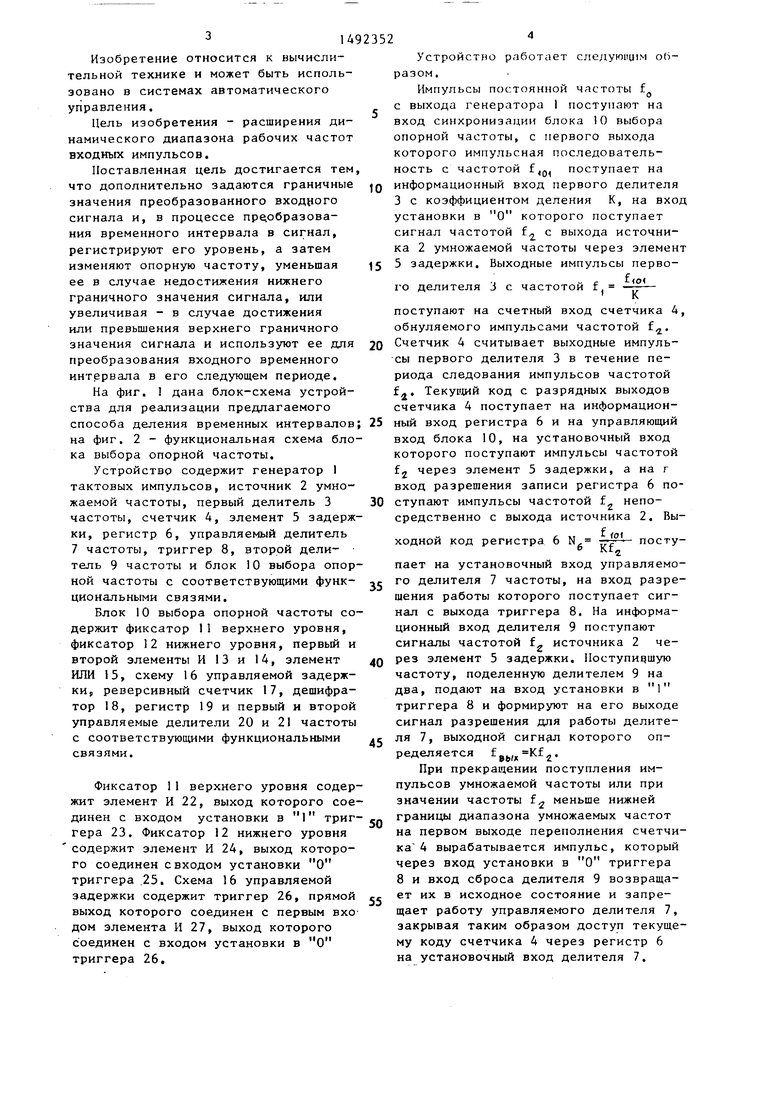

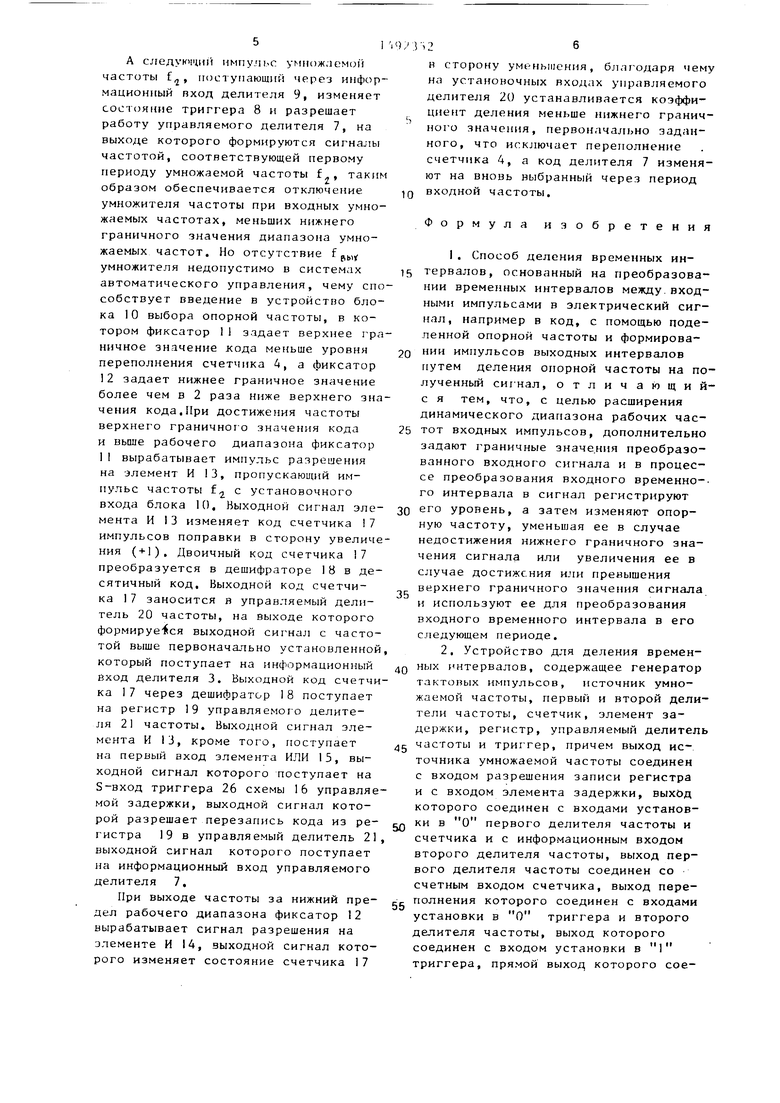

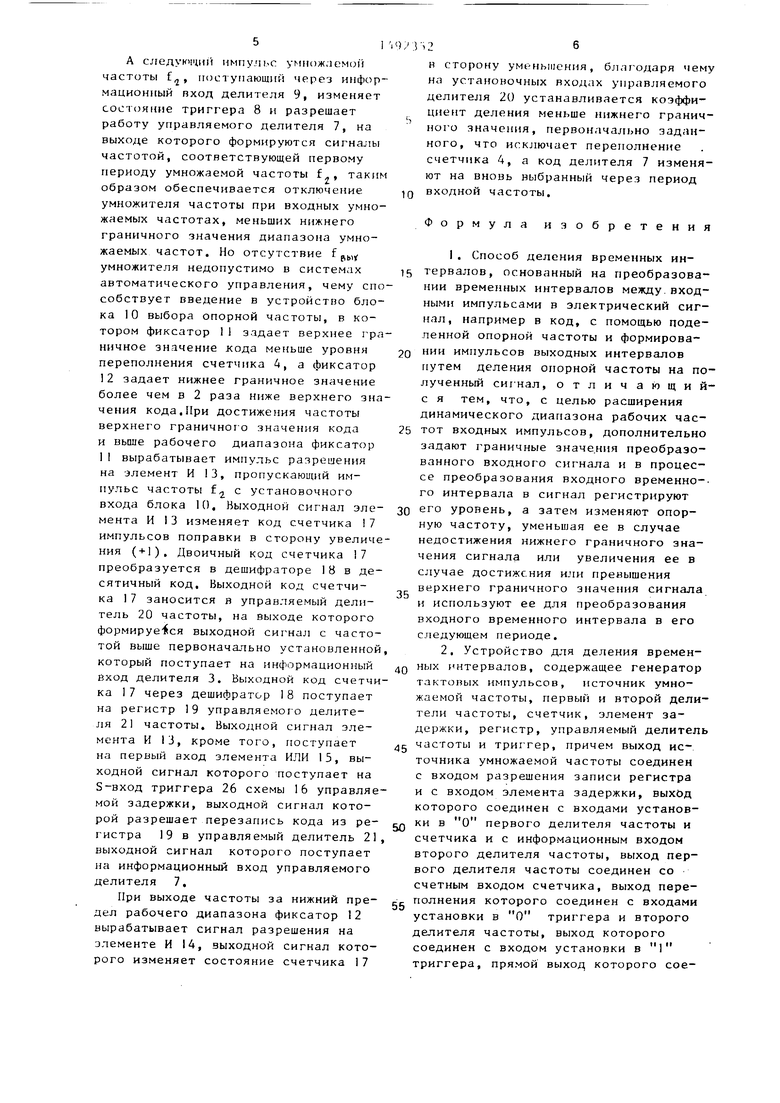

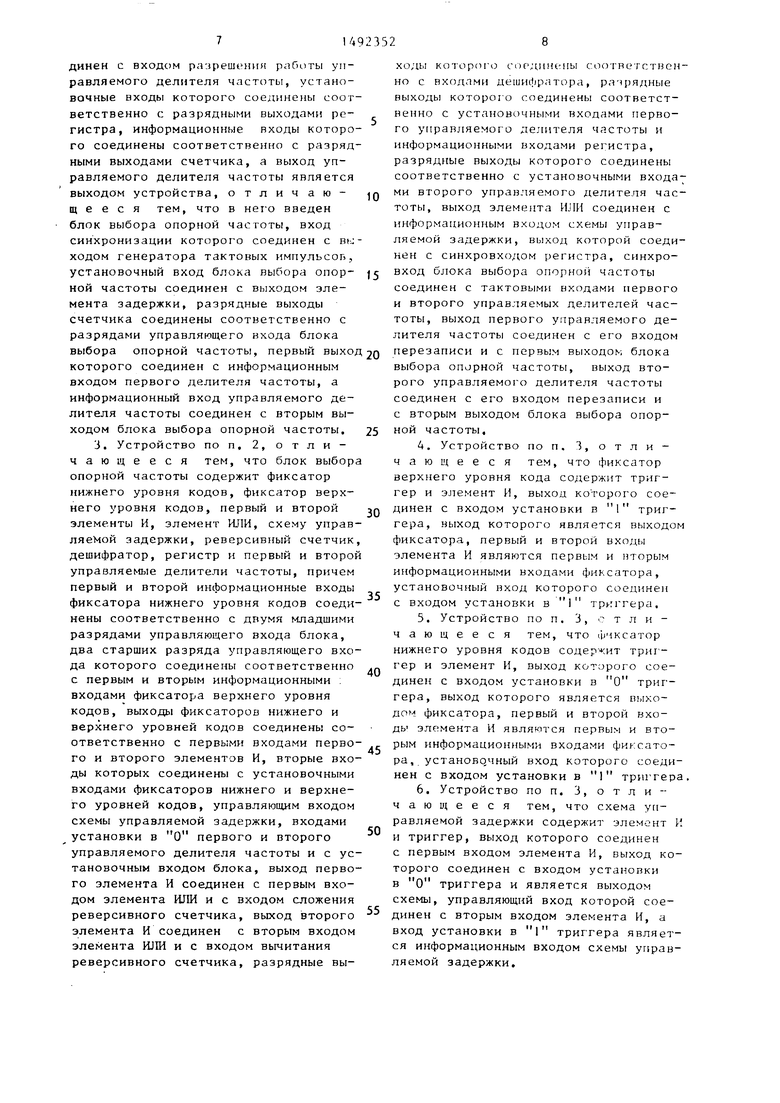

На фиг. I дана блок-схема устройства для реализации предлагаемого способа деления временных интервалов на фиг. 2 - функциональная схема блока выбора опорной частоты.

Устройство содержит генератор I тактовых импульсов, источник 2 умножаемой частоты, первый делитель 3 частоты, счетчик 4, элемент 5 задержки, регистр 6, управляемый делитель 7 частоты, триггер 8, второй делитель 9 частоты и блок 10 выбора опорной частоты с соответствующими функциональными связями.

Блок 10 выбора опорной частоты содержит фиксатор 11 верхнего уровня, фиксатор 12 нижнего уровня, первьй и второй элементы И 13 и 14, элемент ИЛИ 15, схему 16 управляемой задержки, реверсивный счетчик 17, дешифратор 18, регистр 19 и первый и второй управляемые делители 20 и 21 частоты с соответствующими функциональными связями.

Фиксатор 11 верхнего уровня содержит элемент И 22, выход которого соеIIIII

динен с входом установки в 1 триггера 23. Фиксатор 12 нижнего уровня содержит элемент И 24, выход которого соединен с входом установки О триггера .25. Схема 16 управляемой задержки содержит триггер 26, прямой выход которого соединен с первым входом элемента И 27, выход которого соединен с входом установки в О триггера 26,

0

5

0

5

Устройство работает следую1гц1м образом.

Импульсы постоянной частоты f с выхода генератора 1 поступают на вход синхронизации блока 10 выбора опорной частоты, с первого выхода которого импульсная последовательность с частотой f ,Q, поступает на информационный вход первого делителя 3 с коэффициентом деления К, на вход О которого поступает

выхода источника 2 умножаемой частоты через элемент 5 задержки. Выходные импульсы перво(о«

К

поступают на счетный вход счетчика 4, обнуляемого импульсами частотой f.. Счетчик 4 считывает выходные импульсы первого делителя 3 в течение периода следования импульсов частотой f. Текупд1й код с разрядных выходов счетчика 4 поступает на информационный вход регистра 6 и на управляющий вход блока 10, на установочный вход которого поступают импульсы частотой fj через элемент 5 задержки, а на г вход разрешения записи регистра 6 по- 0 ступают импульсы частотой f непосредственно с выхода источника 2. Выустановки в

сигнал частотой i с

го делителя 3 с частотой f

ходной код регистра 6 N,

f Kf.

fot

посту

пает на установочный вход управляемого делителя 7 частоты, на вход разрешения работы которого поступает сигнал с выхода триггера 8. На информационный вход делителя 9 поступают сигналы частотой f источника 2 через элемент 5 задержки. Поступившую частоту, поделенную делителем 9 на два, подают на вход установки в 1 триггера 8 и формируют на его выходе сигнал разрешения для работы делителя 7, выходной сигнал которого определяется f pj,j, Kf 2.

При прекращении поступления импульсов умножаемой частоты или при

значении частоты f меньше нижней границы диапазона умножаемых частот на первом выходе переполнения счетчика 4 вырабатывается импульс, который через вход установки в О триггера 8 и вход сброса делителя 9 возвращает их в исходное состояние и запрещает работу управляемого делителя 7, закрывая таким образом доступ текущему коду счетчика 4 через регистр 6 на установочный вход делителя 7.

А следукччш импульс умиож.чем) частоты f, поступающий через информационный вход делителя 9, изменяет состояние триггера 8 и разрешает работу управляемого делителя 7, на выходе которого формируются сигналы частотой, соответствующей первому периоду умножае.мой частоты f., таким образом обеспечивается отключение умножителя частоты при входных умножаемых частотах, меньших нижнего граничного значения диапазона умножаемых частот. Но отсутствие f умножителя недопустимо в системах автоматического управления, чему способствует введение в устройство блока 10 выбора опорной частоты, в котором фиксатор 11 задает верхнее граничное значение кода меньше уровня переполнения счетчика 4, а фиксатор 12 задает нижнее граничное значение более чем в 2 раза ниже верхнего значения кода,При достижения частоты верхнего граничного значения кода и выше рабочего диапазона фиксатор 1I вырабатывает импульс разрешения на элемент И 13, пропускающий импульс частоты f с установочного входа блока И), Выходной сигнал элемента И I3 изменяет код счетчика I7 импульсов поправки в сторону увеличения (), Двоичный код счетчика 17 преобразуется в дешифраторе 18 в десятичный код. Выходной код счетчика I7 заносится в управляемый делитель 20 частоты, на выходе которого формируешься выходной сигнал с частотой выше первоначально установленной который поступает на информационный йход делителя 3. Выходной код счетчика 17 через дешифратор 18 поступает на регистр 19 управляемого делителя 21 частоты. Выходной сигнал элемента И 13, кроме того, поступает на первый вход элемента ИЛИ 15, выходной сигнал которого поступает на З-БХОД триггера 26 схемы 16 управляемой задержки, выходной сигнал которой разрешает перезапись кода из регистра 19 в управляемый делитель 21 выходной сигнал которого поступает на информационный вход управляемого делителя 7,

При выходе частоты за нижний предел рабочего диапазона фиксатор 12 вырабатывает сигнал разрешения на элементе И 14, выходной сигнал которого изменяет состояние счетчика 17

0

5

0

5

0

5

0

5

0

5

н сторону уменьшения, благодаря чему на установочных входах управляемого делителя 20 устанавливается коэффи- циeflт деления меньше нижнего граничного значения, первоначально заданного, что исключает переполнение счетчика 4, а код делителя 7 изменяют на вновь выбранный через период входной частоты.

Формула изобретения

1 , Способ деления временных интервалов, основанный на преобразовании временных интервалов между.входными импульсами в электрический сигнал, например в код, с помощью поделенной опорной частоты и формировании импульсов выходных интервалов путем деления опорной частоты на полученный сигнал, отличающий- с я тем, что, с целью расширения динамического диапазона рабочих частот входных импульсов, дополнительно задают граничные значе.ния преобразованного входного сигнала и в процессе преобразования входного временно-. го интервала в сигнал регистрируют его уровень, а затем изменяют опорную частоту, уменьшая ее в случае недостижения нижнего граничного значения сигнала или увеличения ее в случае достижения или превышения верхнего граничного значения сигнала и используют ее для преобразования входного временного интервала в его следующем периоде,

2, Устройство для деления временных интервалов, содержащее генератор тактонь1Х импульсов, источник умножаемой частоты, первый и второй делители частоты, счетчик, элемент задержки, регистр, управляемый делитель частоты и триггер, причем выход источника умножаемой частоты соединен с входом разрешения записи регистра и с входом элемента задержки, выход которого соединен с входами установки в О первого делителя частоты и счетчика и с информационным входом второго делителя частоты, выход первого делителя частоты соединен со счетным входом счетчика, выход переполнения которого соединен с входами установки в О триггера и второго делителя частоты, выход которого соединен с входом установки в 1 триггера, прямой выход которого соединен с входом разрешения работы управляемого делителя частоты, установочные входы которого соединены соответственно с разрядными выходами регистра, информационные входы которого соединены соответственно с разрядными выходами счетчика, а выход управляемого делителя частоты является выходом устройства, отличающееся тем, что в нег о введен блок выбора опорной частоты, вход синхронизации которого соединен с выходом генератора тактовых импульсов, установочный вход блока выбора опорной частоты соединен с выходом элемента задержки, разрядные выходы счетчика соединены соответственно с разрядами управляющего входа блока выбора опорной частоты, первый выход которого соединен с информационным входом первого делителя частоты, а информационный вход управляемого делителя частоты соединен с вторым выходом блока выбора опорной частоты, 3. Устройство по п, 2, отличающееся тем, что блок выбор опорной частоты содержит фиксатор нижнего уровня кодов, фиксатор верхнего уровня кодов, первый и второй элементы И, элемент ИЛИ, схему управляемой задержки, реверсивный счетчик дешифратор, регистр и первый и второ управляемые делители частоты, причем первый и второй информационные входы фиксатора нижнего уровня кодов соединены соответственно с двумя младшими разрядами управляющего входа блока, два старших разряда управляющего входа которого соединены соответственно с первым и вторым информационными ; входами фиксатора верхнего уровня кодов, выходы фиксаторов нижнего и верхнего уровней кодов соединены соответственно с первь ми входами первого и второго элементов И, вторые входы которых соединены с установочными входами фиксаторов нижнего и верхнего уровней кодов, управляющим входом схемы управляемой задержки, входами установки в О первого и второго управляемого делителя частоты и с установочным входом блока, выход первого элемента И соединен с первым входом элемента ИЛИ и с входом сложения реверсивного счетчика, выход второго элемента И соединен с вторым входом элемента ШШ и с входом вьтитания реверсивного счетчика, разрядные вы

5

0

5

0

5

0

5

0

5

ходы которого сордииены соответственно с входами дешифратора, рлчрядные выходы которог о соединены соответственно с установочными входами первого управляемого делителя частоты и информационными входами регистра, разрядные выходы которого соединены соответственно с установочными входа7 ми второго управляемого делителя частоты, выход элемента ИЛИ соединен с информационным входом схемы управляемой задержки, выход которой соединен с синхровходом регистра, синхро- вход блока выбора опорной частоты соединен с тактовыми входами первого и второго управляемых делителей частоты, выход первого управляемого делителя частоты соединен с его входом перезаписи и с первым выходом блока выбора опорной частоты, выход второго управляемого делителя частоты соединен с его входом перезаписи и с вторым выходом блока выбора опорной частоты,

4.Устройство по п. 3, отличающееся тем, что фиксатор верхнего уровня кода содержит триггер и элемент И, выход которого соединен с входом установки в 1 триггера, выход которого является выходом фиксатора, первый и второй входы элемента И являются первым и пторым информационными входами фиксатора, установочный вход которого соединен

с входом установки в i Tptrrrepa,

5.Устройство по п. 3, отличающееся тем, что (рчксатор нижнего уровня кодов содержит триг - гер и элемент И, выход которого соединен с входом установки в О триггера, выход которого является выходом фиксатора, первый и второй входу элемента И являются первым и вторым информационными входами фиксатора, установочный вход которого соединен с входом установки в 1 триггера.

6.Устройство по п. 3, о т л и - чающееся тем, что схема управляемой задержки содержит элемент И и триггер, выход которого соединен

с первым входом элемента И, которого соединен с входом установки в О триггера и является выходом схемы, управляющий вход которой соединен с вторым входом элемента И, а вход установки в 1 триггера является информационным входом схемы управляемой задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1092504A2 |

| Сеточная модель | 1984 |

|

SU1260981A1 |

| Следящий умножитель частоты | 1979 |

|

SU832556A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1038943A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1001098A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1290313A1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Дискретный умножитель частоты | 1977 |

|

SU736099A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах автоматического управления. Цель изобретения - расширение динамического диапазона рабочих частот входных импульсов. Принцип данного способа деления временных интервалов заключается в задании граничных значений преобразованного входного сигнала, после чего в процессе преобразования временного интервала в сигнал регистрируют его уровень, а затем изменяют опорную частоту, уменьшая ее в случае недостижения нижнего граничного значения сигнала или увеличивая - в случае достижения или превышения верхнего граничного значения сигнала, и используют ее для преобразования входного временного интервала в его следующем периоде. Устройство, реализующее данный способ, содержит генератор 1 тактовых импульсов, источник 2 умножаемой частоты, первый делитель 3 частоты, счетчик 4, элемент 5 задержки, регистр 6, управляемый делитель 7 частоты, триггер 8, второй делитель 9 частоты и блок 10 выбора опорной частоты с соответствующими функциональными связями. Блок 10 выбора опорной частоты содержит фиксаторы верхнего и нижнего уровней, два элемента И,элемент ИЛИ, схему управляемой задержки, реверсивный счетчик, дешифратор, регистр и два управляемых делителя частоты. 2 ил.

| Множительно-делительное устройство | 1981 |

|

SU982002A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Умножитель частоты следования импульсов | 1982 |

|

SU1092504A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-07—Публикация

1987-01-23—Подача