Изобретение относится к автоматике и вычислительной технике и может быть использовано в стендовой аппаратуре.

Цель изобретения - повьш1ение достоверности контроля устройства.

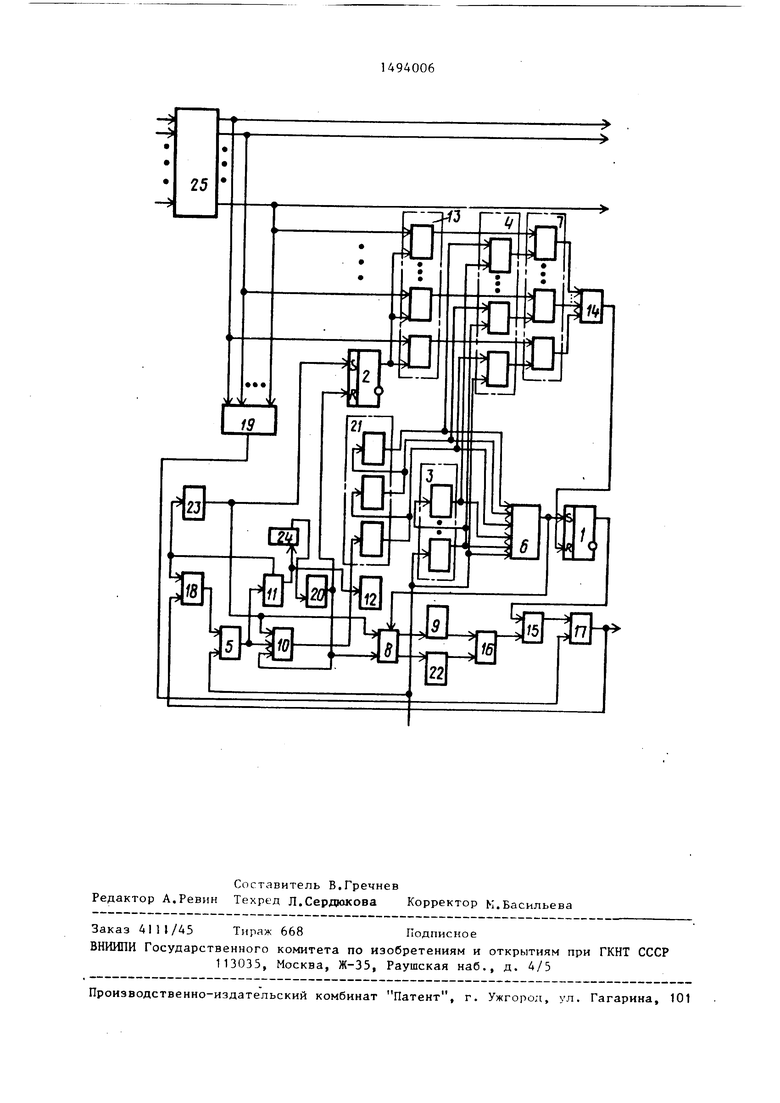

На чертеже изображена функционгшь- ная схема предлагаемого устройства.

Устройство содержит триггеры I и 2, первую группу 3 элементов задержки, группу 4 элементов ИЛИ, генератор 5 тактовых импульсов, третий элемент ИЛИ 6, группу 7 элементов И, второй коммутатор 8, первый элемент 9 за- .держки, первый коммутатор 10, счетчик II, блок 12 индикации, группу 13 элементов равнозначности, второй элемент ИЛИ 14, элемент И 15, четвертый элемент ИЛИ 16, первый элемент ИЛИ 17, пятый элемент ИЛИ 18, пороговый элемент 19, третий элемент 20 задержки, вторую группу 21 элементов задержки, второй элемент 22 задержки,. четвертый элемент 23 задержки, узел 24 дешифрации. Кроме того, на чертеже изображен контролируемый дешифратор 25, не входяи|яй в состав устройства.

Устройство работает следующим- образом.

Контролируется дешифратор, у которого только К комбинаций являются

СО 4:

а

разрешенными. Предполагается, что на вход контролируемого дешифратора 25 вначале в определенной последовательности подаются разрешенные коды, а затем - запрещенные, после чего контроль завершается.

Перед началом работы триггер 1 устанавливается в нулевое состояние а триггер 2 - в единичное со

стояние (цепи начальной установки не указаны).

Разрешенные коды на вход контролируемого дешифратора 25 подаются в такой последовательности, чтобы сиг- налы появлялись на его выходах поочередно с первого по К-й.

Одновременно с подачей первой кодвой комбинации на вход контролируемого дешифратора 25 поступает сиг- нал на вход запуска устройства. Этот сигнал через третий элемент ИЛИ 6 устанавливает в единичное состояние триггер 1. Одновременно он запускает генератор 5 тактовых импульсов и поступает на вход первого элемента задержки первой группы 3 элементов задержки и на первый вход первого элемента ИЛИ группы 4 элементов ИЛИ К этому времени при правильной работе контролируемого дешифратора 25 на первом входе первого элемента равнозначности группы 13 элементов равнозначности появляется единичный сигн а с соответствующего выхода дешифрато- ра 25. В результате единичный сигнал появляется и на выходе этого элемента равнозначности группы 13, элементов равнозначности,поскольку на его втором входе присутствует единичный сигнал с прямого выхода второго триггера 2. На выходах остальных элементов равнозначности группы 13 элементов равнозначности присутствуют нулевые сигналы. Единичный сигнал с выхода первого элемента равнозначности группы 13 элементов равнозначности разрешает прохождение сигнала с выхода первого элемента ИЛИ группы 4 элементов ИПИ через первый элемент И группы 7 элементов И на соответствующий вход второго элемента ИЛИ группы 4 элементов ИЛИ. Сигнал с выхода элемента ИЛИ группы 4 элементов ИЛИ сбрасывает в нулевое состояние первый триггер 1 . Таким образом, при правильной работе контролируемого дешифратора 25 триггер 1 к моменту поступления на второ

0

5

0

5

05

вход элемента И 15 импульса с выхода третьего элемента ИЛИ 6, прошедшего через второй коммутатор 8, первый элемент 9 задержки и четвертый элемент ИЛИ 16, оказывается в нулевом состоянии и его прямой выход закрывает элемент И 15, препятствуя формированию единичного сигнала на выходе неисправности устройства.

Через интервал времени, равный Т, на вход контролируемого дешифратора 25 поступает код следующей разрешенной комбинации,в результате чего на его втором выходе формируется единичный сигнал, и одновременно появляется сигнал на выходе первого элемента задержки первой группы 3 элементов задержки задержка всех элементов задержки группы 3 равна Т), устанавливающий через третий элемент ИЛИ 6 триггер 1 в единичное состояние. Сигнал с выхода первого элемента задержки первой группы 3 элементов задержки проходит через второй элемент И группы 7 элементов И. К этому времени на выходе второго элемента равнозначности присутствует единичный потенциал, в результате чего сигнал с выхода второго элемента И группы 7 элементов И через второй элемент ИЛИ 14 сбрасывает в нулевое состояние триггер 1, препятствуя формированию сигнала на выходе неисправности устройства .

При исправном контролируемом дешифраторе 25 сигналы с выходов последующих элементов задержки первой группы 3 элементов задержки опрашивают соотвбтстэующие элементы И группы 7 элементов И, проверяя правильность работы контролируемого дешифратора. При этом сигналы с выхода генератора 5 тактовых импульсов (их период еле-. 5 дования также равен Т) ггодсчитьгоают- ся счетчиком П,

Устройство контролирует появление сигнала на выходе дешифратора 25, нег- соответствующего входному коду, появление сигналов на нескольких выходах дешифратора 25 или отсутствие сигнала на его выходах.

Если, например, после поступления на вход дешифратора 25 кода второй разрешенной комбинации сигнал на втором выходе дешифратора 25 не появится (он появится на другом выходе или не появится вообще), то (как укаг зывалось выше) сигнал с выхода перво0

0

5

го элемента задержки первой группы 3 элементов задержки через элемент ИЛИ 6 установит в единичное состояние триггер I и через второй элемент ИЛР1 группы 4 элементов ШШ поступит на опрос второго элемента И группы 7 Ьлементов И, На выходе второго элемента равнозначности группы 13 элементов равнозначности присутствует нулевой сигнал, поскольку на первом входе этого элемента равнозначности группы 13 элементов равнозначности присутствует нулевой сигнал, а на втором - единичный с выхода тригге- ра 2, Поэтому второй элемент И группы 7 элементов И оказьшается-закры- тым и триггер 1 остается в единичном состоянии.

Сигнал с выхода элемента ИЛИ 6 проходит на первый выход второго коммутатора 8, задерживается на первом элементе 9 задержки на время, равное половине периода Т, а затем через элемент ИЛИ 16, элемент И 15 и эле- мент ИЛИ 17 проходит на выход неисправности устройства. Сигнал неисправности, пройдя через элемент ИЛИ 18, останавливает генератор 5 тактовых импульсов и на блоке 12 индикаци высвечивается код счетчика 11,соответствующий номеру входной комбинации дешифратора 25, на которой обнаружена неисправность контролируемого дешифратора 25.

Появление нескольких сигналов на выходах дешифратора 23 фиксируется пороговым элементом 19. Сигнал,с его вьгхода проходит через первый элемент ИЛИ 17 на выход неисправности устрой ства и также останавливает генератор 5 тактовых импульсов.

При правильной работе контролируемого дешифратора 25 после появления

сигнала на выходе последнего (К-|)-го 5 контролируемого дешифратора, выход

элемента задержки группы 3 элементов задержки на счетчике 11 устанавливается код К, который фиксируется узлом 24 дешифрации. В результате сигнал с его вьгхода переключает через третий элемент 20 задержки коммутаторы 8 и 10 и устанавливает в нулевое состояние триггер 2. Начинается контроль работы дешифратора 25 при поступлении на его входы неразрешенных комбинаций.

На вход дешифратора 25 поступает .первая неразрешенная комбинация. При этом на его выходах, подключенных к

50

55

порогового элемента соединен с первым входом первого элемента ИЛИ, вы ход которого является выходом неисправности устройства, выходы элемен тов И группы соединены с соответствующими входами второго элемента ИЛ выход которого соединен с нулевым входом первого триггера, прямой вы ход которого соединен с первым входом элемента И, выход которого соединен с вторым входом первого элеме та ИЛИ, первый вход третьего элемен та ЫШ и вход первого элемента задержки пррвой группы подключены к

5

0 5 О

о

5

устройству, не должно быть единичных сигналов.

Сигнал с вьгхода генератора 5 импульсов через первый коммутатор 10 проходит на вход первого элемента задержки второй группы 21 элементов задержки. Элементы задержки проверяют -отсутствие сигналов на выходах дешифратора для каждой неразрешенной комбинации.

Величина задержки элементов второй группы 21 элементов задержки в К раз меньше периода Т,

Контроль проводится, как и Bi чае проверки разрешенных комбинаций, но сигнал с выхода элемента ИЛИ 6 . проходит на второй выход второго коммутатора 8 и опрашивает элемент И 15 через элемент 22 задержки и элемент ИЛИ 16. Задержка на элементе 22 задержки в два раза меньше задержки на элементах второй группы 21,элементов задержки.

После перебора всех кодов на входе контролируемого дешифратора 25 сигнал переполнения счетчика I1 через элемент ИЛИ 18 останавливает генератор 5 тактовых импульсов, а через элемент 23 задержки устанавливает второй триггер 2 и коммутаторы 8 и 10 в исходное состояние. Проверка завершена.

Формула изобретения

Устройство для контроля дешифратора, содержащее пороговый элемент, три элемента ИЛИ, элемент И, первый триггер, группу элементов И и первую группу элементов задержки, причем входы порогового элемента образуют группу информационных входов устройства для подключения к группе выходов

0

5

порогового элемента соединен с первым входом первого элемента ИЛИ, выг- ход которого является выходом неисправности устройства, выходы элементов И группы соединены с соответствующими входами второго элемента ИЛИ, выход которого соединен с нулевым входом первого триггера, прямой выход которого соединен с первым входом элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, первый вход третьего элемента ЫШ и вход первого элемента задержки пррвой группы подключены к

в.ходу запуска устройства, выход каждого предыдущего элемента задержки первой группы соединен с входом последующего элемента задержки первой груп пы, выходы всех элементов задержки группы соединены с соответствующими входами третьего элемента ИЛИ, выход которого соединен с единичным входом первого триггера, отличающееся тем, что, с целью повьпнения достоверности контроля устройства, в него введены группа элементов равнознач- ности, группа элементов ИЛИ, второй триггер, генератор тактовых импуль сов, счетчик, блок-индикации, четыре элемента задержки, вторая группа элементов задержки, четвертый и пятый элементы ИЛИ, два коммутатора и узел дешифрации, причем вход запус- ка генератора тактовых импульсов подключен к входу запуска устройства, выход генератора тактовых импульсов соединен со счетным входом счетчика и информационным входом первого ком- мутатора, выход которого соединен с входом первого элемента задержки второй группы, выход каждого предыдущего элемента задержки второй группы соединен с входом последую- щего элемента задержки второй группы выходы элементов задержки второй группы - с соответствующими входами третьего элемента ИЛИ, первые входы

элементов равнозначности группы под

ключены к соответствующим информационным входам устройства для подключения к группе выходов контролируемого дешифратора, прямой выход второго триггера, соединен с вторыми входами всех элементов равнозначности группы, выходьЕ которых соединены

с первыми входами соответствующих элементов И группы, первый вход первого элемента ИЛИ группы подключен к входу запуска устройства, первые входы элементов ИЛИ группы, начиная с второго, соединены с выходами соответствующих элементов задержки первой группы, выходы элементов задержки второй группы - с вторыми входами соответствующих элементов ИЛИ группы, выходы которых соединены с вторыми входами соответствующих элементов И группы, выход третьего элемента ИЛИ соединен с информационным входом второго коммутатора, первый и второй выходы которого соединены соответственно через первый и второй элементы задержки с соответствующими входами четвертого элемента ИЛИ, выход которого соединен с вторым входом элемента И, информационный выход счетчика соединен с информационными входа-; ми блока индикации и узла дешифрации, выход которого, соответствующий числу разрешенных комбинаций контролируемого дешифратора, соединен через третий элемент задержки с нулевым входом второго триггера и первыми управляющими входами первого и второго коммутаторов, выход первого элемента ИЛИ соединен с первым входом пятого элемента ИЛИ, выход которого соединен с входом останова генератора тактовых импульсов, выход переполнения счетчика - с вторым входом пятого элемента ИЛИ и входом четвертог го элемента задержки, выход которого соединен с единичным входом второго триггера и вторыми управляющими входами первого и второго коммутаторов .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приемопередачи в кольцевом канале связи | 1986 |

|

SU1314361A1 |

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Преобразователь параллельного кода в последовательный | 1987 |

|

SU1547076A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| Устройство для контроля схем сравнения | 1981 |

|

SU970377A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1390616A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

| Устройство для тренировки операторов | 1989 |

|

SU1647621A1 |

| Генератор псевдослучайных чисел | 1984 |

|

SU1239844A1 |

| Устройство для контроля схем сравнения | 1985 |

|

SU1297062A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в стендовой аппаратуре. Цель изобретения - повышение достоверности контроля устройства. Устройство запускается одновременно с подачей первого кода на вход контролируемого дешифратора. Вначале на вход контролируемого дешифратора подаются в определенной последовательности разрешенные коды, и сигнал запуска с помощью первой группы элементов задержки, группы элементов равнозначности, группы элементов И, группы элементов ИЛИ контролирует правильность очередности формирования сигналов на выходах контролируемого дешифратора. Наличие на выходах контролируемого дешифратора нескольких сигналов контролируется пороговым элементом. По окончании проверки разрещенных комбинаций на вход контролируемого дешифратора поступают запрещенные комбинации. В это время на выходах контролируемого дешифратора не должно быть сигналов, что и контролируется второй группой элементов задержки с помощью группы элементов РАВНОЗНАЧНОСТИ, группы элементов И и группы элементов ИЛИ. 1 ил.

| Устройство для контроля дешифратора | 1974 |

|

SU544969A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля дешифратора | 1980 |

|

SU918948A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-15—Публикация

1987-10-13—Подача