4

СО

со

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дискретных сигналов | 1988 |

|

SU1597881A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для ввода информации | 1983 |

|

SU1149236A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1309032A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ЧИСЛА ПРОСТОЕВ ОБОРУДОВАНИЯ | 1991 |

|

RU2017219C1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для измерения плоских углов | 1988 |

|

SU1567885A1 |

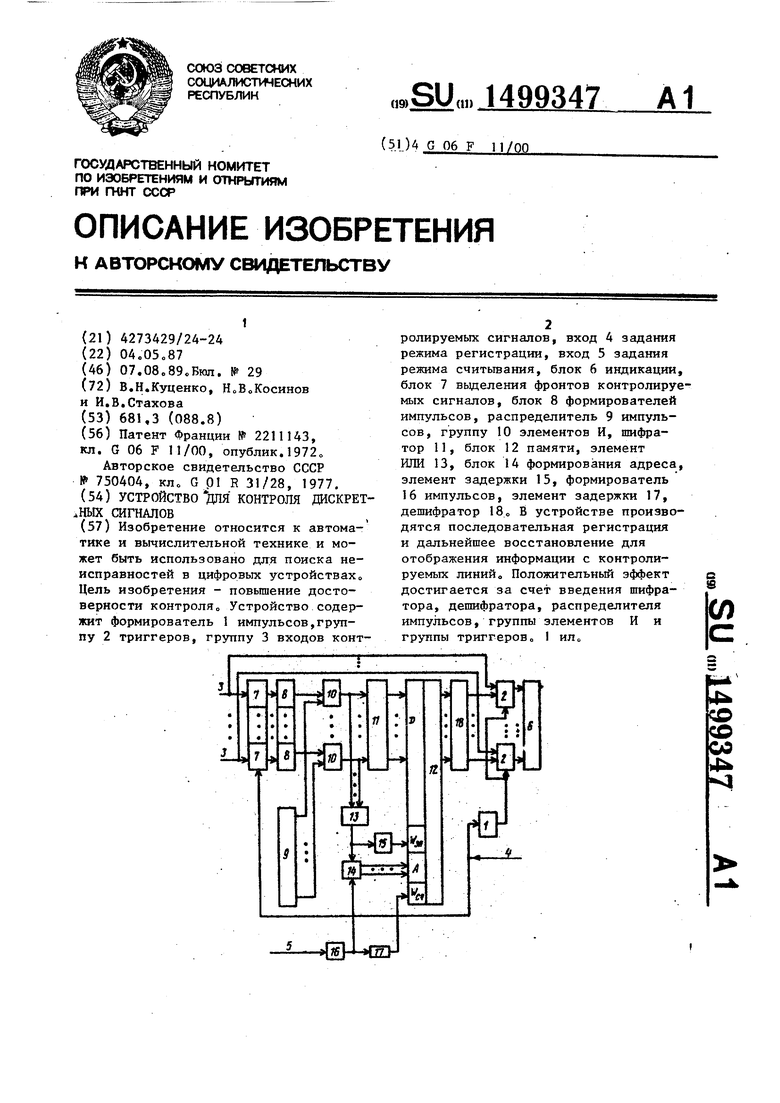

Изобретение относится к автоматике и вычислительной технике и может использовано для поиска неисправностей в цифровых устройствах. Цель изобретения - повышение достоверности контроля. Устройство содержит формирователь 1 импульсов, группу 2 триггеров, группу 3 входов контролируемых сигналов, вход 4 задания режима регистрации, вход 5 задания решения считывания, блок 6 индикации, блок 7 выделения фронтов контролируемых сигналов, блок 8 формирователей импульсов, распределитель 9 импульсов, группу 10 элементов И, шифратор 11, блок 12 памяти, элемент ИЛИ 13, блок 14 формирования адреса, элемент задержки 15, формирователь 16 импульсов, элемент задержки 17, дешифратор 18. В устройстве производятся последовательная регистрация и дальнейшее восстановление для отображения информации с контролируемых линий. Положительный эффект достигается за счет введения шифратора, дешифратора, распределителя импульсов, группы элементов И и группы триггеров. 1 ил.

3149

Изобретение относится к автоматике и вычислительной технике и может использоваться для поиска неисправностей в цифровых устройствах.

Цель изобретения - повышение достоверности контроля о

На чертеже дана схема устройства для контроля дискретных сигналов,,

Устройство содержит формирователь 1 импульсов, группу триггеров 2,группу 3 входов контролируемых сигналов, вход А задания режима регистрации, вход 5 задания режима считывания, блок 6 индикации, блок 7 вьщеления фронтов контролируемых сигналов,блок 8 формирователей импульсов, распределитель 9 импульсов, группу элементов И 10, шифратор 11, блок 12 памяти, элемент ИЛИ 13, блок 14 формиро- вания адреса, первый элемент 15 задержки, формирователь 16 импульсов, второй элемент 17 задержки, дешифратор 18„

Устройство работает следующим об- разом.

При появлении на входе 4 сигнала Регистрации запускается формирователь 1 импульс в, сигнал с которого поступает на входы записи триггеров грзтпЫо Таким образом, счетные триггеры 2 группы установлены в начальное состояние, соответствующее состояниям контролируемых входов 3 в момент появления сигнала Регистра- ция. Сигнал Регистрация разрешает также работу блока 7 выделения фронтов контролируемых сигналов, который формирует короткие импульсы, запускающие блок В формирователей импуль- .сов, формирующий импульсы длительностью в N раз большей, чем длительность такта распределителя импульсов.

При наличии на соответствующем выходе распределителя 9 импульсов и на соответствукяцем выходе блока 8 формирователей импульсов сигналов единичного значения импульс единичного значения поступает через соот- ветствую1ций элемент И 10 группы на шифратор 11 о Шифратор 11 формирует код линии, на которой произошло изменение уровня входного сигнапа Импульсы с элементов И 10 поступают также на элемент ИЛИ 13, единичное значение на выходе которого свиде- тельствует об изменении логического значения сигнала на одном из контролируемых входов 3 и необходимости увеличения на единицу значения адреса блока 14 формирования Адреса.По сформированному адресу код с выхода шифратора 11 записывается в блок 12 памяти при наличии разрешающего сигнала на входе записи с выхода элемента 15 задержки, длительность которого определяется длительностями задержек шифратора 11 и блока 14

Считьтание из блока 12 памяти записанной информации с целью ее последующего анализа происходит при наличии сигнала Считывание на входе 5, разрешающего работу формирователя 16 импульсов, импульс с которого изменяет значение адреса блока 14 формирования адреса на единицу и поступает через второй элемент 17 задержки на управляющий вход считывания блока 12. Считанные коды номеров контролируемых.входов поступают на дешифратор 18, сигнал единичного значения с соответствующего выхода которого поступает на счетный вход счетного триггера 2 группы,изменяя его состояние на противоположное. Информация со счетных триггеров 2 поступает на: устройство индикации - блок 6 о

Формула изобретения

Устройство для контроля дискретных- сигналов, содержащее блок памя- ти два элемента задержки, элемент ИЛИ, блок формирования адреса,пер- вьй формирователь импульсов, блок индикации, блок вьщеления фронтов контролируемых сигналов, блок формирователей импульсов, причем выход элемента ИЛИ соединен с первым входом синхронизации блока формирования адреса и с входом первого элемента задержки, выход которого соединен с входом записи блока памяти, группа адресных входов которого соединена с группой выходов блока формирования адреса, второй вход синхронизации которого соединен с входом второго элемента задержки и подключен к выходу первого формирователя импульсов, вход которого является входом задания режима считывания устройства, группа входов контролируемых сигналов которого соединена с группой входов блока выделения фронтов контролируемых сигналов, выход второго элемента задержки соединен с входом считывания блока памяти, отличающееся тем, что, с целью повьгаения достоверности контроля, в устройство введены распределитель импульсов, группа элементов И, шифратор, дешифратор, группа триггеров, второй формирователь им- пулксов, причем вход задания режима регистрации устройства соединен с входом второго формирователя импульсов и с входом разрешения блока выделения фронтов контролируемых сигналов, группа выходов которого соединена с группой входов блока формирователей импульсов, выходы которого соединены с первыми входами соответ

ствующих элементов И группы, вторые входы котороых соединены с выходами распределителя импульсов, выход второго формирователи импульсов соединен с входами записи триггеров группы, выходы которых соединены с входами блока индикации, выходы элементов И группы соединены с входами элемента ИЛИ и с входами шифратора, группа выходов которого соединена с группой информационных входов блока памяти, группа выходов которого сое- динеиа с группой входов дешифратора, выхойы которого соединены со счетными входами соответствующих триггеров группы, группа информационных входов которых соединена с группой входов контролируемьпс сигналов устройства.

| УСТРОЙСТВО ДЛЯ НАНЕСЕНИЯ КЛЕЕВОГО ПОКРЫТИЯ НА ЗАГОТОВКИ ПРОТЕКТОРОВ | 2002 |

|

RU2211143C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-07—Публикация

1987-05-04—Подача