Изобретение относится к коммутационной технике и может быть использовано при построении сотовых систем радиосвязи.

Целью изобретения является повьше- ние надежности за счет уменьшения количества связей и децентрализации управления коммутатором.

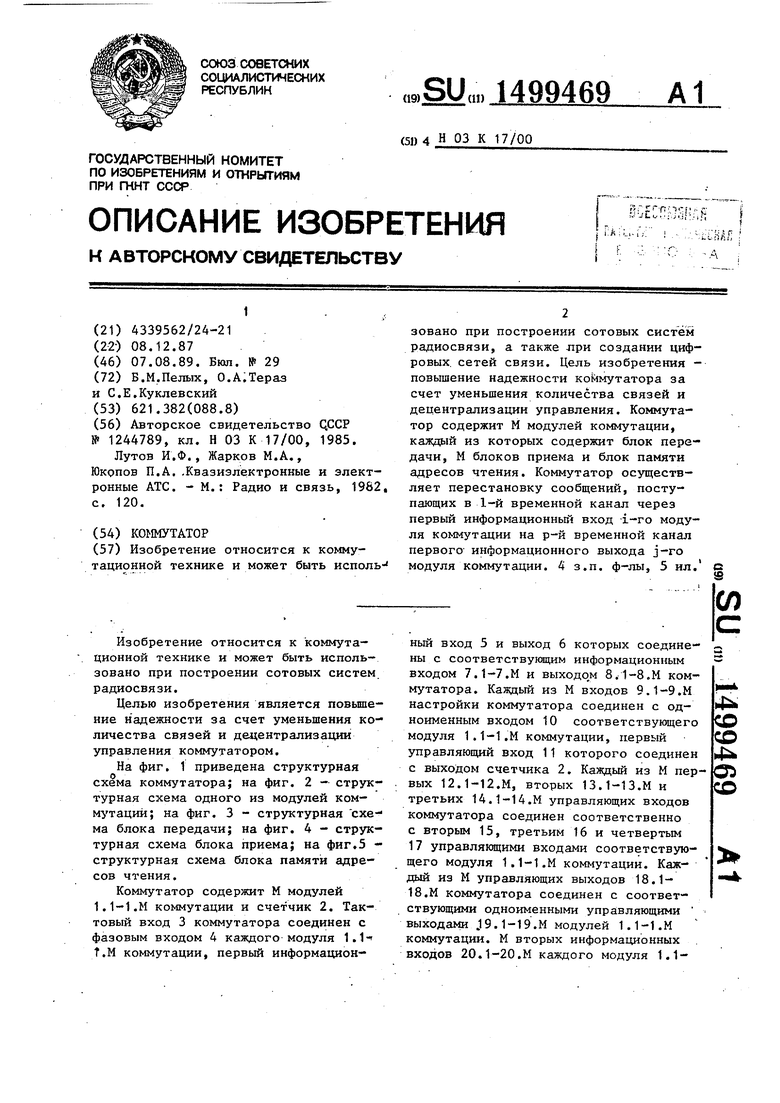

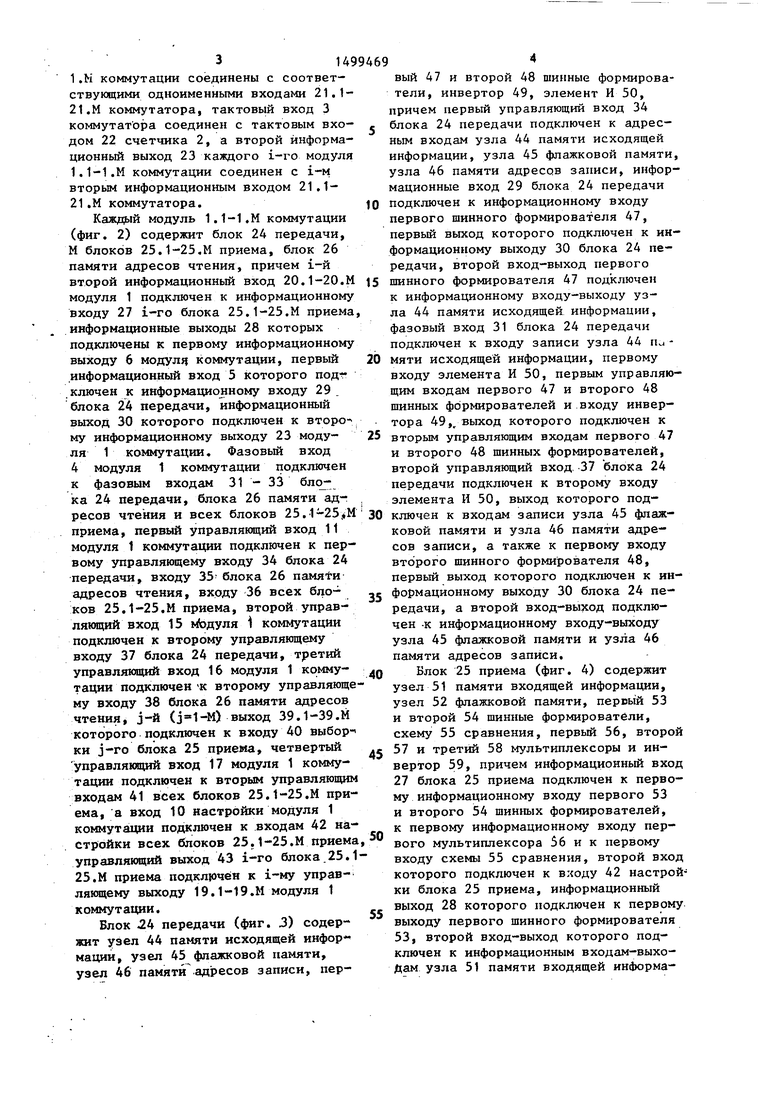

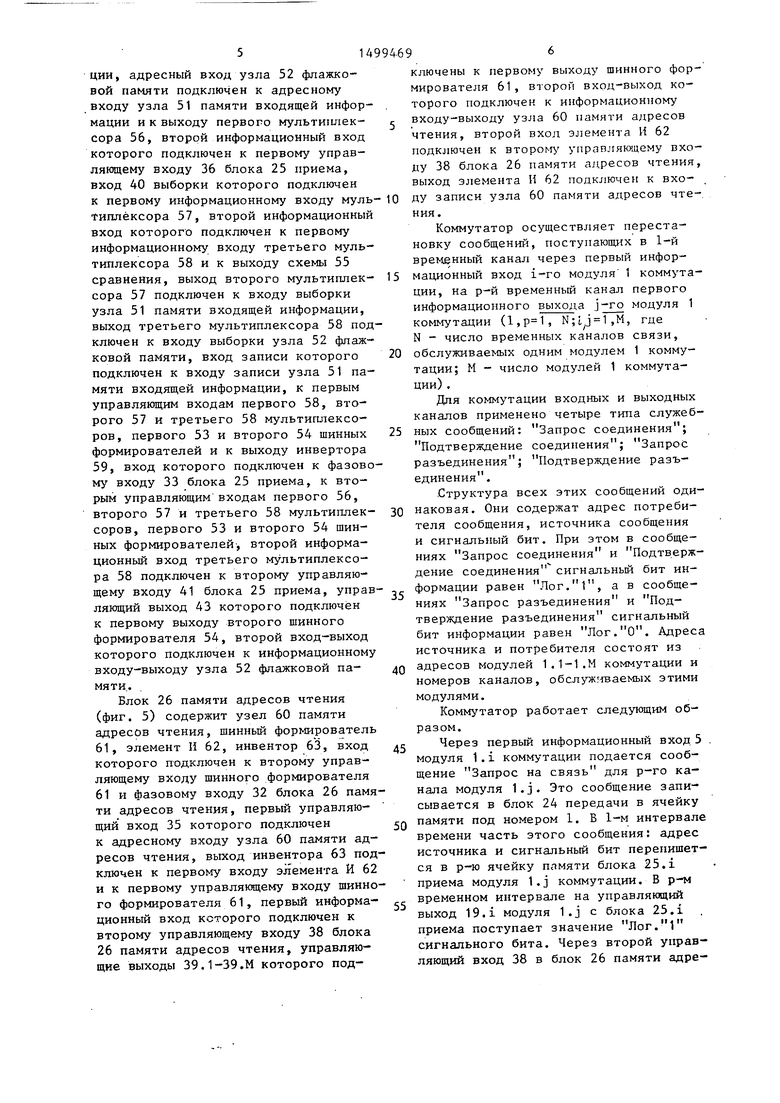

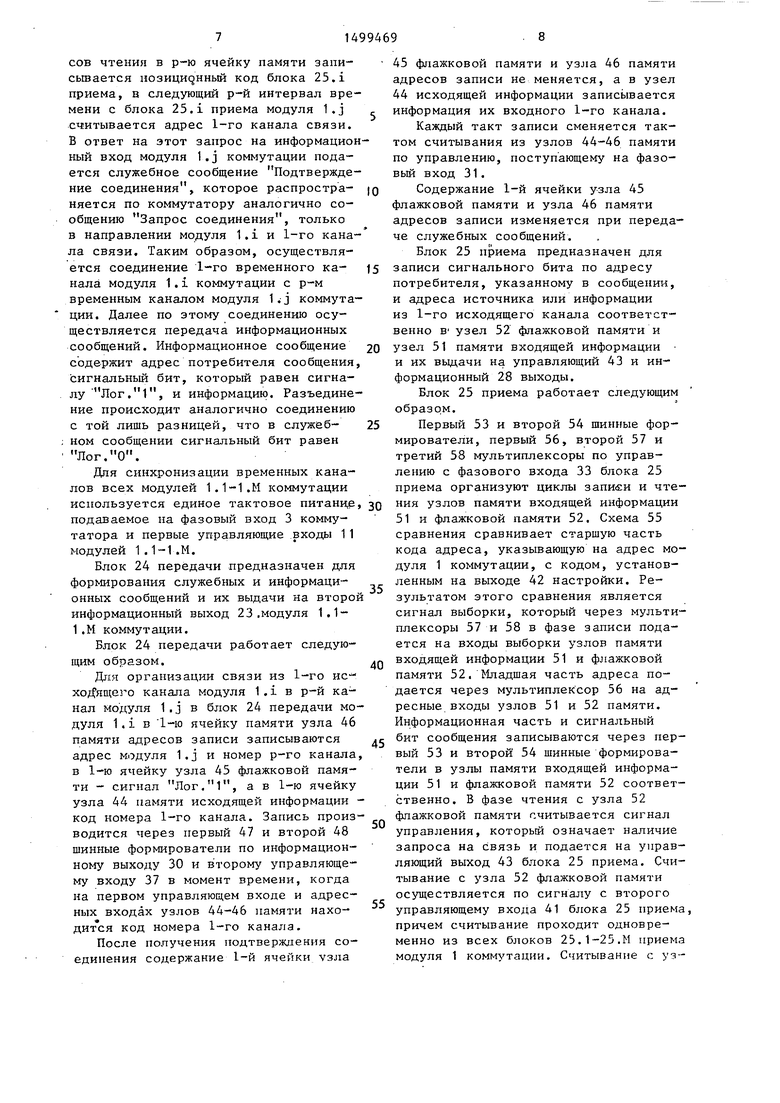

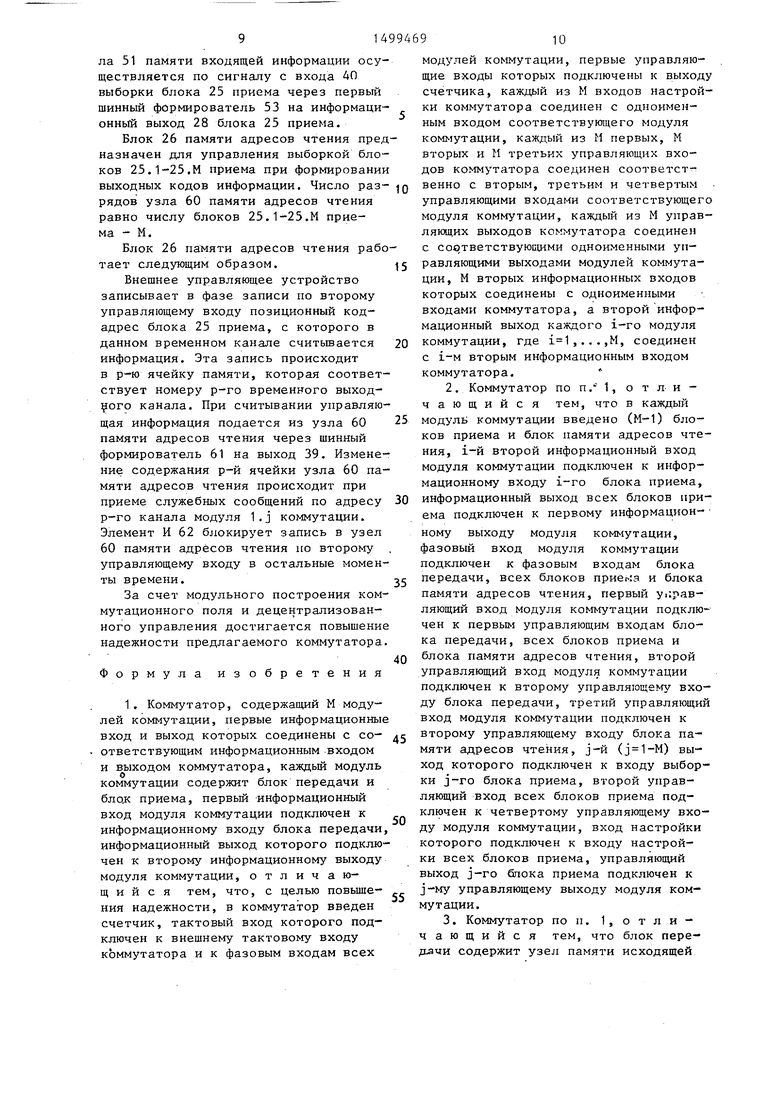

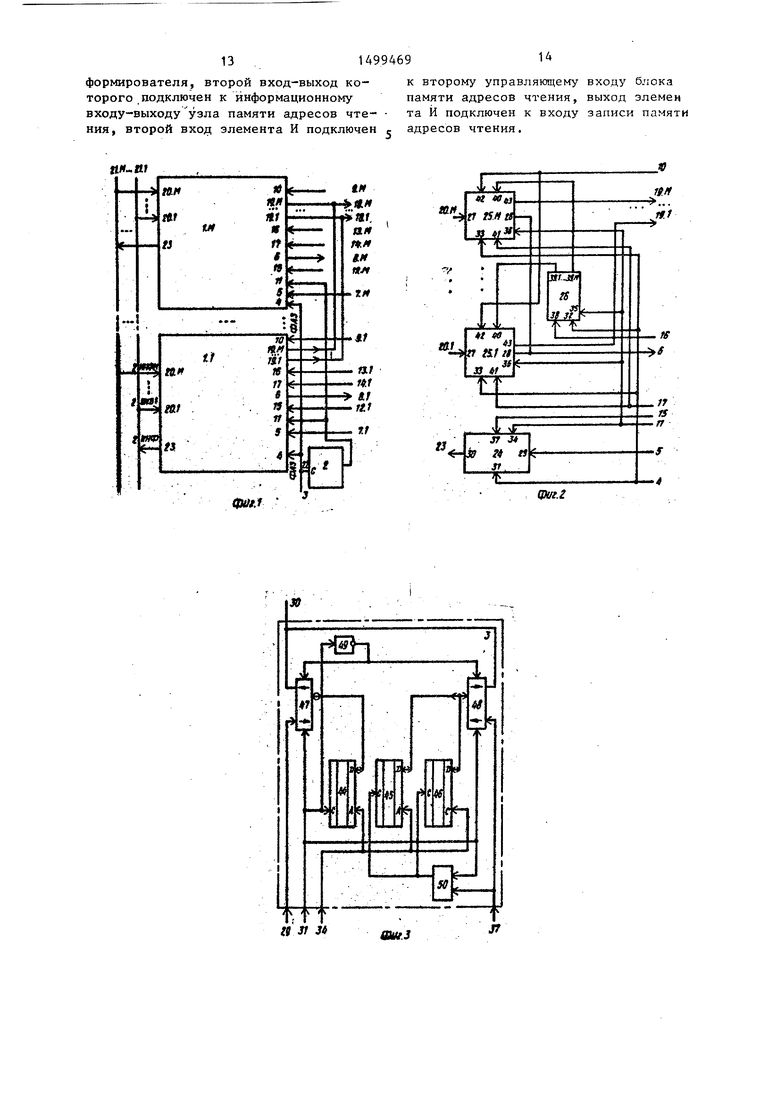

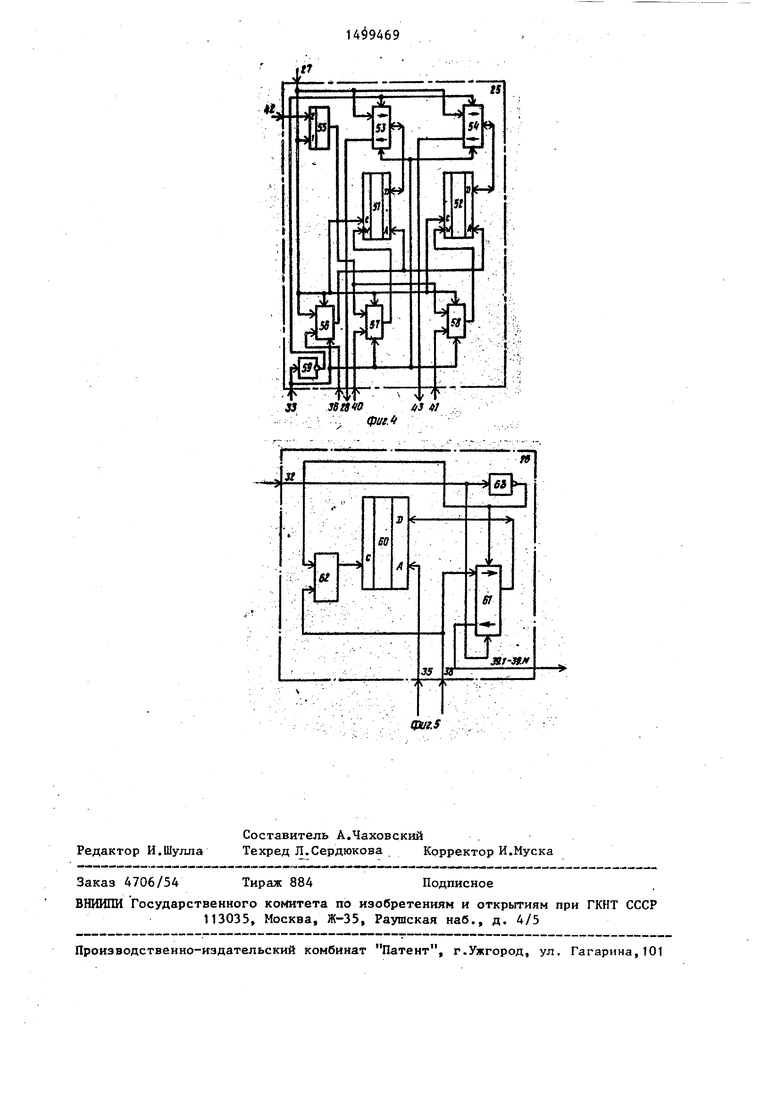

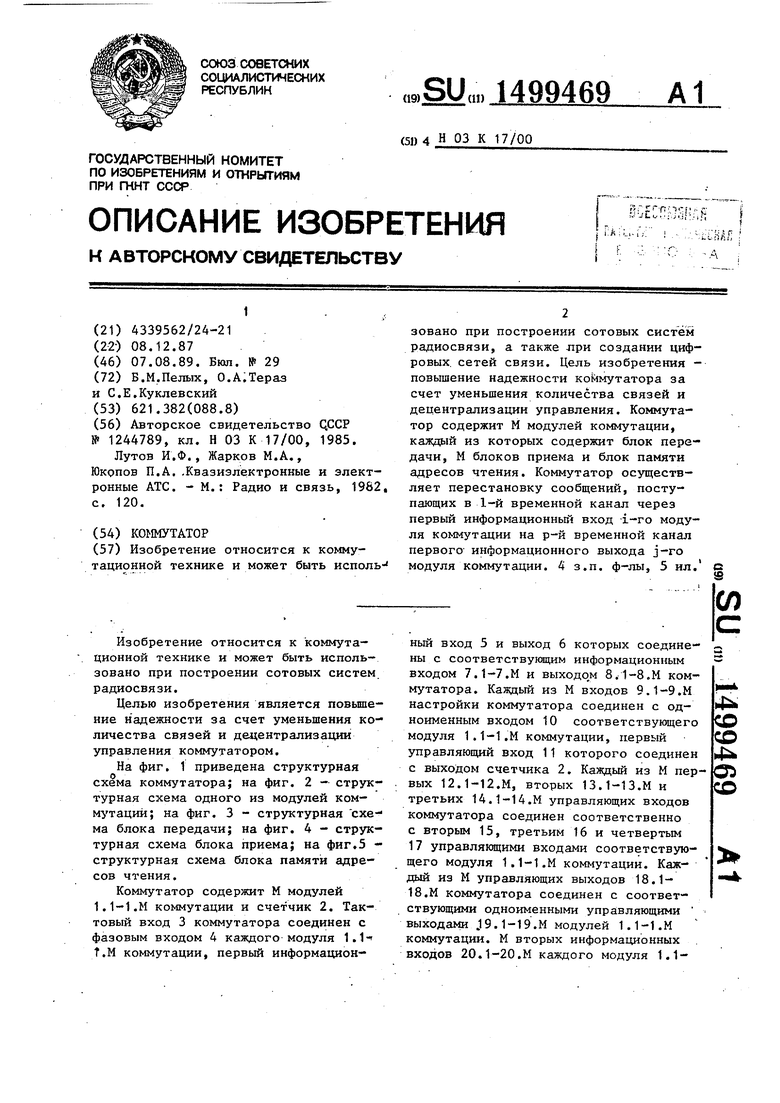

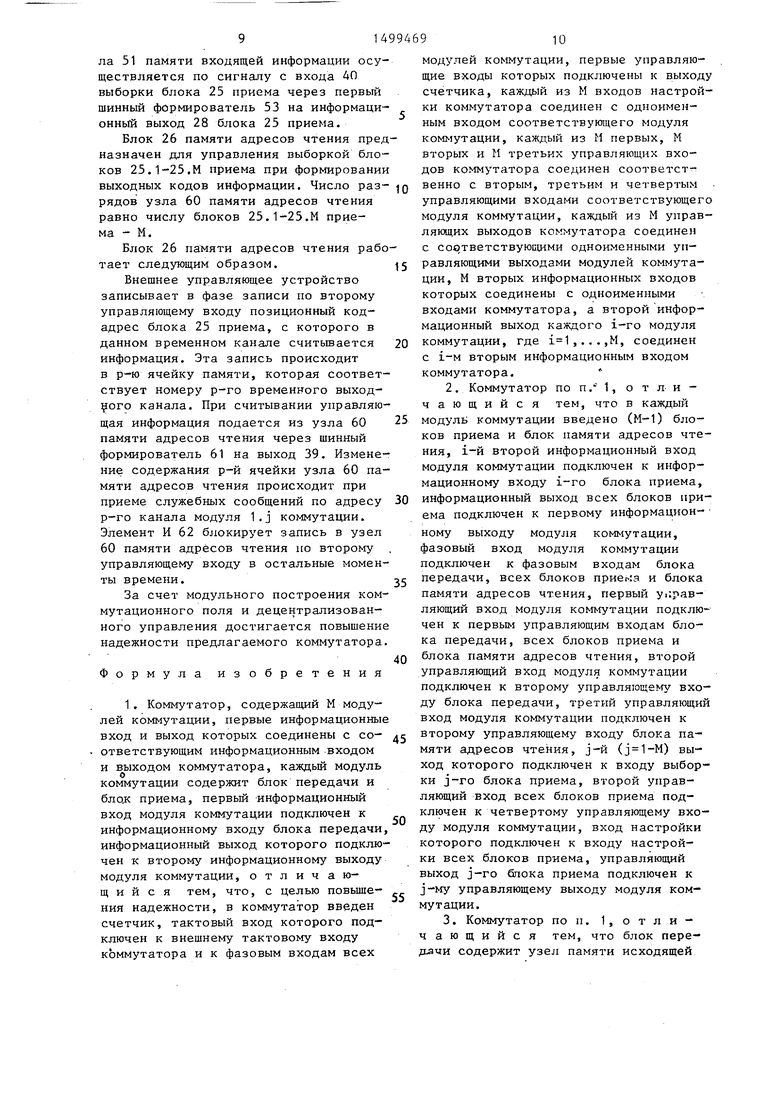

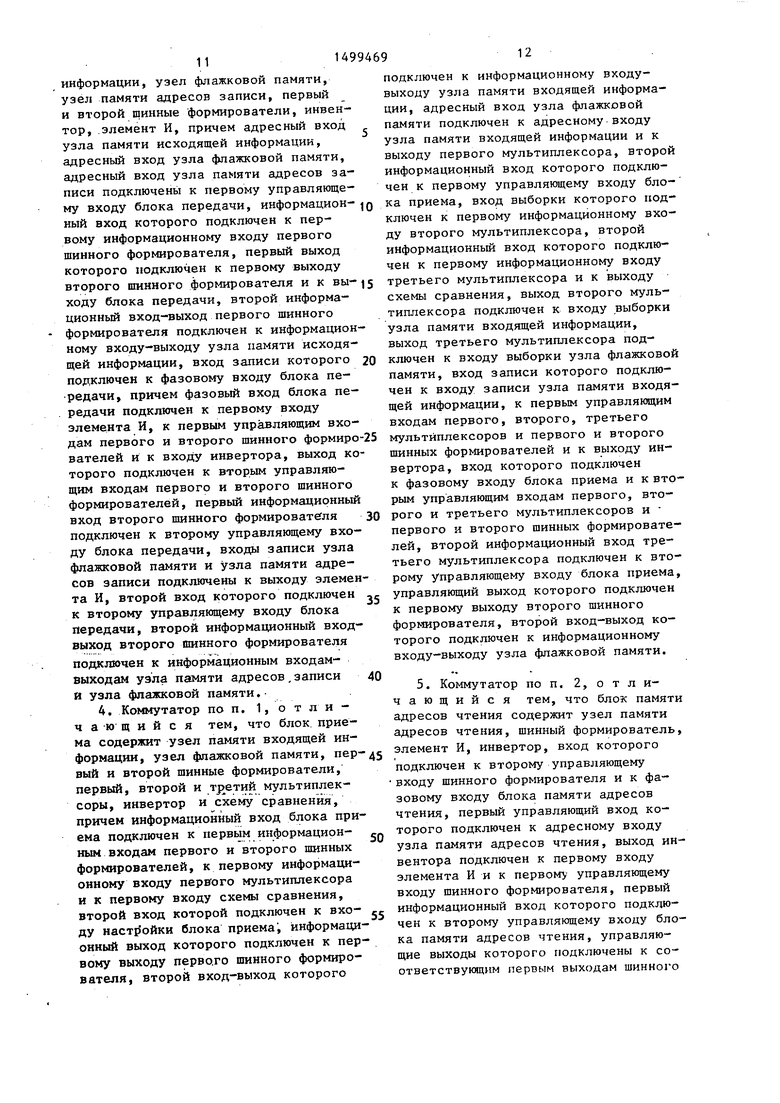

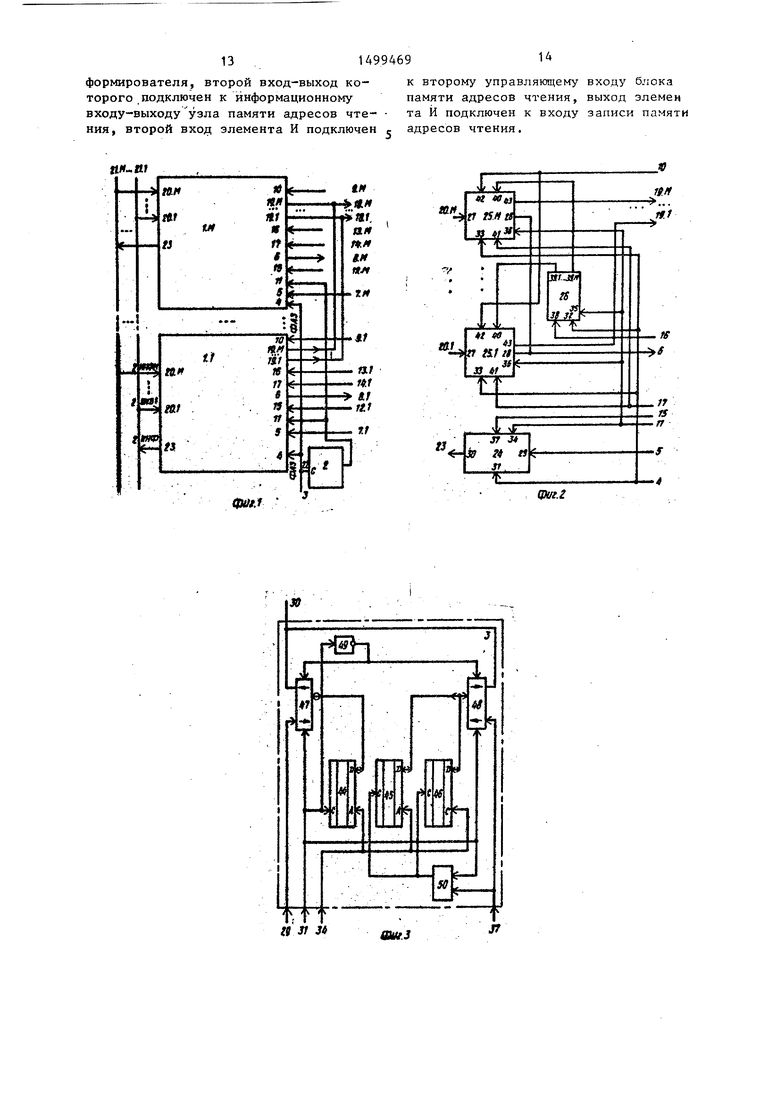

На фиг. 1 приведена структурная схема коммутатора; на фиг. 2 - структурная схема одного из модулей коммутации; на фиг. 3 - структурная схема блока передачи; на фиг. 4 - структурная схема блока приема; на фиг.5 - структурная схема блока памяти адресов чтения.

Коммутатор содержит М модулей 1.1-1.М коммутации и счетчик 2. Тактовый вход 3 коммутатора соединен с фазовым входом 4 каждого модуля I.I- t.M коммутации, первый информационный вход 5 и выход 6 которых соединены с соответствующим информационным входом 7.1-7.М и выходо,м 8.1-8.М коммутатора. Кавдый из М входов 9.1-9.М настройки коммутатора соединен с одноименным входом 10 соответствующего модуля 1.1-1.М коммутации, первый управляющий вход 11 которого соединен с выходом счетчика 2. Каждый из М первых 12.1-12.М, вторых 13.1-13.М и третьих 14.1-14.М управляющих входов коммутатора соединен соответственно с вторым 15, третьим 16 и четвертым 17 управляющими входами соответствующего модуля 1.1-1.М коммутации. Каждый из М управляющих выходов 18.1- 18.М коммутатора соединен с соответствующими одноименными управляющими выходами J9.1-19.M модулей 1.1-1.М коммутации. М вторых информационных входов 20.1-20.М каждого модуля 1.14 СО СО 4 О5

СО

1.N коммутации соединены с соответствующими одноименными входами 21.1- 21.М коммутатора, тактовый вход 3 коммутатора соединен с тактовым входом 22 счетчика 2, а второй информационный выход 23 каждого i-ro модуля 1.1-1.М коммутации соединен с i-м вторым информационным входом 21.1- 21.М коммутатора.

Каждый модуль 1.1-1.М коммутации (фиг. 2) содержит блок 24 передачи, М блоков 25.1-25,М приема, блок 26 памяти адресов чтения, причем i-й

второй информационный вход 20.1-20.М 5 шинного формирователя 47 подключен модуля 1 подключен к информационному к информационному входу-выходу уз- входу 27 -го блока 25.1-25.М приема, ла 44 памяти исходящей информации.

информационные выходы 28 которых подключены к первому информационному выходу 6 модул;| коммутации, первый информационный вход 5 которого подг ключен к информационному входу 29 блока 24 передачи, информационный выход 30 которого подключен к второ- му информационному выходу 23 модуля 1 коммутации, Фазовый вход 4 модуля 1 коммутации подключен к фазовым входам 31 - 33 блока 24 передачи, блока 26 памяти адфазовый вход 31 блока 24 передачи подключен к входу записи узла 44 па

20 мяти исходящей информации, первому входу элемента И 50, первым управля щим входам первого 47 и второго 48 шинных формирователей и входу инвер тора 49,, выход которого подключен к

25 вторым управляющим входам первого 4 и второго 48 щинных формирователей, второй управляющий вход, -37 блока 24 передачи подключен к второму входу элемента И 50, выход которого под25 вторым управляющим входам первого 47 и второго 48 щинных формирователей, второй управляющий вход, -37 блока 24 передачи подключен к второму входу элемента И 50, выход которого подресов чтения и всех блоков 25.1-25л,М ЗО ключен к входам записи узла 45 флаж40

приема, первый управлякяций вход 11 модуля 1 коммутации подключен к первому управляющему входу 34 блока 24 передачи, входу 35 блока 26 памяФи адресов чтения, входу 36 всех блоков 25,1-25.М приема, второй управляющий вход 15 1А)дуля 1 коммутации подключен к второму управляющему входу 37 блока 24 передачи, третий управляющий вход 16 модуля 1 коммутации подключен К второму управляющему входу 38 блока 26 памяти адресов чтения, j-й () выход 39.1-39.М которого подключен к входу 40 выбор- ки j-ro блока 25 приема, четвертый управляющий вход 17 модуля 1 коммутации подключен к вторым управляющим входам 41 всех блоков 25.1-25.М приема, а вход 10 настройки модуля 1 коммутации подключен к входам 42 настройки всех блоков 25.1-25.М приема, 50 управлякяций выход 43 i-ro блока.25.1- 25.М приема подкл50чён к i-му управляющему выходу 19.1-19.М модуля 1 коммутации.

Блок 24 передачи (фиг. 3) содержит 44 памяти исходящей информации, узел 45 флажковой памяти, узел 46 памяти адресов записи, перковой памяти и узла 46 памяти адресов записи, а также к первому входу втброго шинного формирователя 48, первый выход которого подключен к ин35 Формационному выходу 30 блока 24 передачи, а второй вход-выход подключен -к информационному входу-выходу узла 45 флажковой памяти и узла 46 памяти адресов записи.

Блок 25 приёма (фиг. 4) содержит узел 51 памяти входящей информации, узел 52 флажковой памяти, первый 53 и второй 54 шинные формирователи, схему 55 сравнения, первый 56, второй

д5 57 и третий 58 мультиплексоры и инвертор 59, причем информационный вход 27 блока 25 приема подключен к первому информационному входу первого 53 и второго 54 шинных формирователей, к первому информационному входу первого мультиплексора 56 и к первому входу схемы 55 сравнения, второй вход которого подключен к входу 42 настрой ки блока 25 приема, информационный выход 28 которого подключен к первому выходу первого шинного формирователя 53, второй вход-выход которого подключен к информационным входам-выходам узла 51 памяти входящей информа55

вый 47 и второй 48 шинные формирователи, инвертор 49, элемент И 50, причем первый управляющий вход 34 блока 24 передачи подключен к адресным входам узла 44 памяти исходящей информации, узла 45 флажковой памяти, узла 46 памяти адресов записи, информационные вход 29 блока 24 передачи подключен к информационному входу первого шинного формирователя 47, первый выход которого подключен к информационному выходу 30 блока 24 передачи, второй вход-выход первого

фазовый вход 31 блока 24 передачи подключен к входу записи узла 44 па мяти исходящей информации, первому входу элемента И 50, первым управляющим входам первого 47 и второго 48 шинных формирователей и входу инвертора 49,, выход которого подключен к

вторым управляющим входам первого 47 и второго 48 щинных формирователей, второй управляющий вход, -37 блока 24 передачи подключен к второму входу элемента И 50, выход которого подключен к входам записи узла 45 флаж0

0

ковой памяти и узла 46 памяти адресов записи, а также к первому входу втброго шинного формирователя 48, первый выход которого подключен к ин5 Формационному выходу 30 блока 24 передачи, а второй вход-выход подключен -к информационному входу-выходу узла 45 флажковой памяти и узла 46 памяти адресов записи.

Блок 25 приёма (фиг. 4) содержит узел 51 памяти входящей информации, узел 52 флажковой памяти, первый 53 и второй 54 шинные формирователи, схему 55 сравнения, первый 56, второй

5 57 и третий 58 мультиплексоры и инвертор 59, причем информационный вход 27 блока 25 приема подключен к первому информационному входу первого 53 и второго 54 шинных формирователей, к первому информационному входу первого мультиплексора 56 и к первому входу схемы 55 сравнения, второй вход которого подключен к входу 42 настройки блока 25 приема, информационный выход 28 которого подключен к первому выходу первого шинного формирователя 53, второй вход-выход которого подключен к информационным входам-выходам узла 51 памяти входящей информа5

ции, адресный вход узла 52 флажковой памяти подключен к адресному входу узла 51 памяти входящей информации и к выходу первого мультиплек- г сора 56, второй информационный вход которого подключен к первому управляющему входу 36 блока 25 приема, вход 40 выборки которого подключен к первому информационному входу муль- 10 типлёксора 57, второй информационный вход которого подключен к первому информационному входу третьего мультиплексора 58 и к выходу схемы 55 сравнения, выход второго мультиплексора 57 подключен к входу выборки узла 51 памяти входящей информации, выход третьего мультиплексора 58 подключен к входу выборки узла 52 флажковой памяти, вход записи которого подключен к входу записи узла 51 памяти входящей информации, к первым управляющим входам первого 58, второго 57 и третьего 58 мультиплексоров, первого 53 и второго 54 шинных формирователей и к выходу инвертора 59, вход которого подключен к фазовому входу 33 блока 25 приема, к вторым управляющим входам первого 56, второго 57 и третьего 58 мультиплексоров, первого 53 и второго 54 шинных формирователей, второй информационный вход третьего мультиплексора 58 подключен к второму управляюключены к первому выходу шинного формирователя 61, второй вход-выход которого подключен к информационному входу-выходу узла 60 памяти адресов чтения, второй вход элемента И 62 подключен к втором управляющему входу 38 блока 26 памяти адресов чтения выход элемента И 62 подключен к входу записи узла 60 памяти адресов чтения.

Коммутатор осуществляет перестановку сообщений, поступающих в 1-й временный канал через первый инфор15 мационный вход i-ro модуля 1 коммутации, на р-й временный канал первого информационного выхода j-ro модуля 1 коммутации (1,, ,M, где N - число временных каналов связи,

20 обслуживаемых одним модулем 1 коммутации; М - число модулей 1 коммутации) .

Для коммутации входных и выходных каналов применено четыре типа служеб25 ных сообщений: Запрос соединения ; Подтверждение соединения ; Запрос разъединения ; Подтверждение разъединения .

Структура всех этих сообщений одинаковая. Они содержат адрес потребителя сообщения, источника сообщения и сигнальный бит. При этом в сообщениях Запрос соединения и Подтверждение соединения сигнальный бит ин30

щему входу 41 блока 25 приема, управ- Формации равен Лог,1, а в сообще- ляющий выход 43 которого подключен - -

ниях Запрос разъединения и Подтверждение разъединения сигнальный бит информации равен Лог.О. Адреса источника и потребителя состоят из адресов модулей 1.1-1.М коммутации и номеров каналов, обслуж тваемых этими модулями.

к первому выходу второго шинного формирователя 54, второй вход-выход которого подключен к информационному входу-выходу узла 52 флажковой па- мяти..

Блок 26 памяти адресов чтения (фиг. 5) содержит узел 60 памяти адресов чтения, шинный формирователь 61, элемент Н 62, инвентор 63, вход которого подключен к второму управляющему входу шинного формирователя 61 и фазовому входу 32 блока 26 памяти адресов чтения, первый управляющий вход 35 которого подключен к адресному входу узла 60 памяти адресов чтения, выход инвентора 63 подключен к первому входу элемента И 62 и к первому управляющему входу шинного формирователя 61, первый информационный вход которого подключен к второму управляющему входу 38 блока 26 памяти адресов чтения, управляющие выходы 39.1-39.М которого под

ключены к первому выходу шинного формирователя 61, второй вход-выход которого подключен к информационному входу-выходу узла 60 памяти адресов чтения, второй вход элемента И 62 подключен к втором управляющему входу 38 блока 26 памяти адресов чтения, выход элемента И 62 подключен к входу записи узла 60 памяти адресов чте. ния.

Коммутатор осуществляет перестановку сообщений, поступающих в 1-й временный канал через первый информационный вход i-ro модуля 1 коммутации, на р-й временный канал первого информационного выхода j-ro модуля 1 коммутации (1,, ,M, где N - число временных каналов связи,

обслуживаемых одним модулем 1 коммутации; М - число модулей 1 коммутации) .

Для коммутации входных и выходных каналов применено четыре типа служебных сообщений: Запрос соединения ; Подтверждение соединения ; Запрос разъединения ; Подтверждение разъединения .

Структура всех этих сообщений одинаковая. Они содержат адрес потребителя сообщения, источника сообщения и сигнальный бит. При этом в сообщениях Запрос соединения и Подтверждение соединения сигнальный бит ин

Формации равен Лог,1, а в сообще- - -

5

О

0

5

ниях Запрос разъединения и Подтверждение разъединения сигнальный бит информации равен Лог.О. Адреса источника и потребителя состоят из адресов модулей 1.1-1.М коммутации и номеров каналов, обслуж тваемых этими модулями.

Коммутатор работает следующим образом.

Через первый информационный вход 5 . модуля 1.i коммутации подается сообщение Запрос на связь для р-го канала модуля I.J. Это сообщение записывается в блок 24 передачи в ячейку памяти под номером 1. Б 1-м интервале времени часть этого сообщения: адрес источника и сигнальный бит перепишется в р-ю ячейку плмяти блока 25.1 приема модуля l.j коммутации. В р-м временном интервале на управляющий выход 19.1 модуля 1.J с блока 25,1 приема поступает значение Лог. М сигнального бита. Через второй управляющий вход 38 в блок 26 памяти адресов чтения в р-ю ячейку памяти запи- сьтается позиционный код блока 25.1 приема, в следующий р-й интервал времени с блока 25.1 приема модуля 1.j считывается адрес 1-го канала связи. В ответ на этот запрос на информационный вход модуля 1.J коммутации подается служебное сообщение Подтверждение соединения, которое распространяется по коммутатору аналогично сообщению Запрос соединения, только в направлении модуля 1.1 и 1-го канала связи. Таким образом, осуществляется соединение 1-го временного канала модуля 1.i коммутации с р-м временным каналом модуля l.j коммутации. Далее по этому соединению осуществляется передача информационных сообщений. Информационное сообщение содержит адрес потребителя сообщения, сигнальный бит, который равен сигналу .1, и информацию. Разъединение происходит аналогично соединению с той лишь разницей, что в служебном сообщении сигнальный бит равен Лог.О.

Для синхронизации временных каналов всех модулей 1.1-1.М коммутации используется единое тактовое питание подаваемое на фазовый вход 3 коммутатора и первые управляющие входы 11 модулей 1.1-1.М.

Блок 24 передачи предназначен для формирования служебных и информационных сообщений и их выдачи на второй информационный выход 23 .модуля 1.1- 1.М коммутации.

Блок 24 передачи работает следующим образом.

Для организации связи из 1-го ис-- xorfяй ero канала модуля 1 .1 в р-й канал модуля 1.J в блок 24 передачи модуля 1.i в 1-ю ячейку памяти узла 46 памяти адресов записи записываются адрес модуля l.j и номер р-го канала в 1-ю ячейку узла 45 флажковой памяти - сигнал Лог.1, а в 1-ю ячейку узла 44 памяти исходящей информации - код номера 1-го канала. Запись производится через первый 47 и второй 48 шинные формирователи по информационному выходу 30 и в торому управляющему входу 37 в момент времени, когда на первом управляющем входе и адресных входах узлов 44-46 памяти находится код номера 1-го канала.

После получения подтверждения соединения содержание 1-й ячейки узла

0

5

0

5

0

5

0

5

45 флажковой памяти и узла 46 памяти адресов записи не меняется, а в узел 44 исходящей информации записывается информация их входного 1-го канала.

Каждый такт записи сменяется тактом считывания из узлов 44-46 памяти по управлению, поступающему на фазовый вход 31.

Содержание 1-й ячейки узла 45 флажковой памяти и узла 46 памяти адресов записи изменяется при передаче служебных сообщений.

Блок 25 приема предназначен для записи сигнального бита по адресу потребителя, указанному в сообщении, и адреса источника или информации из 1-го исходящего канала соответственно В узел 52 флажковой памяти и узел 51 памяти входящей информации и их вьщачи на управляющий 43 и информационный 28 выходы.

Блок 25 приема работает следующим образо.м.

Первый 53 и второй 54 шинные формирователи, первый 56, второй 57 и третий 58 мультиплексоры по управлению с фазового входа 33 блока 25 приема организуют циклы записи и чтения узлов памяти входящей информации 51 и флажковой памяти 52. Схема 55 сравнения сравнивает старшую часть кода адреса, указывающую на адрес модуля 1 коммутации, с кодом, установленным на выходе 42 настройки. Результатом этого сравнения является сигнал выборки, который через мультиплексоры 57 и 58 в фазе записи подается на входы выборки узлов памяти входящей информации 51 и флажковой памяти 52,Младшая часть адреса подается через мультиплексор 56 на адресные входы узлов 51 и 52 памяти. Информационная часть и сигнальный бит сообщения записываются через первый 53 и второй 54 шинные формирователи в узлы памяти входящей информации 51 и флажковой памяти 52 соответственно. В фазе чтения с узла 52 флажковой памяти считывается сигнал управления, который означает наличие запроса на связь и подается на управляющий выход 43 блока 25 приема. Считывание с узла 52 флажковой памяти осуществляется по сигналу с второго управляющему входа 41 блока 25 приема, причем считывание проходит одновременно из всех блоков 25.1-25.М приема модуля 1 коммутации. Считывание с узла 51 памяти входящей информации осуществляется по сигналу с входа 4П выборки блока 25 приема через первый шинный формирователь 53 на информаци- онный выход 28 блока 25 приема.

Блок 26 памяти адресов чтения предназначен для управления выборкой блоков 25.1-25.М приема при формировании

модулей коммутации, первые управляющие входы которых подключены к выходу счетчика, каждый из М входов настройки коммутатора соединен с одноименным входом соответствующего модуля коммутации, каждый из М первых, М вторых и М третьих управляющих входов коммутатора соединен соответст

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| РАДИОКОМПЛЕКС ЭКСТРЕННОЙ МЕДИЦИНСКОЙ ПОМОЩИ | 2006 |

|

RU2329606C2 |

| КОММУТАТОР LINK-ПОРТОВ | 2009 |

|

RU2405196C1 |

| Устройство для обмена данными между процессорами | 1985 |

|

SU1277127A1 |

| Устройство для сопряжения внешних устройств с общей памятью | 1985 |

|

SU1297069A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Модульная многоуровневая система коммутации процессоров | 1984 |

|

SU1249524A1 |

Изобретение относится к коммутационной технике и может быть использовано при построении сотовых систем радиосвязи, а также при создании цифровых сетей связи. Цель изобретения - повышение надежности коммутатора за счет уменьшения количества связей и децентрализации управления. Коммутатор содержит M модулей коммутации, каждый из которых содержит блок передачи, M блоков приема и блок памяти адресов чтения. Коммутатор осуществляет перестановку сообщений, поступающих в L - й временной канал через первый информационный вход I - го модуля коммутации на P - й временной канал первого информационного выхода J - го модуля коммутации. 5 ил.

выходных кодов информации. Число раз- Q венно с вторым, третьим и четвертым рядов узла 60 памяти адресов чтения равно числу блоков 25.1-25.М приема - М.

Блок 26 памяти адресов чтения рабоуправляющими входами соответствующег модуля коммутации, каждый из М управ ляющих выходов коммутатора соединен с соответствуюшлми одноименными управляющими выходами модулей коммутации, М вторых информационных входов которых соединены с одноименными входами коммутатора, а второй информационный выход каждого i-ro модуля коммутации, где ,...,М, соединен с i-M вторым информационным входом коммутатора.

тает следующим образом.

Внешнее управляющее устройство записывает в фазе записи по второму управляющему входу позиционный код- адрес блока 25 приема, с которого в данном временном канале считьшается информация. Эта запись происходит в р-ю ячейку памяти, которая соответствует номеру р-го временного выход- сго канала. При считывании управляющая информация подается из узла 60 памяти адресов чтения через шинный формирователь 61 на выход 39. Изменение содержания р-й ячейки узла 60 памяти адресов чтения происходит при приеме служебных сообщений по адресу р-го канала модуля 1,j коммутации. Элемент И 62 блокирует запись в узел 60 памяти адресов чтения по второму управляющему входу в остальные моменты времени.

За счет модульного построения коммутационного поля и децентрализованного управления достигается повышение надежности предлагаемого коммутатора.

Формула изобретения

Q венно с вторым, третьим и четвертым

5

0 5 0 5

0

5

0

5

управляющими входами соответствующего модуля коммутации, каждый из М управляющих выходов коммутатора соединен с соответствуюшлми одноименными управляющими выходами модулей коммутации, М вторых информационных входов которых соединены с одноименными входами коммутатора, а второй информационный выход каждого i-ro модуля коммутации, где ,...,М, соединен с i-M вторым информационным входом коммутатора.

111499469

информации, узел флажковой памяти, узел памяти адресов записи, первый и второй шинные формирователи, инвен- тор, .элемент И, причем адресный вход узла памяти исходящей информации, адресный вход узла флаткковой памяти, адресный вход узла памяти адресов записи подключены к первому управляющему входу блока передачи, информацион- Q ка приема, вход выборки которого йодный вход которого подключен к первому информационному входу первого щинного формирователя, первый выход которого подключен к первому выходу второго шинного формирователя и к вы-|5 ходу блока передачи, второй информационный вход-выход первого шинного формирователя подключен к информационному входу-выходу узла памяти исходящей информации, вход записи которого 20 подключен к фазовому входу блока передачи, причем фазовый вход блока передачи подключен к первому входу элемента И, к первым управляющим входам первого и второго шинного формиро-25 вателей и к входу инвертора, выход которого подключен к вторым управляющим входам первого и второго шинного формирователей, первый информационный вход второго шинного формироватеГля 30 подключен к второму управляющему входу блока передачи, входы записи узла флажковой памяти и узла памяти адресов записи подключены к выходу элемента И, второй вход которого подключен к второму управляющему входу блока передачи, второй информационный вход- выход второго шинного формирователя подключен к информационным входам- выходам узла па1мяти адресов . записи и узла флажковой памяти.

35

40

50

55

ключен к первому информационному входу второго мультиплексора, второй информационный вход которого подключен к первому информационному входу третьего мультиплексора и к выходу схемы сравнения, выход второго мультиплексора подключен к входу выборки узла памяти входящей информации, выход третьего мультиплексора подключен к входу выборки узла флажковой памяти, вход записи которого подключен к входу записи узла памяти входящей информации, к первым управляющим входам первого, второго, третьего мультиплексоров и первого и второго щинных формирователей и к выходу инвертора, вход которого подключен к фазовому входу блока приема и к вторым управляющим входам первого, второго и третьего мультиплексоров и первого и второго шинных формирователей, второй информационный вход третьего мультиплексора подключен к второму управляющему входу блока приема, управляющий выход которого подключен к первому выходу второго шинного формирователя, второй вход-выход которого подключен к информационному входу-выходу узла флажковой памяти.

12

подключен к информационному входу- выходу узла памяти входящей информации, адресный вход узла флажковой памяти подключен к адресному входу узла памяти входящей информации и к выходу первого мультиплексора, второй информационный вход которого подключен к первому управляющему входу бло-

Q ка приема, вход выборки которого йод505 05

5

0

0

5

ключен к первому информационному входу второго мультиплексора, второй информационный вход которого подключен к первому информационному входу третьего мультиплексора и к выходу схемы сравнения, выход второго мультиплексора подключен к входу выборки узла памяти входящей информации, выход третьего мультиплексора подключен к входу выборки узла флажковой памяти, вход записи которого подключен к входу записи узла памяти входящей информации, к первым управляющим входам первого, второго, третьего мультиплексоров и первого и второго щинных формирователей и к выходу инвертора, вход которого подключен к фазовому входу блока приема и к вторым управляющим входам первого, второго и третьего мультиплексоров и первого и второго шинных формирователей, второй информационный вход третьего мультиплексора подключен к второму управляющему входу блока приема, управляющий выход которого подключен к первому выходу второго шинного формирователя, второй вход-выход которого подключен к информационному входу-выходу узла флажковой памяти.

131499469U

формирователя, второй вход-выход ко-к второму управляющему входу блока

торого .подключен к информационномупамяти адресов чтения, выход элемен

входу-выходу узла памяти адресов чте- -та И подключен к входу записи памяти

ния, второй вход элемента И подключен садресов чтения.

«

Э

19 31 36

«в

t Hi

«

r(

ани.з

JT

Т Т

33 Уба«о ii3 Di

. . фигЛ

X

да

ЯТ-ЗЛМ

| Коммутирующее устройство для многопроцессорной вычислительной системы | 1985 |

|

SU1244789A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Лутов И.Ф., Жарков М.А., Юкопов П.А | |||

| .Квазиэлектронные и электронные АТС | |||

| - М.: Радио и связь, 1982, с | |||

| Кровля из глиняных обожженных плит с арматурой из проволочной сетки | 1921 |

|

SU120A1 |

Авторы

Даты

1989-08-07—Публикация

1987-12-08—Подача