112

Изобретение относится к вьмисли- тельной технике, в частности, к устройствам связи между процессорами, и может быть использовано в многопроцессорных системах., предназначенных для решения итерационными методами систем алгебраических, дифференциаль Hbix, интегральных уравнений и уравнений в частных производных, когда возникает необходимость в быстром обмене данными между всеми процессорами на каждом шаге итерации.

Целью изобретения является увеличение быстродействия.

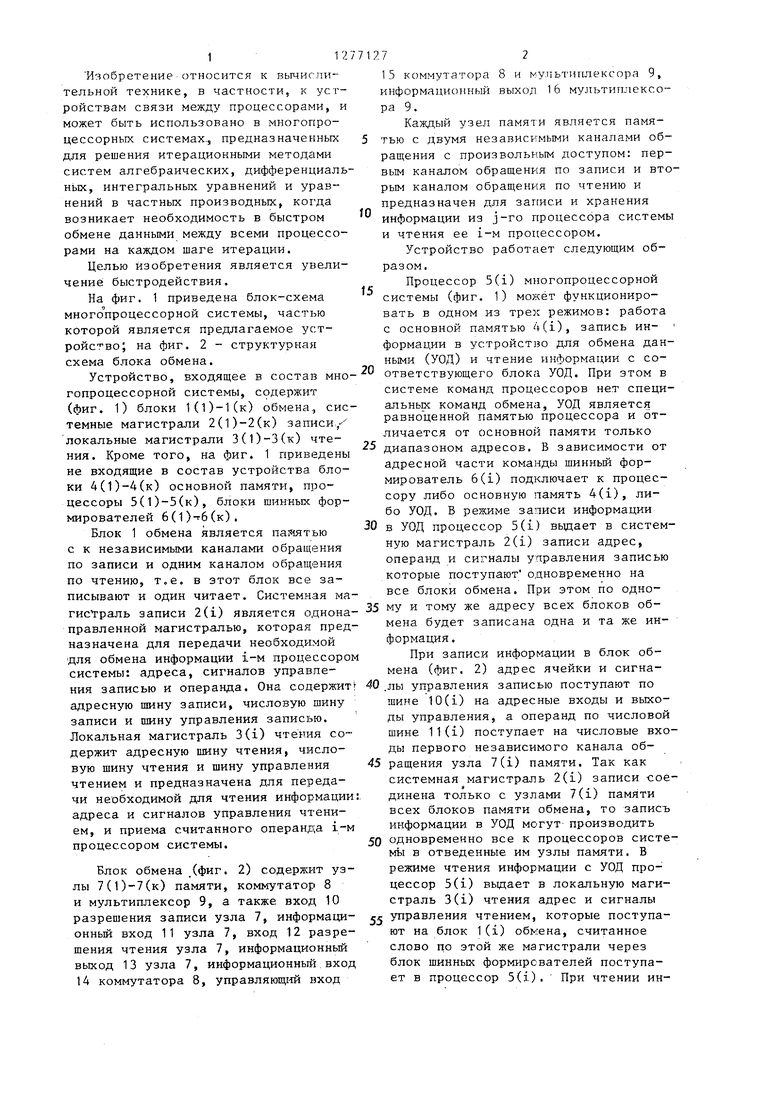

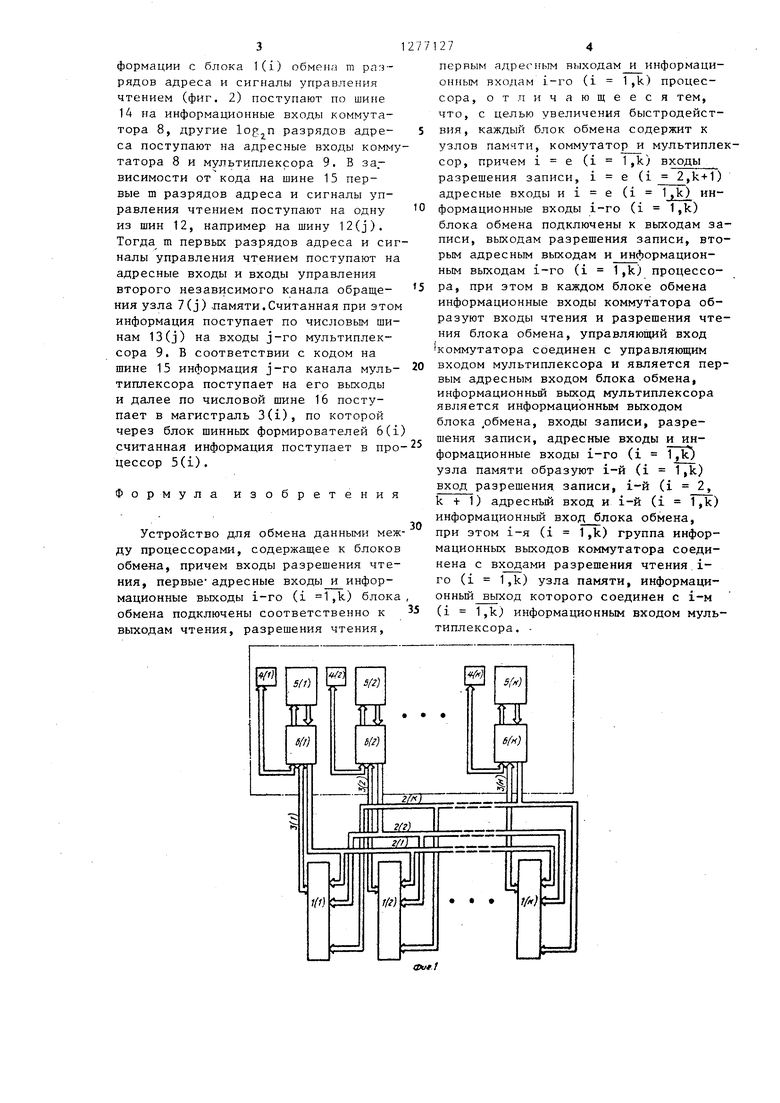

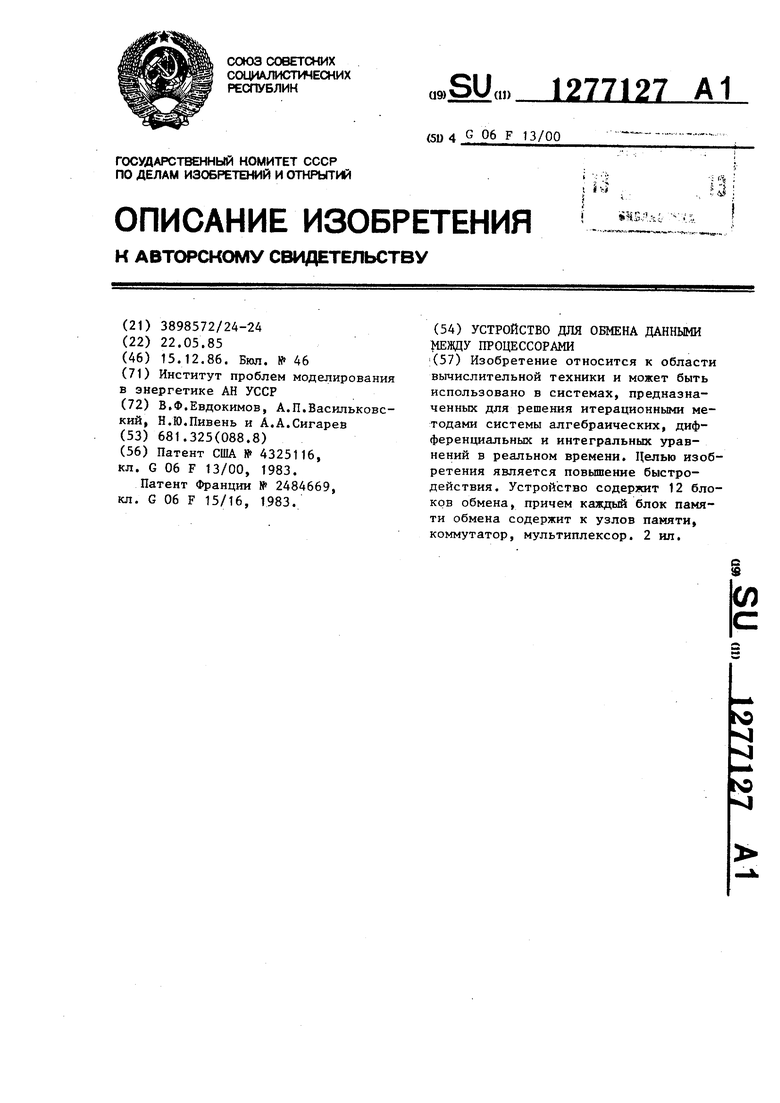

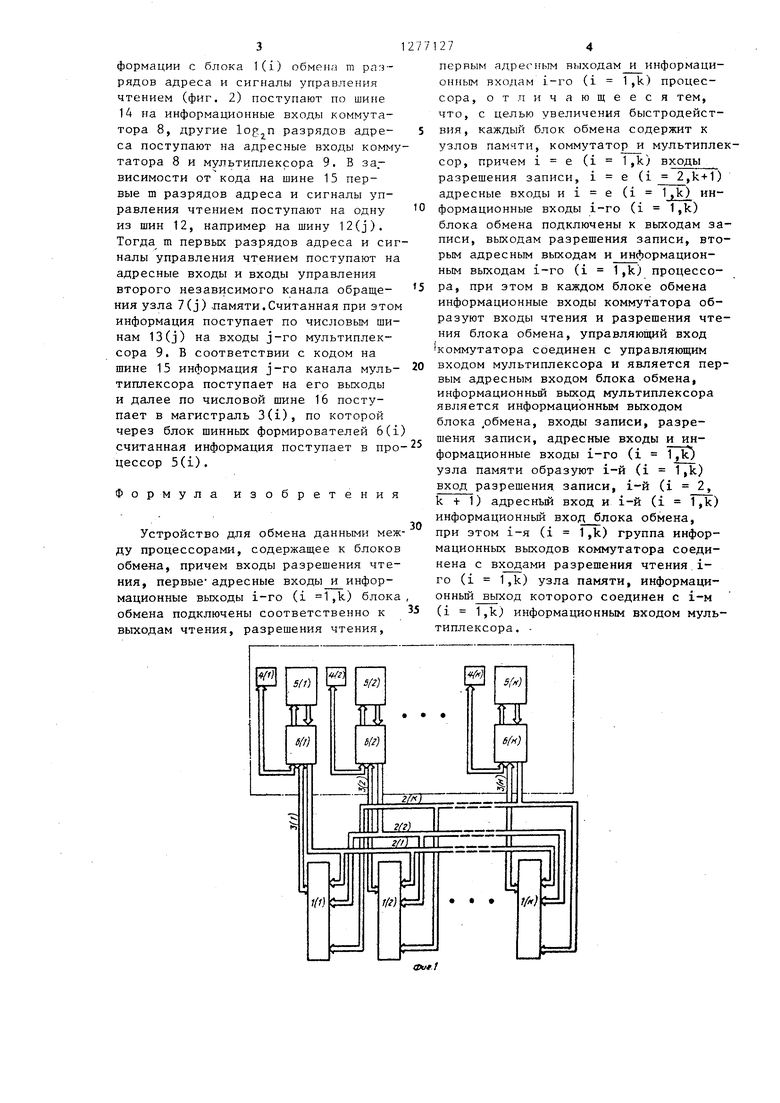

На фиг. 1 приведена блок-схема многопроцессорной системы, частью которой является предлагаемое устройство; на фиг. 2 - структурная схема блока обмена.

Устройство, входящее в состав многопроцессорной системы, содержит (фиг. 1) блоки 1(1)-1(к) обмена, системные магистрали 2(1)-2(к) записи,-- локальные магистрали 3(1)-3(к) чтения. Кроме того, на фиг. 1 гфиведены не входящие в состав устройства блоки 4(1)-4(к) основной памяти, процессоры 5(1)-5(к), блоки шинных формирователей 6(1)-г6(к).

Блок 1 обмена является паяятью с к независимыми каналами обращения по записи и одним каналом обращения по чтению, т.е. в этот блок все записывают и один читает. Системная магистраль записи 2(1) является однонаправленной магистралью, которая предназначена для передачи необходимой ДЛЯ обмена информации i-м процессоро системы: адреса, сигналов управления записью и операнда. Она содержит адресную шину записи, числовую шину записи и шину управления записью. Локальная магистраль 3(1) чтения содержит адресную шину чтения, числовую шину чтения и шину управления чтением и предназначена для передачи необходимой для чтения информации адреса и сигналов управления чтением, и приема считанного операнда 1-м процессором системы.

Блок обмена (фиг. 2) содержит узлы 7(1)-7(к) памяти, коммутатор 8 и мультиплексор 9, а также вход 10 разрешения записи узла 7, информационный вход 11 узла 7, вход 12 разрешения чтения узла 7, информационньш выход 13 узла 7, информационньш вход 14 коммутатора 8, управляющий вход

1272

15 коммутатора 8 и му.пьтиплексора 9, информационный выхол 16 мультиплексора 9.

Каждый узел памяти является памя- тью с двумя независимыми каналами обращения с произвольным доступом: первым каналом обращения по записи и вторым каналом обращения по чтению и предназначен для записи и хранения информации из j-ro процессора системы и чтения ее i-м процессором.

Устройство работает следующим образом.

Процессор 5(1) многопроцессорной системы (фиг. 1) может функционировать в одном из трех режимов: работа с основной памятью 4(1), запись ий- формации в устройство для обмена данными (УОД) и чтение информации с со- 0 ответствующего блока УОД. При зтом в системе команд процессоров не.т специальньк команд обмена, УОД является равноценной памятью процессора и отличается от основной памяти только

5 диапазоном адресов. В зависимости от адресной части команды шинньш формирователь 6(1) подключает к процессору либо основную память 4(1), либо УОД. Б режиме записи информации

0 в УОД процессор 5(1) вьщает в системную магистраль 2(1) записи адрес, операнд и сигналы управления записью которые поступают одновременно на все блоки обмена. При этом по одно5 му и тому же адресу всех блоков обмена будет записана одна и та же информация .

При записи информации в блок обмена (фиг. 2) адрес ячейки и сигна0 лы управления записью поступают по шине 10(1) на адресные входы и выходы управленияj а операнд по числовой шине 11(1) поступает на числовые входы первого независимого канала об5 ращения узла 7(1) памяти. Так как системная магистраль 2(1) записи соединена только с узлами 7(1) памяти всех блоков памяти обмена, то запись информации в УОД могут- производить

0 одновременно все к процессоров систе- МЬ1 в отведенные им узлы памяти. В режиме чтения информации с УОД процессор 5(1) выдает в локальную магистраль 3(1) чтения адрес и сигналы

5 управления чтением, которые поступают на блок 1(1) обмена, считанное слово по этой же магистрали через блок шинных формирователей поступает в процессор 5(1). При чтении ий

31

формации с блока 1(i) обмена m разрядов адреса и сигналы управления чтением (фиг. 2) поступают по 14 на информационные входы коммутатора 8, другие разрядов адре- са поступают на адресные входы коммутатора 8 и мультиплексора 9. В зависимости от кода на шине 15 первые m разрядов адреса и сигналы управления чтением поступают на одну из шин 12, например на шину 12(j). Тогда m первых разрядов адреса и сигналы управления чтением поступают на адресные входы и входы управления второго независимого канала обращения узла 7(j) -памяти.Считанная при этом информация поступает по числовым шинам 13(J) на входы j-ro мультиплексора 9. В соответствии с кодом на шине 15 информация j-ro канала мультиплексора поступает на его выходы и далее по числовой шине 16 поступает в магистраль 3(1), по которой через блок шинных формирователей 6(1) считанная информация поступает в процессор 5(1).

Формула изобретения

Устройство для обмена данными между процессорами, содержащее к блоков обмена, причем входы разрешения чтения, первые- адресные входы и информационные выходы 1-го (1 1,k) блока обмена подключены соответственно к выходам чтения, разрешения чтения.

0

5

77

5 5

0

1274

первым адресным выходам и информационным входам i-ro (,k) процессора, отличающееся тем, что, с целью увеличения быстродействия, каждый блок обмена содержит к узлов памяти, коммутатор и мультиплексор, причем 1 е (1 1,k) входы разрешения записи, 1 е (1 2,k-b1) адресные входы и 1 е (1 1,k) информационные входы 1-го (1 1,k) блока обмена подключены к выходам записи, выходам разрешения записи, вторым адресным выходам и информацион- ным выходам 1-го (1 1,k) процессора, при этом в каждом блоке обмена информационные входы коммутатора образуют входы чтения и разрешения чтения блока обмена, управляющий вход коммутатора соединен с управляющим входом мультиплексора и является первым адресным входом блока обмена, информационный выход мультиплексора является информационным выходом блока обмена, входы записи, разрешения записи, адресные входы и ин- формационные входы 1-го (1 узла памяти образуют 1-й (1 1,k) вход разрешения записи, 1-й (, k + 1) адресный вход и 1-й (1 1,k) информационньш вход блока обмена, при этом 1-я (1 1,k) группа информационных выходов коммутатора соединена с входами разрешения чтения 1- го (1 1,k) узла памяти, информаци- онный выход которого соединен с i-м (1 1,k) информационным входом мультиплексора. 5

iff)

/ n ч

«г

Ю(2

г2Гг} .

74.

J

.

Составитель С.Пестмал Редактор И.Рыбченко Техред. И.Попрвич Корректор А.Ильин

Заказ 6668/43 Тираж 671 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

iff)

гоТгГтП

Л1

г//;

75//)

22f - ;

/g/)

Л7

////у)

7А;

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между процессорами | 1988 |

|

SU1566361A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Устройство для запоминания трассы функционирования многопроцессорных систем | 1990 |

|

SU1737454A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Устройство для сопряжения двух процессоров | 1991 |

|

SU1784983A1 |

| Процессор для мультипроцессорной системы | 1987 |

|

SU1517035A1 |

| Патент США № 4325116, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| СПОСОБ КОРРЕКЦИИ ДИСБИОЗА ВЛАГАЛИЩА ПРИ МЕТАБОЛИЧЕСКОМ СИНДРОМЕ | 2012 |

|

RU2484669C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-15—Публикация

1985-05-22—Подача