Изобретение относится к вычислительной технике и может найти применение в информационно-измерительных системах, в автоматизированных системах для научных исследований и в системах автоконтроля и является усовершенствованием изобретения по авт.св № 450157.

Цель изобретения - повышение пропускной способности системы

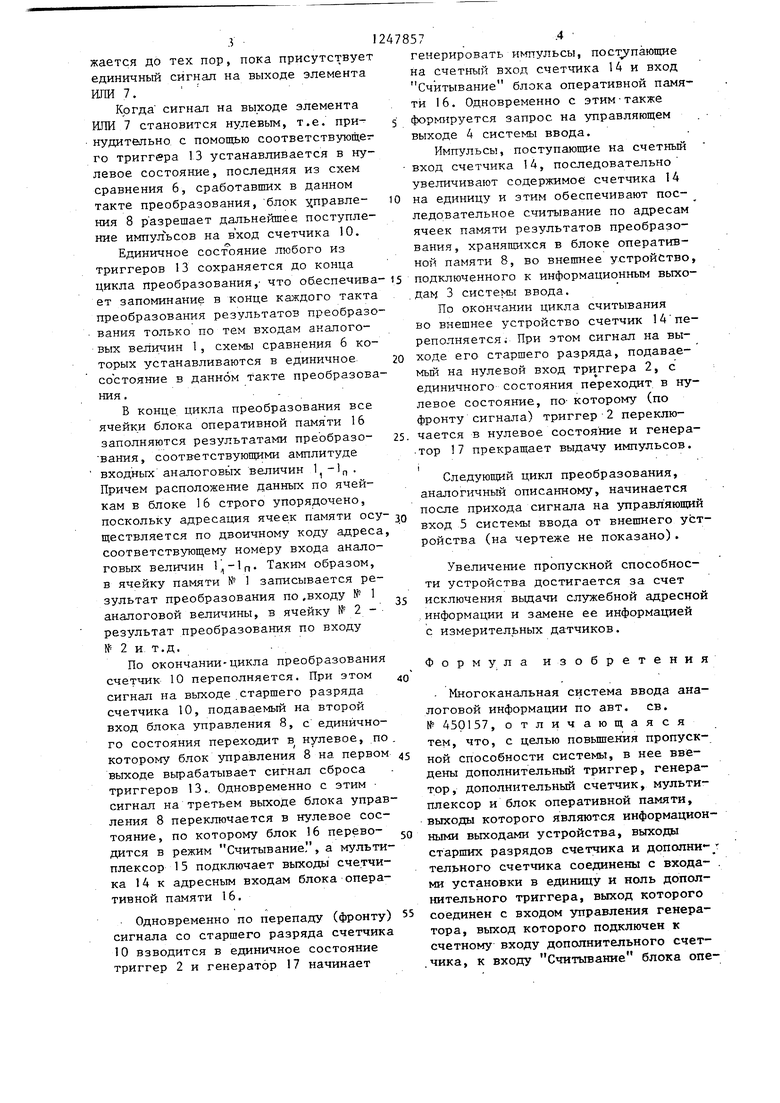

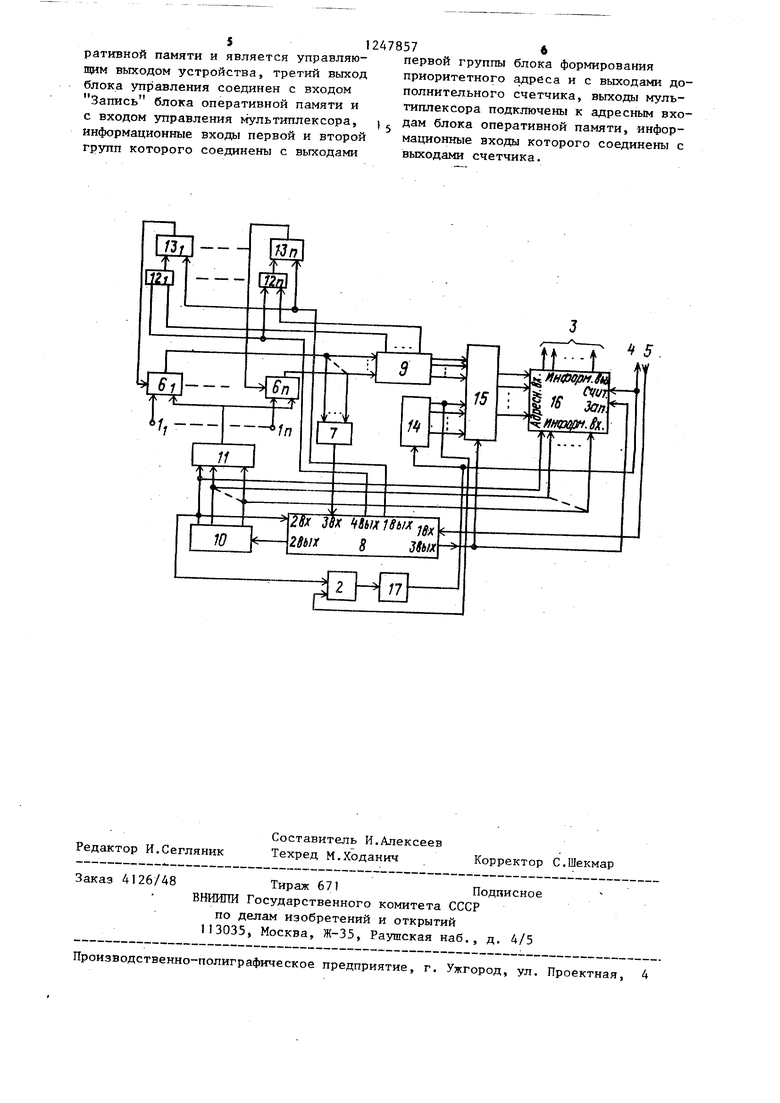

На чер.теже придедена блок-схема многоканальной системы ввода,

Система содержит входы аналоговых величин t -If, , дополнительный триггер 2, информационные выходы 3, управляющий выход 4, управляющий вход 5, схемы сравнения ,,. элемент ИЛИ 7, блок управления 8, блок формирования приоритетного адреса 9, счетчик 10, цифро-аналоговый преобразователь (ЦДЛ) 11, элементы И . и триггеры 1 3 -1 3j, дополнительный счетчик 14, мультиплексор 15, блок оперативной памяти 16, генератор 17.

Многоканальная система ввода работает следующим образом.

Аналоговые сигналы подаются на входы аналоговых величин , На суммирующий вход счетчика 10 блок управления 8 подает последовательность импульсов. Цифро-ана.поговый преобразователь 11 преобразует циф- -ровой код на вьгходе счетчика 10 в аналоговую величину, поступающую на выходы схем сравнения , которые сравнивают эту аналоговую величину с аналоговыми величинами на входах 1 п Если указанные величины на входах некоторой схемы сравнеция, нап ример 6, , совпадают, то на ее выходе устанавливается единичное состояние .

Если хотя бы одна из схем сравнения находится в единичном состоянии, то элемент ИЛИ 7 вырабатьгоа- ет сигнал, поступающий в блок управления 8.

Одновременно с этим блок формирования приоритетного адреса 9, входы которого соединены с выходами схем сравнения ,, формирует на своих выходах позиционный и двоичный коды номера старшей по установленному приоритету схемы сравнения из всех тех, которые находятся в данный момент в единичном состоянии.

С момента появления единичного сигнала на входе элемента ИЛИ 7 блок

управления 8 запрещает выдачу импульсов на вход счетчика 10 и формирует единичный сигнал Запись на третьем выходе. По сигналу Запись

мультиплексор 15 подключает выходы блока формирования приоритетного адреса 9 к адресным входам блока оперативной памяти 16. Одновременно по сигналу Запись, поданного на управляющий вход Запись блока 16, осуществляется запись кода результата преобразования, соответствующего амплитуде аналогового сигнала и поступающего с выходов счетчика 10 на

информационные входы, в ячейку памяти блока 16. Причем адрес ячейки памяти определяет двоичный код адреса, соответствующий номеру входа аналоговой величины, для которого

входная аналоговая величина равна аналоговой величине на выходе цифро- аналогового преобразователя П , сформированный на соответствующих выходах блока формирования приоритетного адреса 9. Ло окончании этой операции блок управления 8 формирует на четвертом выходе сигнал, который поступает на выходы все х элементов И . Вторые входы элементов И соединены индивидуально с выходами, блока формирован ия приоритетного адреса 9, на которых формируется позиционный код адреса входа аналоговых величин, для которого входная аналоговая величина равна аналоговой величине на выходе цифро- аналогового преобразователя 11. Поэтому, при наличии сигнала на каком- либо из этих выходов блока формирования приоритетного адреса, триггер 13 переходит в единичное состояние. В силу того, что сигнал с нулевого выхода каждого из этих триггеров 13 поступает на запрещающей вход соответствующей схемы сравнения 6, она принудительно устанавливается в нулевое состояние и удерживается в нем до окончания &сего цикла преобразования.

Если при этом единичный сигнал, на выходе элемента ИЛИ 7 сохраняется, что указывает на наличие единичного состояния еще одной или нескольких схем сравнения 6, то блок управления

8 вырабатывает очередной сигнал

Запись на третьем выходе и описанный процесс записи информации в блок 6 повторяется. Такой процесс продолжается до тех пор, пока присутствует единичный сигнал на выходе элемента

ти 1.

Когда сигнал на выходе элемента ИЛИ 7 становится нулевым, т.е. при- нудительно с помощью соответствующего триггера 13 устанавливается в нулевое состояние, последняя из схем сравнения 6, сработавших в данном такте преобразования, блок ния 8 р азрешает дальнейшее поступление импул ьсов на вход счетчика 10.

Единичное состояние любого из триггеров 13 сохраняется до конца цикла преобразования,- что об.еспечива ет запоминание в конце каждого такта преобразования результатов преобразования только по тем входам аналоговых величин 1, схемы сравнения 6 которых устанавливаются в единичное состояние в данном такте преобразования ..

В конце цикла преобразования все ячейки блока оперативной памяти 16 заполняются результатами преобразо- вания, соответствующими амплитуде входных аналоговых величин . Причем расположение данных по ячейкам в блоке 16 стр.ого упорядочено, поскольку адресация ячеек памяти осу ществляется по двоичному коду адреса соответствующему номеру входа аналоговых величин г,. Таким образом, в ячейку памяти № 1 записывается результат преобразования по .входу № 1 аналоговой величины, в ячейку № 2 - результат преобразования по входу № 2 и. т.д.

По окончании-цикла преобразования счетчик 10 переполняется. При этом сигнал на выходе старшего разряда счетчика 10, подаваемый на второй вход блока управления 8, с единичного состояния переходит в нулевое, по которому блок управления 8 на первом выходе вырабатывает сигнал сброса триггеров 13.. Одновременно с этим сигнал на третьем выходе блока управления 8 переключается в нулевое состояние, по которому блок 16 перево- дится в режим Считывание,, а мультиплексор 15 подключает выходы счетчика 1 4 к адресным входам блока оперативной памяти 16.

Одновременно по перепаду (фронту) сигнала со старшего разряда счетчика 10 взводится в единичное состояние триггер 2 и генератор 17 начинает

5 Ю

15 20

25. о

Q 5 о

5

5

генерировать иьшульсы, поступающие На счетный вход счетчика 14 и вход Считывание блока оперативной памяти 16. Одновременно с этим-также формируется запрос на управляющем выходе 4 системы ввода.

Импульсы, поступаюшт1е на счетный вход счетчика 14, последовательно увеличивают содержимое счетчика 14 на единицу и этим обеспечивают последовательное считывание по адресам ячеек памяти результатов преобразования , хранящихся в блоке оперативной памяти 8, во внешнее устройство, подключенного к информационным выходам 3 системы ввода.

По окончании цикла считывания во внешнее устройство счетчик 14 переполняется; При этом сигнал на выходе его старшего разряда, подаваемый на нулевой вход три ггера 2, с единичного состояния переходит в нулевое состояние, по- которому (по фронту сигнала) триггер - 2 переключается в нулевое состояние и генера- тор 17 прекращает выдачу импульсов.

i

Следующий цикл преобразования,

аналогичный описанному, начинается после прихода сигнала на управл яющий вход 5 системы ввода от внешнего устройства (на чертеже не показано).

Увеличение пропускной способности устройства достигается за счет исключения вьщачи служебной адресной информации и замене ее информацией с измерительных датчиков.

Формула изобретения

Многоканальная система ввода аналоговой информации по авт. св. № 450157, отличающаяся тем, что, с целью повьшгения пропускной способности системы, в нее введены дополнительный триггер, генератор, дополнительный счетчик, мультиплексор и блок оперативной памяти, выходы которого являются информационными выходами устройства, выходы старших разрядов счетчика и дополни- тельного счетчика соединены с входа- . ми установки в единицу и ноль дополнительного триггера, выход которого соединен с входом управления генератора, выход которого подключен к счетному входу дополнительного счетчика, к входу Считывание блока oneративной памяти и является управляющим выходом устройства, третий выход блока управления соединен с входом Запись блока оперативной памяти и с входом управления мультиплексора, информационные входы первой и второй групп которого соединены с выходами

1247857

первой группы блока формирования приоритетного адреса и с выходами дополнительного счетчика, выходы мультиплексора подключены к адресным входам блока оперативной памяти, информационные входы которого соединены с выходами счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения запаздывающих функций | 1985 |

|

SU1249546A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1984 |

|

SU1238054A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1987 |

|

SU1453397A1 |

| Устройство для ввода аналоговой информации | 1988 |

|

SU1501026A1 |

| Устройство для воспроизведения запаздывающих функций | 1984 |

|

SU1168973A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Устройство для воспроизведения запаздывающих функций | 1985 |

|

SU1285493A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| Формирователь сложной функции | 1982 |

|

SU1107293A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах многопозиционного контроля датчиков. Цель изобретения - повьшение пропускной способности устройства - достигается введением триггера, счетчика, мультиплексора и блока оперативной памяти, которые позволяют расположить р.езуль- таты измерения по порядку нумерации датчиков и дают возможность заменить передачу адресной информации с выхода устройства на информацию с измерительных датчиков. Изобретение - дополнительное к авт.св. № 450157. 1 ил. i

Редактор И.Сегляник

Составитель И.Алексеев Техред М.Ходанич

Заказ 4126/48Тираж 67 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор С.Шекмар

| Многоканальная система ввода аналоговой информации | 1973 |

|

SU450157A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-30—Публикация

1984-07-06—Подача