(Л

gjue.i

3 .150

Изобретение относится к области вычислительной техники и может быть использовано для моделирования схемотехнических решений цифровой РЭЛ, в том- числе микронроцессорной, а также для проектирования заказных и полузаказных БИС, СБИС.

Цель изобретения - раглирение функциональных возможностей устройства за счет возможности моделирования заказных и полузаказных БИС и повьаче- ние достоверности моделирования.

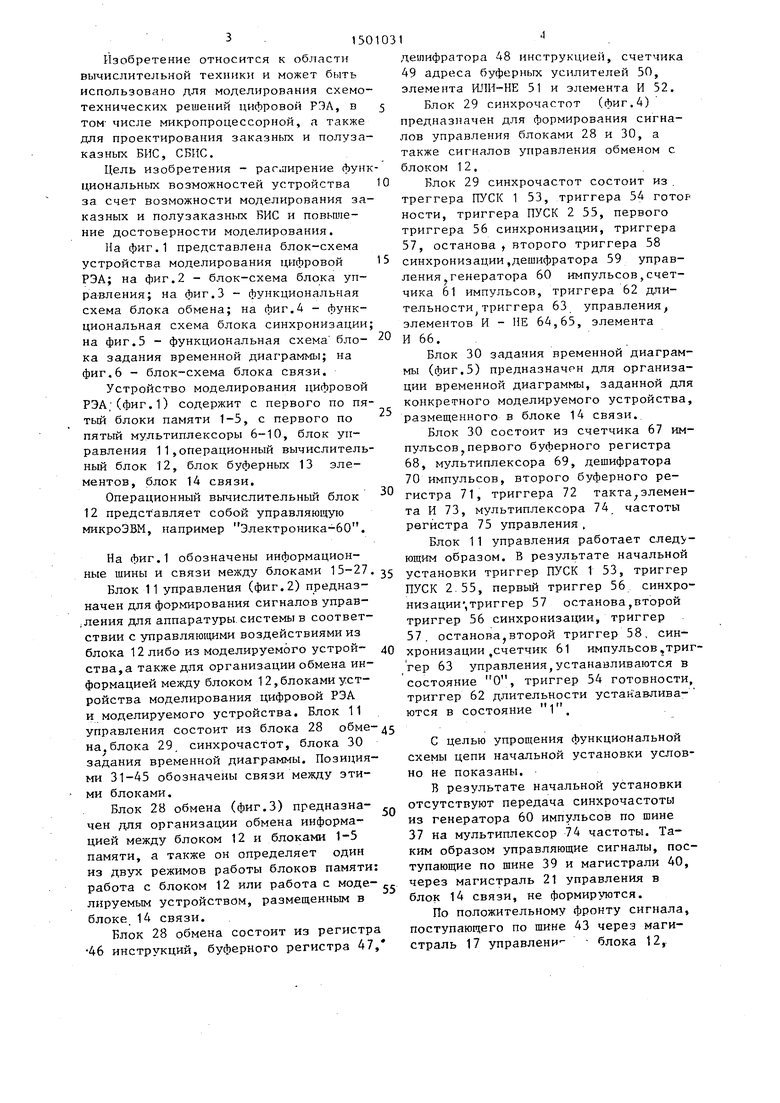

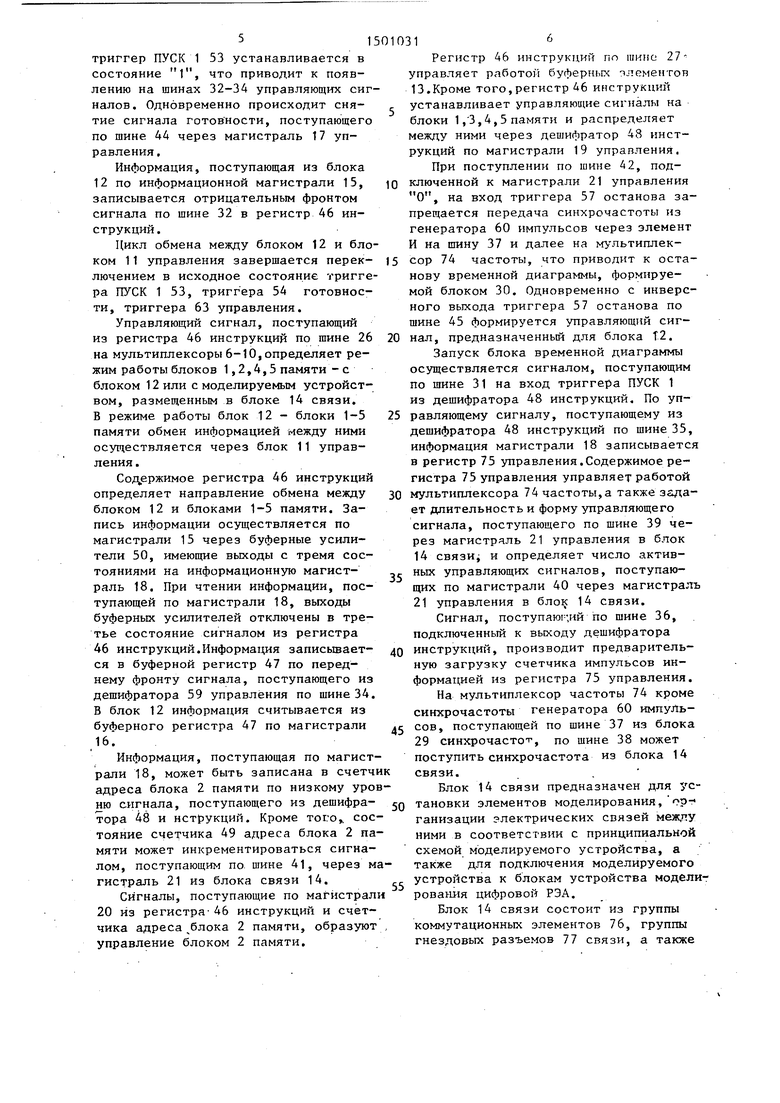

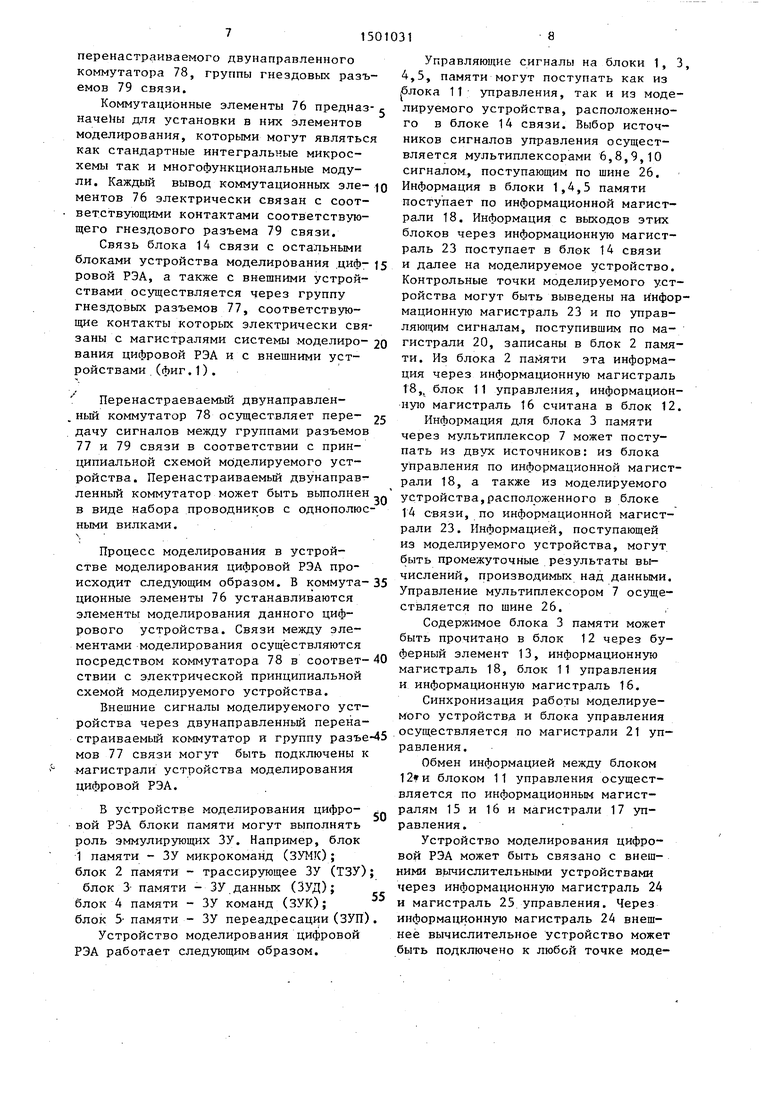

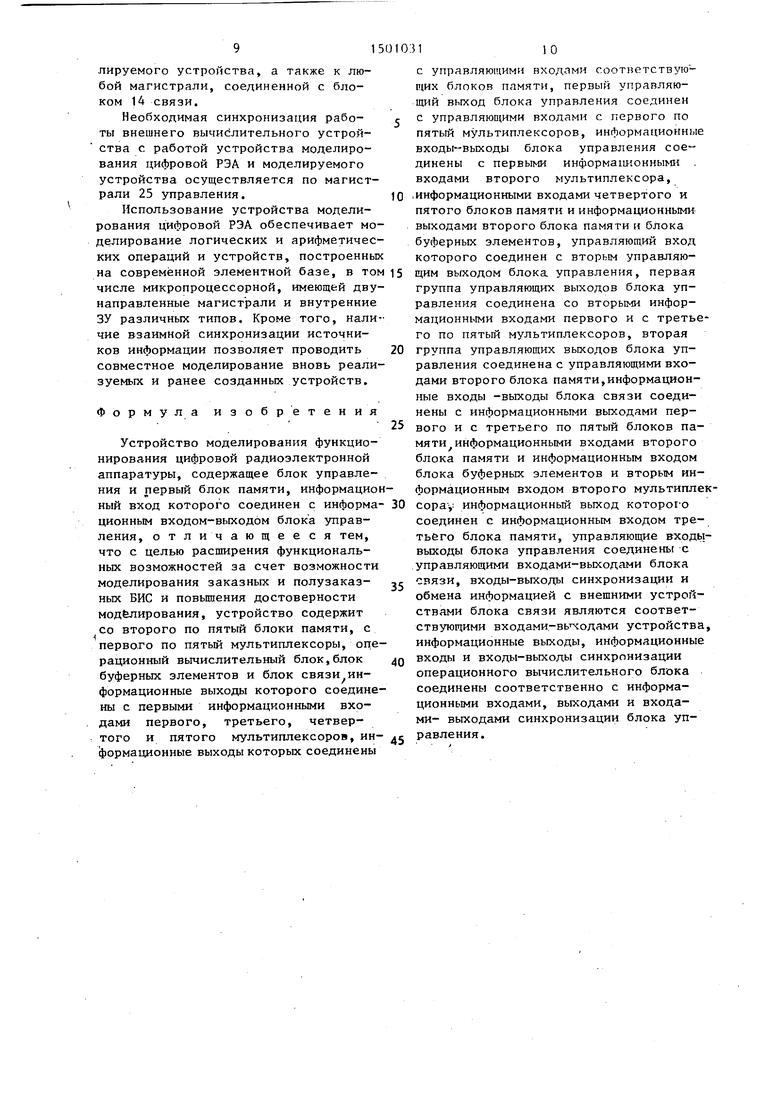

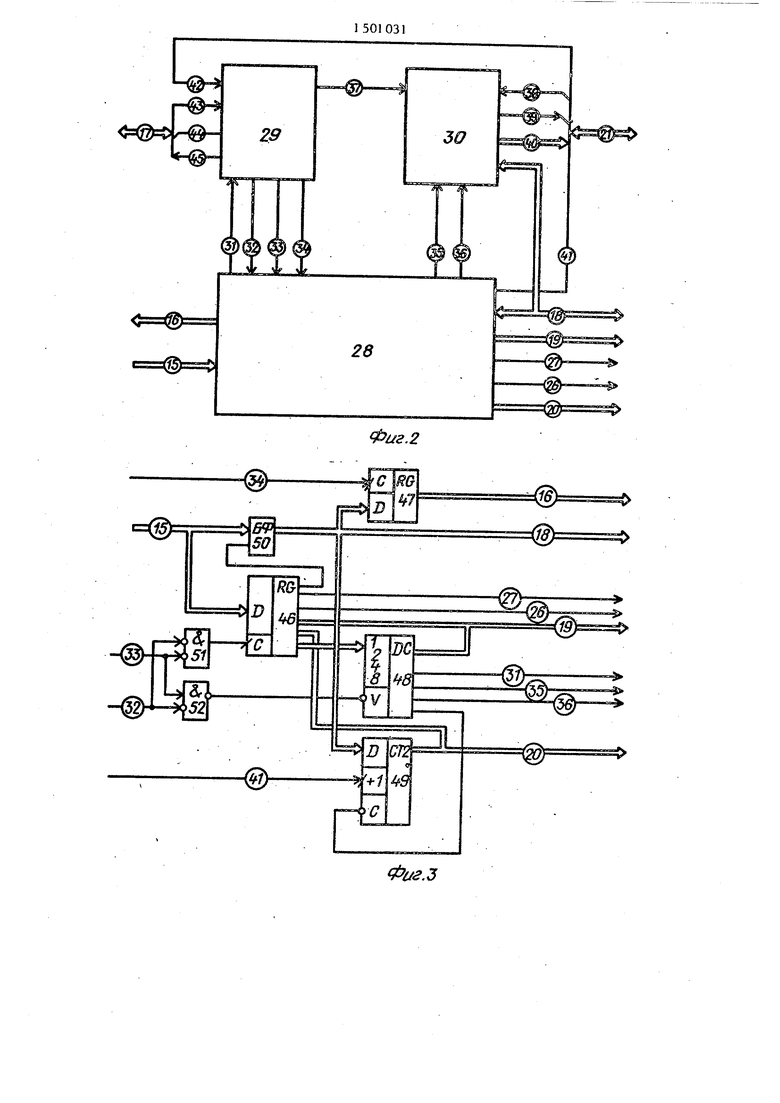

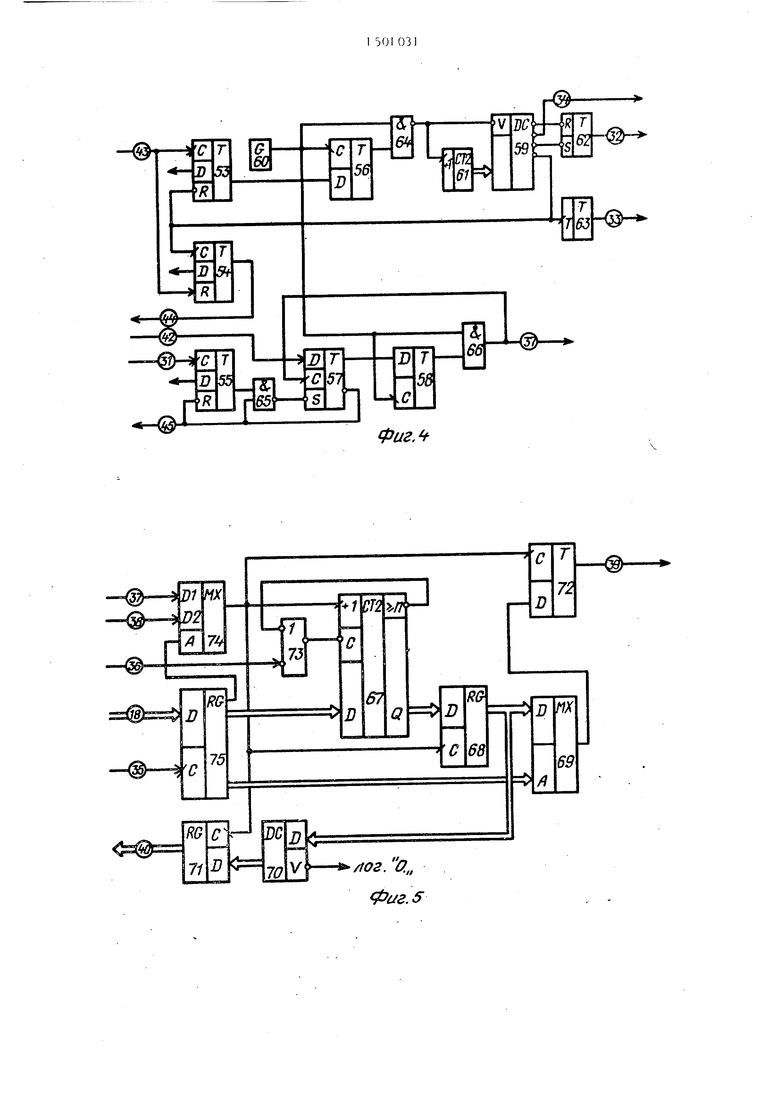

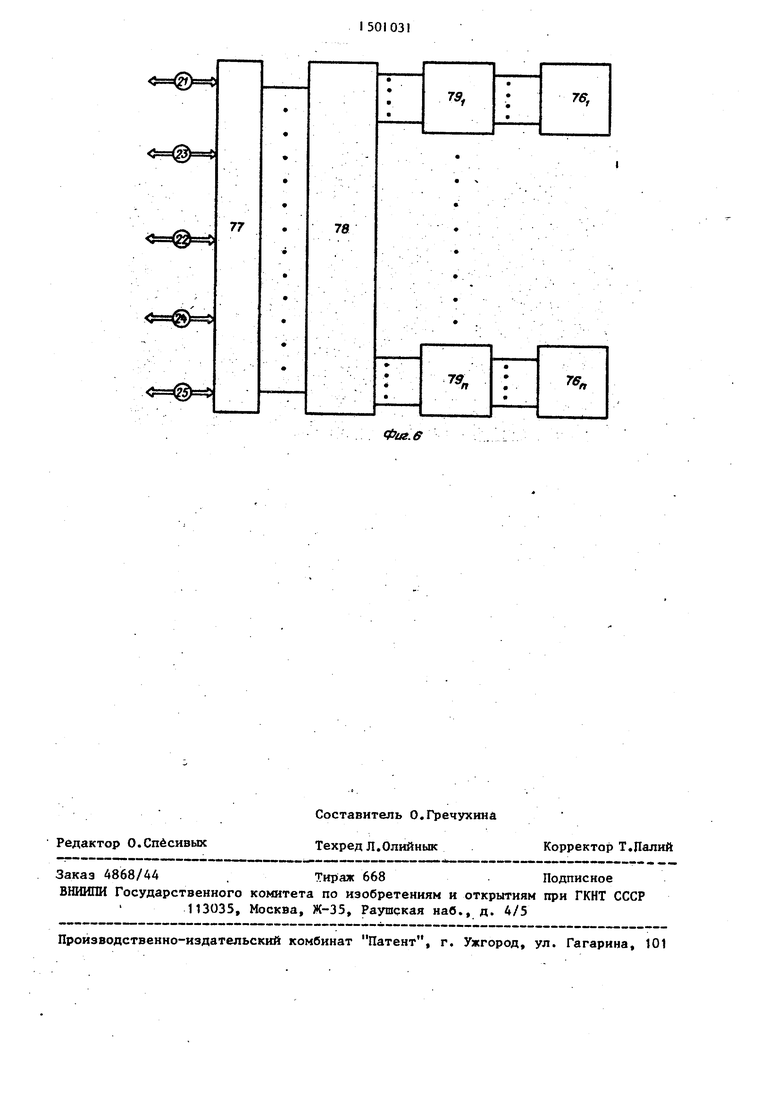

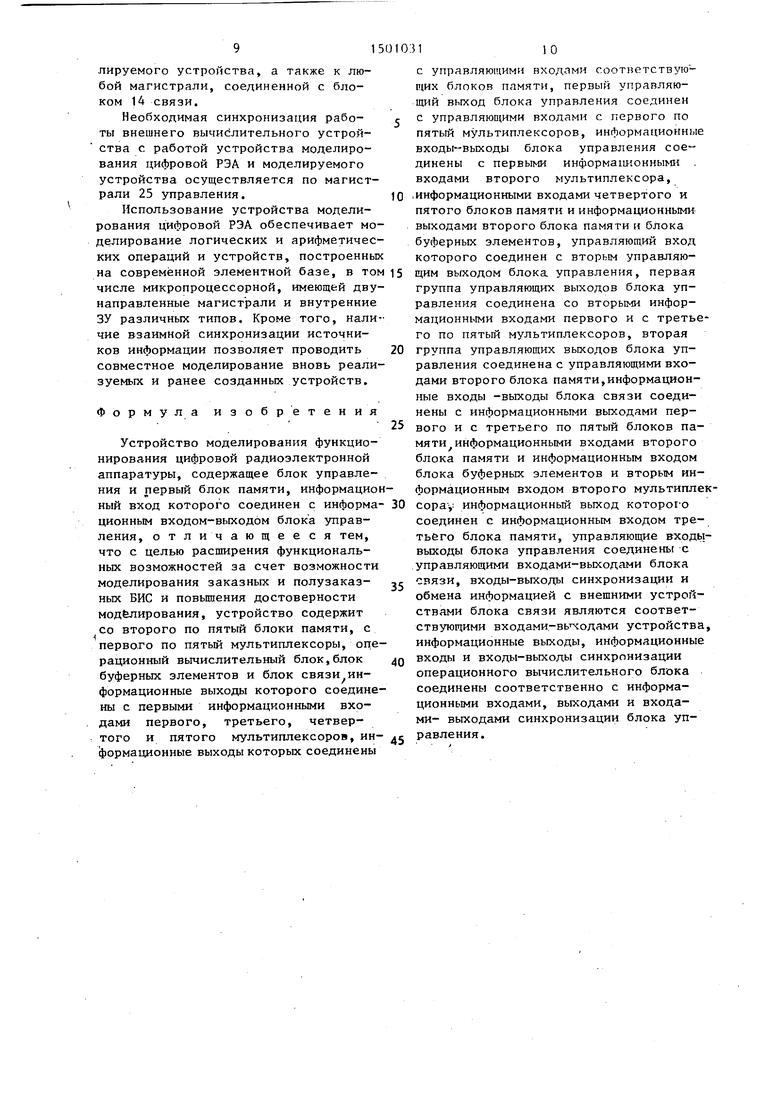

На фиг.1 представлена блок-схема устройства моделирования цифровой РЭА; на фиг.2 - блок-схема блока управления; на фиг.З - функциональная схема блока обмена; на фиг.4 - функциональная схема блока синхронизации; на фиг.З - функциональная схема бло- ка задания временной диаграммы; на фиг.6 - блок-схема блока связи.

Устройство моделирования цифровой РЭА;(фиг.1) содержит с первого по пятый блоки памяти 1-5, с первого по пятый мультиплексоры 6-10, блок управления 11,операционный вычислительный блок 12, блок буферных 13 элементов, блок 14 связи.

Операционный вычислительный блок 12 предст авляет собой управляющую микроэвм, например Электроника-60.

На фиг.1 обозначены информационные шины и связи между блоками 15-27.

Блок 11 управления (фиг.2) предназначен для формирования сигналов управ- ления для аппаратуры, системы в соответствии с управляю1цими воздействиями из блока 12 либо из моделируемого устрой- ства,а также для организации обмена информацией между блоком 12 ,блоками устройства моделирования цифровой РЭА и моделируемого устройства. Блок 11 управления состоит из блока 28 обмена.блока 29, синхрочастот, блока 30 задания временной диаграммы. Позициями 31-45 обозначены связи между этими блоками.

Блок 28 обмена (фиг.З) предназна- чен для организации обмена информацией между блоком 12 и блоками 1-5 памяти, а также он определяет один из двух режимов работы блоков памяти: работа с блоком 12 или работа с моде- лируемым устройством, размещенным в блоке,14 связи.

Блок 28 обмена состоит из регистра 46 инструкций, буферного регистра 47,

1

дешифратора 48 инструкцией, счетчика 49 адреса буферных усилителей 50, элемента Ш1И-НЕ 51 и элемента И 52.

Блок 29 синхрочастот (фиг.4) предназначен для формирования сигналов управления блоками 28 и 30, а также сигналов управления обменом с блоком 12.

Блок 29 синхрочастот состоит из. треггера ПУСК 1 53, триггера 54 ГОТОР ности, триггера ПУСК 2 55, первого триггера 56 синхронизации, триггера 57, останова « второго триггера 58 синхронизации,дешифратора 59 управления генератора 60 импульсов,счетчика 61 импульсов, триггера 62 длительности триггера 63 управления элементов И - НЕ 64,65, элемента И 66.

Блок 30 задания временной диаграммы (фиг.5) предназначен для организации временной диаграммы, заданной для конкретного моделируемого устройства, размещенного в блоке 14 связи.

Блок 30 состоит из счетчика 67 импульсов первого буферного регистра 68, мультиплексора 69, дешифратора 70 импульсов, второго буферного регистра 71, триггера 72 такта элемента И 73, мультиплексора 74 частоты регистра 75 управления .

Блок 11 управления работает следующим образом. В результате начальной установки триггер ПУСК 1 53, триггер ПУСК 2-55, первый триггер 56 синхронизации, триггер 57 останова,второй триггер 56 синхронизации, триггер 57, останова,второй триггер 58, синхронизации ,счетчик 61 импульсов,триггер 63 управления,устанавливаются в состояние О, триггер 54 готовности, триггер 62 длительности устан авливаются в состояние 1.

С целью упрощения функциональной схемы цепи начальной установки условно не показаны.

В результате начальной установки отсутствуют передача синхрочастоты из генератора 60 импульсов по шине 37 на мультиплексор 74 частоты. Таким образом управляющие сигналы, поступающие по щине 39 и магистрали 40, через магистраль 21 управления в блок 14 связи, не формируются.

По положительному фронту сигнала, поступающего по шине 43 через магистраль 17 управление - блока 12,

триггер ПУСК 1 53 устанавливается в состояние 1, что приводит к появлению на шинах 32-34 управляющих сигналов. Одновременно происходит снятие сигнала готов ности, поступающего по шине 44 через магистраль 17 управления.

Информация, поступающая из блока 12 по информационной магистрали 15, записывается отрицательным фронтом сигнала по шине 32 в регистр 46 инструкций.

Цикл обмена между блоком 12 и блоком 11 управления завершается переключением в исходное Состояние триггера ПУСК 1 53, триггера 54 готовности, триггера 63 управления.

Управляющий сигнал, поступающий из регистра 46 инструкций по шине 26 на мультиплексоры 6-10, определяет режим работы блоков 1,2,4,5 памяти - с блоком 12 или с моделируемым устройством, размещенным в блоке 14 связи. В режиме работы блок 12 - блоки 1-5 памяти обмен информацией между ними осуществляется через блок 11 управления .

Содержимое регистра 46 инструкций определяет направление обмена между блоком 12 и блоками 1-5 памяти. Запись информации осуществляется по магистрали 15 через буферные усилители 50, имеющие выходы с тремя состояниями на информационную магистраль 18. При чтении информации, поступающей по магистрали 18, выходы буферных усилителей отключены в третье состояние сигналом из регистра 46 инструкций.Информация записьтает- ся в буферной регистр 47 по переднему фронту сигнала, поступающего из дешифратора 59 управления по шине 34. В блок 12 информация считывается из буферного регистра 47 по магистрали 16.

Информация, поступающая по магистрали 18, может быть записана в счетч адреса блока 2 памяти по низкому уроню сигнала, поступающего из дешифра- тора 48 и нструкций. Кроме того,, состояние счетчика 49 адреса блока 2 памяти может инкрементироваться сигналом, поступающим по шине 41, через м

Блок 14 связи пред тановки элементов мод ганизации электрическ ними в соответствии с схемой моделируемого также для подключени устройства к блокам у

гистрапь 21 из блока связи 14. ,

Сигналы, поступающие по магистрали роващ1я цифровой РЭА. 20 из регистра-46 инструкций и счетчика адреса блока 2 памяти, образуют , управление блоком 2 памяти.

Блок 14 связи сост коммутационных элемен гнездовых разъемов 77

0

5

0

5

Q

0

5

0

5

Регистр 46 инструкций по шипе 27 управляет работой буферных тлементон 13.Кроме того,регистр 46 ир1струкций устанавливает управляющие сигналы на блоки 1 , 3,4,5 памяти и распределяет между ними через дешифратор 48 инструкций по магистрали 19 управления.

При поступлении по шине 42, подключенной к магистрали 21 управления О, на вход триггера 57 останова запрещается передача синхрочастоты из генератора 60 импульсов через элемент И на шину 37 и далее на мультиплексор 74 частоты, что приводит к останову временной диаграммы, формируемой блоком 30. Одновременно с инверсного выхода триггера 57 останова по шине 45 формируется управляющий сигнал, предназначенный для блока Т2.

Запуск блока временной диаграммы осуществляется сигналом, поступающим по шине 31 на вход триггера ПУСК 1 из дешифратора 48 инструкций. По управляющему сигналу, поступающему из дешифратора 48 инструкций по шине 35, информация магистрали 18 записывается в регистр 75 управления.Содержимое регистра 75 управления управляет работой мультиплексора 74 частоты,а также згда- ет длительность и форму управляющего сигнала, поступающего по шине 39 через магистраль 21 управления в блок 14 связку и определяет число активных управляющих сигналов, поступающих по магистрали 40 через магистраль 21 управления в блок 14 связи.

Сигнал, поступаю1-;ий по шине 36, подключенный к вькоду дешифратора инструкций, производит предварительную загрузку счетчика импульсов информацией из регистра 75 управления.

На мультиплексор частоты 74 кроме синхрочастоты генератора 60 импуЛь- сов, поступающей по шине 37 из блока 29 синхрочастот, по шине 38 может поступить синхрочастота из блока 14 связи.

Блок 14 связи предназначен для установки элементов моделирования, орт ганизации электрических связей меж,1ту ними в соответствии с принципиальной схемой моделируемого устройства, а также для подключения моделируемого устройства к блокам устройства модели,

роващ1я цифровой РЭА.

Блок 14 связи состоит из группы коммутационных элементов 76, группы гнездовых разъемов 77 связи, а также

перенастраиваемого двунаправленного коммутатора 78, группы гнездовых разъемов 79 связи.

Коммутационные элементы 76 предназ- с начеты для установки в них элементов моделирования, которыми могут являться как стандартные интегральные микросхемы так и многофункциональные модули. Каждый вывод коммутационных эле- ю ментов 76 электрически связан с соот- ветствующими контактами соответствующего гнездового разъема 79 связи.

Связь блока 14 связи с остальными блоками устройства моделирования диф- 15 РОБОЙ РЭА, а также с внешними устройствами осуществляется через группу гнездовых разъемов 77, соответствующие контакты которых электрически связаны с магистралями системы моделиро-20 вания цифровой РЭА и с внешними устройствами . (фиг . 1 ).

Перенастраеваемый двунаправлен- ный коммутатор 78 осзтцествляет пере- 25 дачу сигналов между группами разъемов 77 и 79 связи в соответствии с принципиальной схемой моделируемого устройства. Перенастраиваемый двунаправленный коммутатор может быть выполнен в виде набора проводников с однополюсными вилками. .

30

Процесс моделирования в устройстве моделирования цифровой РЭА происходит следующим образом. В коммута- ционные элементы 76 устанавливаются элементы моделирования данного цифрового устройства. Связи между элементами моделирования осуществляются посредством коммутатора 78 в соответ- ствии с электрической принципиальной схемой моделируемого устройства.

Внешние сигналы моделируемого устройства через двунаправленньй перенастраиваемый коммутатор я группу разъе мов 77 связи могут быть подключены к магистрали устройства моделирования цифровой РЭА.

В устройстве моделирования цифро- вой РЭА блоки памяти могут выполнять роль эммулирующих ЗУ. Например, блок 1 памяти - ЗУ микрокоманд (ЗУМК); блок 2 памяти - трассирующее ЗУ (ТЗУ)

блок 3- памяти - ЗУ данных (ЗУД); блок 4 памяти - ЗУ команд (ЗУК); блок 5- памяти - ЗУ переадресации (ЗУП

Устройство моделирования цифровой РЭА работает следующим образом.

5 0

5

0

5 0

5

д

Управляющие сигналы на блоки 1, 3, 4,5, памяти могут поступать как из рлока 11 управления, так и из моделируемого устройства, расположенного в блоке 14 связи. Выбор источников сигналов управления осуществляется мультиплексорами 6,8,9,10 сигналом., поступающим по шине 26. Информация в блоки 1,4,5 памяти поступает по информационной магистрали 18. Информация с выходов этих блоков через информационную магистраль 23 поступает в блок 14 связи и далее на моделируемое устройство. Контрольные точки моделируемого устройства могут быть выведены на информационную магистраль 23 и по управляющим сигналам, поступившим по магистрали 20, записаны в блок 2 памяти. Из блока 2 памяти эта информация через информационную магистраль 18,, блок 11 управления, информационную магистраль 16 считана в блок 12.

Информация для блока 3 памяти через мультиплексор 7 может поступать из двух источников: из блока управления по информационной магистрали 18, а также из моделируемого устройства,расположенного в блоке 14 связи, по информационной магистрали 23. Информацией, поступающей из моделируемого устройства, могут быть промежуточные результаты вычислений, производимых над данными. Управление мультиплексором 7 осуществляется по шине 26.

Содержимое блока 3 памяти может быть прочитано в блок 12 через буферный элемент 13, информационную магистраль 18, блок 11 управления и информационную магистраль 16.

Синхронизация работы моделируемого устройства и блока управления осуществляется по магистрали 21 управления.

Обмен информацией между блоком блоком 11 управления осуществляется по информационным магистралям 15 и 16 и магистрали 17 управления .

Устройство моделирования цифровой РЭА может быть связано с внешними в.ычислительными устройствами через информационную магистраль 24 и магистраль 25 управления. Через информационную магистраль 24 внешнее вычислительное устройство может быть подключено к любой точке моделируемого устройства, а также к любой магистрали, соединенной с блоком 14 связи.

Необходимая синхронизация рабо- ты внешнего вычислительного устройства с работой устройства моделирования цифровой РЭА и моделируемого устройства осуществляется по магистрали 25 управления.

Использование устройства моделирования цифровой РЭА обеспечивает моделирование логических и арифметических операций и устройств, построенных на современной элементной базе, в том числе микропроцессорной, имеющей двунаправленные магистрали и внутренние ЗУ различных типов. Кроме того, наличие взаимной синхронизации источников информации позволяет проводить совместное моделирование вновь реализуемых и ранее созданных устройств.

Формула изобретения

Устройство моделирования функционирования цифровой радиозлектронной аппаратуры, содержащее блок управления и первый блок памяти, информационный вход которого соединен с информа- 30 ционным входом-выходом блока управления, отличающееся тем, что с целью расширения функциональных возможностей за счет возможности моделирования заказных и полузаказ- ,с ных БИС и повьшения достоверности моделирования, устройство содержит со второго по пятый блоки памяти, с первого по пятый мультиплексоры, оце- рационный вычислительный блок,блок 0 буферных элементов и блок связи информационные выходы которого соединены с первыми информационными вхо- дами первого, третьего, четвертого и пятого мультиплексоров, ин- д ормационные выходы которых соединены

с Q

5 0

5

0 с 0

с управляющими входами соотнетствую - щих блоков памяти, первый управляющий выход блока управления соединен с управляюп(ими входами с первого по пятьй мультиплексоров, информационные входы-выходы блока управления соединены с первыми информационными входами второго мультиплексора, .информационными входами четвертого и пятого блоков памяти и информационными выходами второго блока памяти и бЛока буферных элементов, управляющий вход которого соединен с вторым управляющим выходом блока управления, первая группа управляющих выходов блока управления соединена со вторыми информационными входами первого и с третьего по пятый мультиплексоров, вторая группа управляющих выходов блока управления соединена с управляющими входами второго блока памяти,информационные входы -выходы блока связи соединены с информационными выходами первого и с третьего по пятый блоков памяти информационными входами второго блока памяти и информационным входом блока буферных элементов и вторым информационным входом второго мультиплек- сорау информационный вькод которог о соединен с информационным входом третьего блока памяти, управляющие входы- выходы блока управления соединень с управляющими входами-выходами блока связи, входы-выходы синхронизации и обмена информацией с внешними устройствами блока связи являются соответствующими входами-вь одами устройства, информационные выходы, информационные входы и входы-выходы синхронизации операционного вычислительного блока соединены соответственно с информационными входами, выходами и входами- выходами синхронизации блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления подключением к магистрали | 1985 |

|

SU1304024A1 |

| Контроллер станции локальной сети | 1988 |

|

SU1647590A1 |

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для моделирования конечных автоматов | 1988 |

|

SU1520534A1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА | 2002 |

|

RU2221267C1 |

| Устройство для проверки функциональных блоков | 1980 |

|

SU1008745A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

Изобретение относится к вычислительной технике и может быть использовано для моделирования схемотехнических решений цифровой РЭА, в том числе микропроцессорной, а также для проектирования заказных и полузаказных БИС и СБИС. Цель изобретения расширение функциональных возможностей устройства - достигается тем, что в устройство, содержащее блок памяти 1 и блок управления 11, дополнительно введены блоки памяти 2-5, пять мультиплексоров 6-10, операционный вычислительный блок 12, блок буферных элементов 13 и блок связи 14. 6 ил.

ф

2ff

за

Фиг.2

.З

-

€

; J)

MX

74

t

7J

RG

75

RG 71

С

DC

70

-@b

CT2

I

27

55

т

69

/f03. a,,

Фиг. S

77

18

n

Гб

| Устройство для контроля момента при ударной затяжке резьбовых соединений | 1985 |

|

SU1306702A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Авторское свидетельство СССР Р | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1987-07-24—Подача