IS IS .20

70 2

(Л

сг

:д

П

со

..Jb.

3 1501073

Изобретение относится к вычислиельной технике, в частности к устойствам управления вычислительным омплексом.

Цель изобретения - сокращение апаратурных затрат.

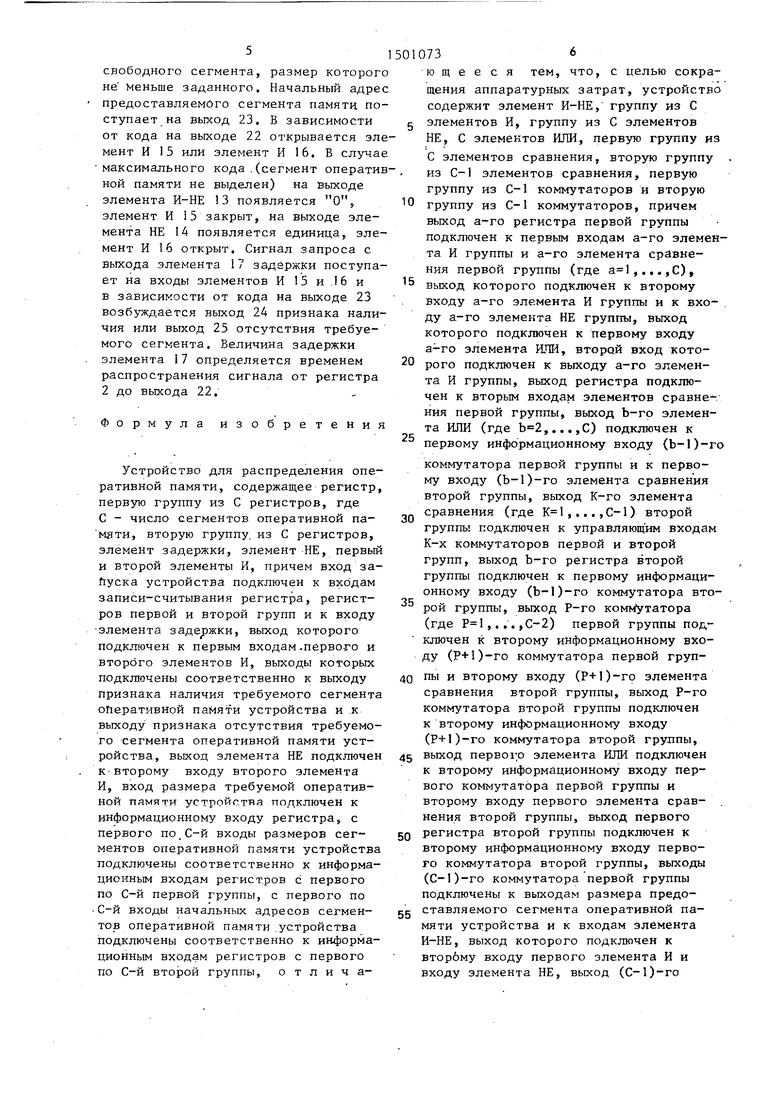

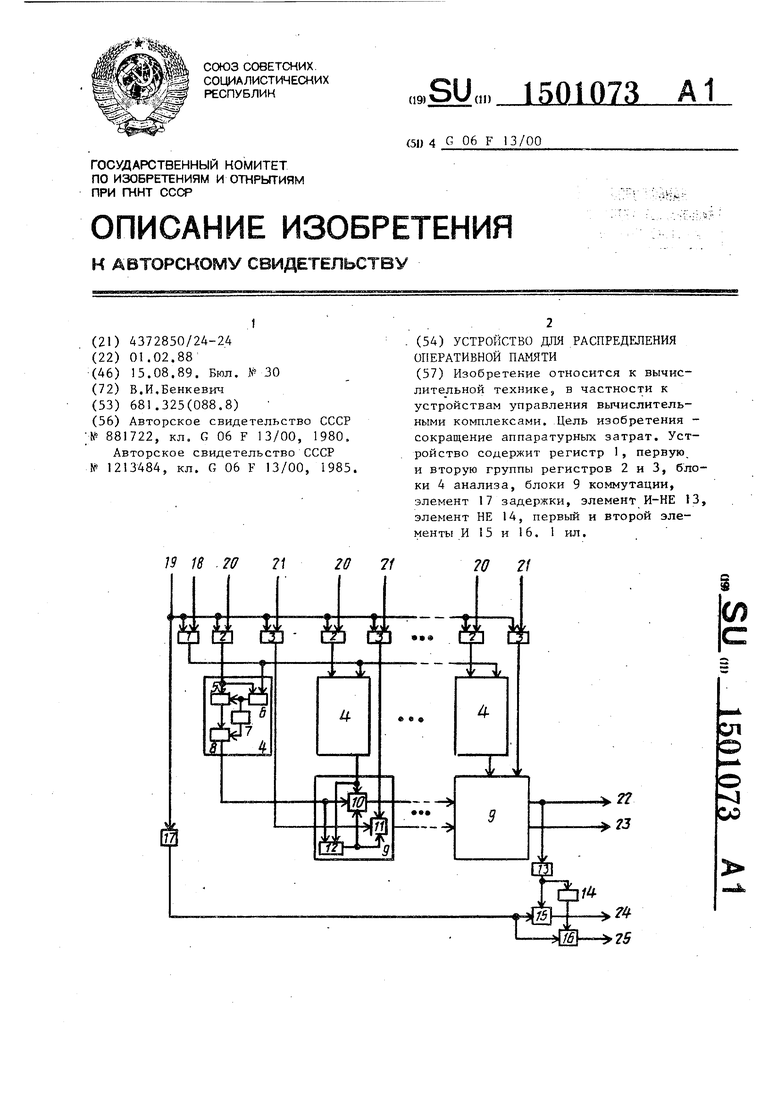

На чертеже представлена схема стройства.

Устройство содержит регистр 1, пер-Ю ую 2 и вторую 3 группы из С регистров соответственно 2 и 3, где С - исло сегментов оперативной памяти, С блоков А анализа, каждый из кото- рых содержит элемент И 5, элемент 6 15

сравнения, элемент НЕ 7. и элемент ШШ 8, () блоков 9 коммутации, каждый из которых содерл ит первый 10 и второй 11 коммутаторы и элемент 12 сравнения, элемент И-НЕ 13, эле- 20 мент НЕ 14, первый 15 и второй 16 элементы. И, элемент 17 задержки, вход 18 размера требуемой оперативной памяти устройства, вход 19- запуска устройства, входы 20 размеров сег- ментов оперативной памяти устройства, входы 21 начальных адресов сегментов оперативной памяти Устройства, выходы 22 .размера представляемого сегмента оперативной памяти устройства, 30 вькод 23 начального адреса предоставляемого сегмента оперативной памяти устройства, выход 24 признака наличия требуемого сегмента, оперативной памяти устройства и выход 25 призна- 35 ка отсутствия требуемого сегмента оперативной памяти устройства.

Устройство работает следующие об- ; разом.

По сигналу запроса с входа .19 в 4t регистр 1 заносится код размера требуемой оперативной памяти, -в регистры ,. 2 через входы 20 - коды размеров сегментов памяти, в регистры 3 через -входы 21 - начальные адреса сег- 45 ментов памяти( причем, ес.пи некоторый сегмент занят., в соответствующие регистры 2 и 3 заносится нулевой код (нули во все разряды регистра),

В каждом блоке анализа на элементе 6 сравнения происходит сравнение кода размера сегмента с требуемым. Если размер i.-ro сегмента больше и равен требуемому, то на выходе эле- ,. мента сравнения 6 появляется 1, которая открырает элементы И 5, и код размера сегькч та гичмят и через элементы И 5 и 3. Tt:MeHTW И.ПИ 8 поступает на

вход блока коммутации. Если размер .сегмента памяти меньше требуемого, то на выходе элемента сравнения 6 появляется О, элементы И 5 закрыты, на выходе элемента НЕ 7 появляется уровень 1, а на выходе элементов ИЛИ 8 - максимальньй код (все единицы) ,

Таким образом, блоки 4 анализа выделяют только те сегменты, размеры которых не меньше заданного. Непригодность некоторого сегмента памяти для дальнейшего использования указывает максимальный код на выходе соответствующего блока анализа.

Каждый блок 9 коммутации предназначен для выделения минимального из двух чисел, а последовательность из (С-I ) блоков коммутации представляет собой схему для выделения минимального из С чисел.

На элемент 12 сравнения каждого блока 9 коммутации поступают коды размеров сегментов памяти. Если код на первом входе элемента 12 больше и равен коду размера сегмента на втором входе, то на выходе элемента 12 сравнения появляется единичный потенциал и коммутаторы 10 и 11 открываются по второму входу . В противном случае (число на первом входе меньше числа на втором входе) на выходе элемента -12 сравнения появляется О и коммутаторы 10 и П открываются по первому входу. Таким образом, при поступлении на входы блока коммутации кодов размеров сегментов памяти и соответствующих им . адресов на выходе коммутатора 10 .появляется код размера меньшего из сегментов, а на выходе коммутатора 1i - соответствующий ему начальный адрес. При последовательном соеди- нении(С-) блоков коммутации на вы ходе последнего выделяется код йаи- меньшего из С рассмэтривае й1х.

Таким образом, блоки анализа обеспечивают выделение -только тех сег- ментов, размеры которых не меньше заданного, а блоки коммутации из выделенных выбирают сегмент минимального размера и соответствующий ему начадьньгй адрес.

Код .размера предоставляемого сегмента поступает на выход 22 устрой- c-TBaj причем максимальный код (все ,единицы) обозначает cиfyaцию, когда сегменты памяти заняты или нет

свободного сегмента, размер которого не меньше заданного. Начальный адрес предоставляемого сегмента памяти поступает на выход 23. В зависимости от кода на выходе 22 открывается элемент И 15 или элемент И 16. В случае максимального кода .(сегмент оперативной памяти не выделен) на Выходе элемента И-НЕ 3 появляется О, элемент И 15 закрыт, на выходе элемента НЕ 14 появляется единица, элемент И 16 открыт. Сигнал запроса с выхода элемента 17 задержки поступает на входы элементов И 15 и .16 и в зависимости от кода на выходе 23 возбуждается выход 24 признака наличия или выход 25 отсутствия требуемого сегмента. Величина задержки элемента i 7 определяется временем распространения сигнала от регистра 2 до выхода 22.

Формула изобретения

Устройство для распределения оперативной памяти, содержащее регистр первую группу из С регистров, где С - число сегментов оперативной па млти, вторую группу, из С регистров, элемент задержки, элемент НЕ, первый и второй элементы И, причем вход за- йуска устройства подключен к входам записи-считывания регистра, регистров первой и второй групп и к входу

элемента задержки, выход которого подключен к первым входам.первого и второго элементов И, выходы которых подключены соответственно к выходу признака наличия требуемого сегмента оперативной памяти устройства и к выходу признака отсутствия требуемого сегмента оперативной памяти устройства, выход элемента НЕ подключен к-второму входу второго элемента И, вход размера требуемой оперативной памяти устройства подключен к информационному входу регистра, с первого входы размеров сегментов оперативной памяти устройства подключены соответственно к информационным входам регистров с первого по С-й первой группы, с первого по

С-й входы начальных адресов сегментов оперативной памяти .устройства подключены соответственно к информационным входам регистров с первого по второй группы, о т л и ч а010736

ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, устройство содержит элемент И-НЕ, группу из С g элементов И, группу из С элементов НЕ, С элементов ИЛИ, первую группу из С элементов сравнения, вторую группу из С-1 элементов сравнения, первую группу из С-1 коммутаторов и вторую О группу из С-1 коммутаторов, причем выход а-го регистра первой группы подключен к первым входам а-го элемента И группы и а-го элемента сравнения первой группы (где ,.,.,С),

15

20

30

выход которого подключен к второму входу а-го элемента И группы и к входу а-го элемента НЕ группы, выход которого подключен к первому входу а-го элемента ИЛИ, второй вход которого подключен к выходу а-го элемента И группы, выход регистра подключен к вторым входам элементов сравне. НИН первой группы, выход Ь-го элемента ИЛИ (где ,...,С) подключен к первому информационному входу (b-l)-ro

коммутатора первой группы и к первому входу (b-l)-ro элемента сравнения второй группы, выход К-го элемента сравнения (где ,...,С-1) второй группы подключен к управляющ им входам К-к коммутаторов первой и второй групп, выход Ь-го регистра второй группы подключен к первому информационному входу (b-l)-ro коммутатора вто- рой группы, выход Р-го ком1.татора (где ,...,С-2) первой группы под- ключей к второму информационному входу (Р+1)-го коммутатора первой груп40 пы и второму входу (Р+1)-го элемента сравнения второй группы, выход Р-го коммутатора второй группы подключен к второму информационному входу (Р+1)-го коммутатора второй группы,

5 выход первого элемента ИЛИ подключен к второму информационному входу первого коммутатора первой группы и второму входу первого элемента срав- . нения второй группы, выход первого

Q регистра второй группы подключен к второму информационному входу первого коммутатора второй группы, выходы (С-1)-го коммутатора первой группы подключены к выходам размера предоg ставляемого сегмента оперативной памяти устройства и к входам элемента И-НЕ, выход которого подключен к вторбму входу первого элемента И и входу элемента НЕ, выход (C-l)-ro

71501073 8

коммутатора второй группы подключен ляемого сегмента оперативной памяти к выходу начального адреса предостав- устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения ресурсов оперативной памяти | 1985 |

|

SU1290335A1 |

| Устройство для адресации памяти | 1986 |

|

SU1328820A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1275442A1 |

| Устройство для обмена информацией | 1980 |

|

SU955014A1 |

| Устройство распределения оперативной памяти | 1988 |

|

SU1509909A1 |

| Система коммутации | 1986 |

|

SU1359783A1 |

| Система коммутации | 1985 |

|

SU1317447A1 |

| Резервированная вычислительная система | 1990 |

|

SU1755400A1 |

| Устройство приема цифровых факсимильных сигналов с коррекцией искажений изображения | 1985 |

|

SU1319313A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

Изобретение относится к вычислительной технике , в частности, к устройствам управления вычислительными комплексами. Цель изобретения - сокращение аппаратурных затрат. Устройство содержит регистр 1, первую и вторую группы регистров 2 и 3, блоки 4 анализа, блоки 9 коммутации, элемент 17 задержки, элемент И-НЕ 13, элемент НЕ 14, первый и второй элементы И 15 и 16. 1 ил.

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство распределения оперативной памяти | 1984 |

|

SU1213484A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-08-15—Публикация

1988-02-01—Подача