сд

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1975 |

|

SU733025A1 |

| Тренажер оператора радиоэлектронной аппаратуры | 1989 |

|

SU1658193A1 |

| Запоминающее устройство | 1984 |

|

SU1241291A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Запоминающее устройство | 1982 |

|

SU1043741A1 |

| Запоминающее устройство | 1983 |

|

SU1203596A1 |

| Запоминающее устройство с коррекцией информации | 1981 |

|

SU957273A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| Тренажер оператора радиоэлектронной аппаратуры | 1988 |

|

SU1524084A1 |

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

Изобретение относится к вычислительной технике и может быть использовано при изготовлении сверхбольших интегральных схем памяти с матричной организацией, имеющих большую площадь кристалла, где требуется высокая емкость памяти. Целью изобретения является повышение эффективности емкости устройства и уменьшение потребляемой мощности. Блок памяти содержит узел памяти 1, узел сравнения 9, программируемые первый 10 и второй 11 регистры, первый элемент ИЛИ 12. Введение в блок памяти второго элемента ИЛИ 13, элемента И 17, сумматора 16 по модулю два, дешифратора 14 позволило осуществить специальным подбором пар дефектных блоков с годными половинами достаточно высокую эффективность использования запоминающих устройств. 3 ил.

Фе/г/

Изобретение относится к вычисли- , тельной технике и может быть использовано при изготовлении запоминающих устройств с матричной организацией на одном кристалле..

Изобретение целесообразно использовать при производстве сверхбольших интегральных схем памяти с матричной организацией, имеющей большую площадь кристалла, где требуется высокая емкость памяти.

Цель изобретения - повышение эффективности емкости устройства и уменьшение потребляемой мощности.

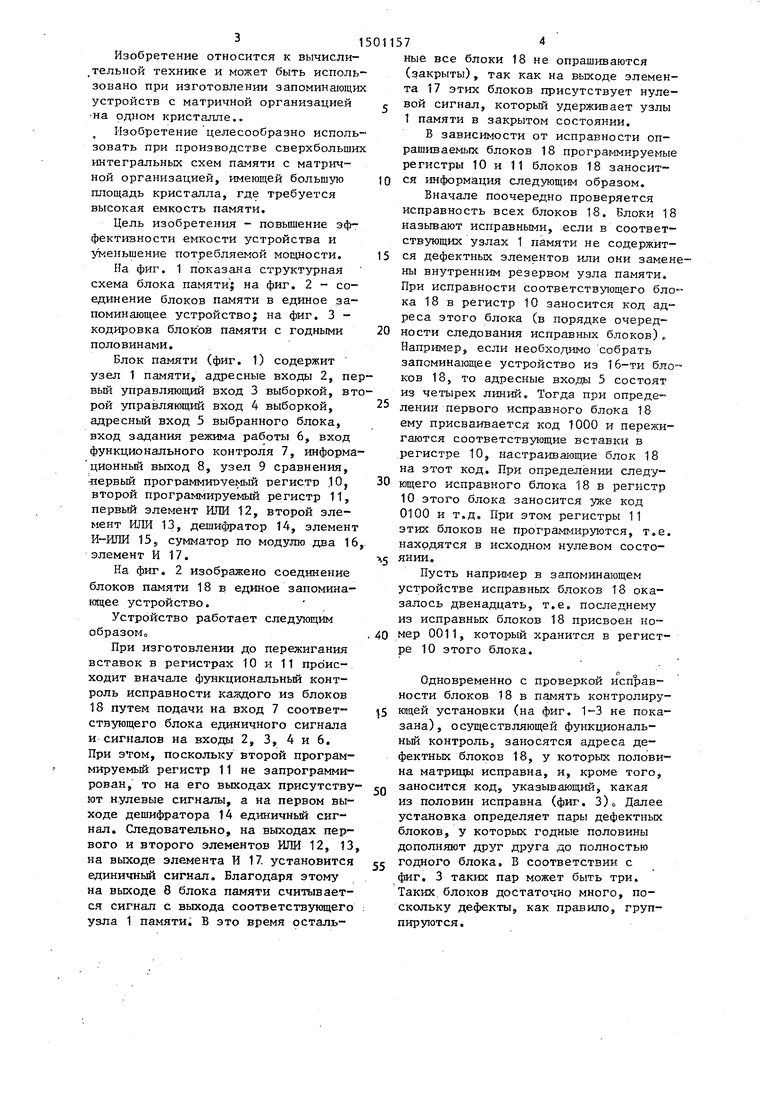

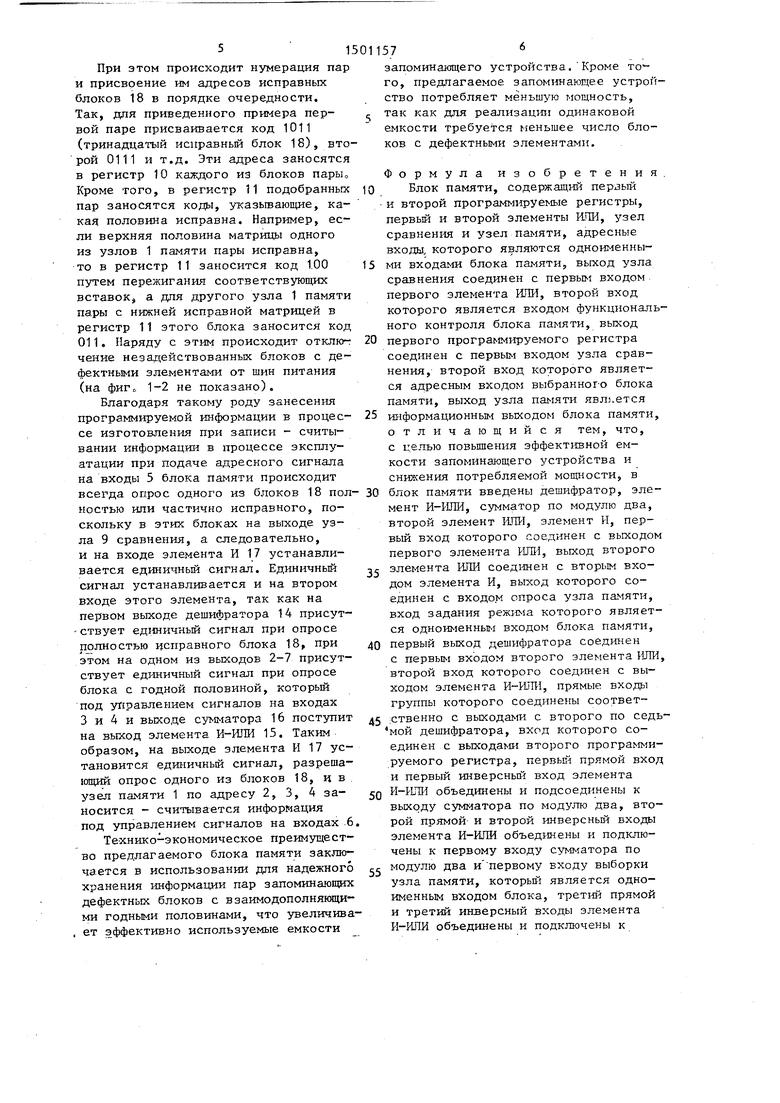

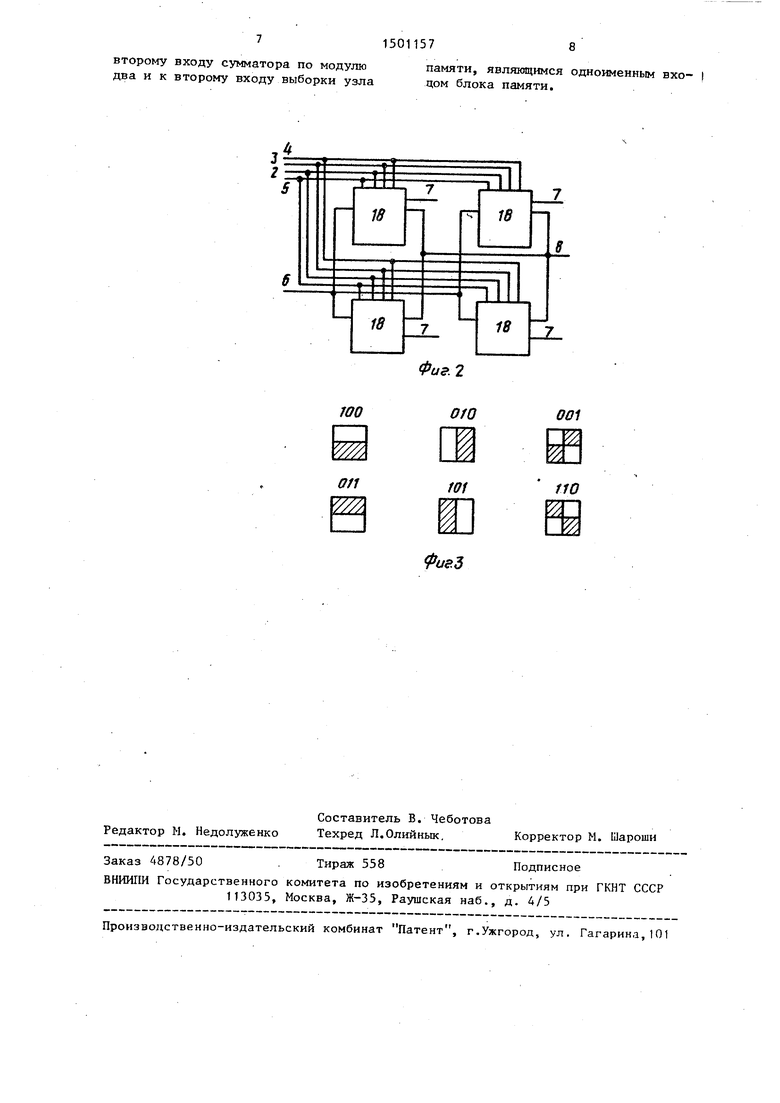

На фиг. 1 показана структурная схема блока памяти; на фиг, 2 - соединение блоков памяти в единое запоминающее устройство на фиг, 3 - кодировка блоков памяти с годными половинами.

Блок памяти (фиг, 1) содержит узел 1 памяти, адресные входы 2, первый управляющий вход 3 выборкой, второй управляющий вход 4 выборкой, адресньм вход 5 выбранного блока, вход задания режима работы 6, вход функционального контроля 7, информа- ционньй выход 8, узел 9 сравнения, лервый программирует регистр JO, второй программируемый регистр 11, первый элемент ИЛИ 12, второй элемент ИЛИ 13, дешифратор 14, элемент И-ИЛИ 13, сумматор по модулю два 16 элемент И 17,

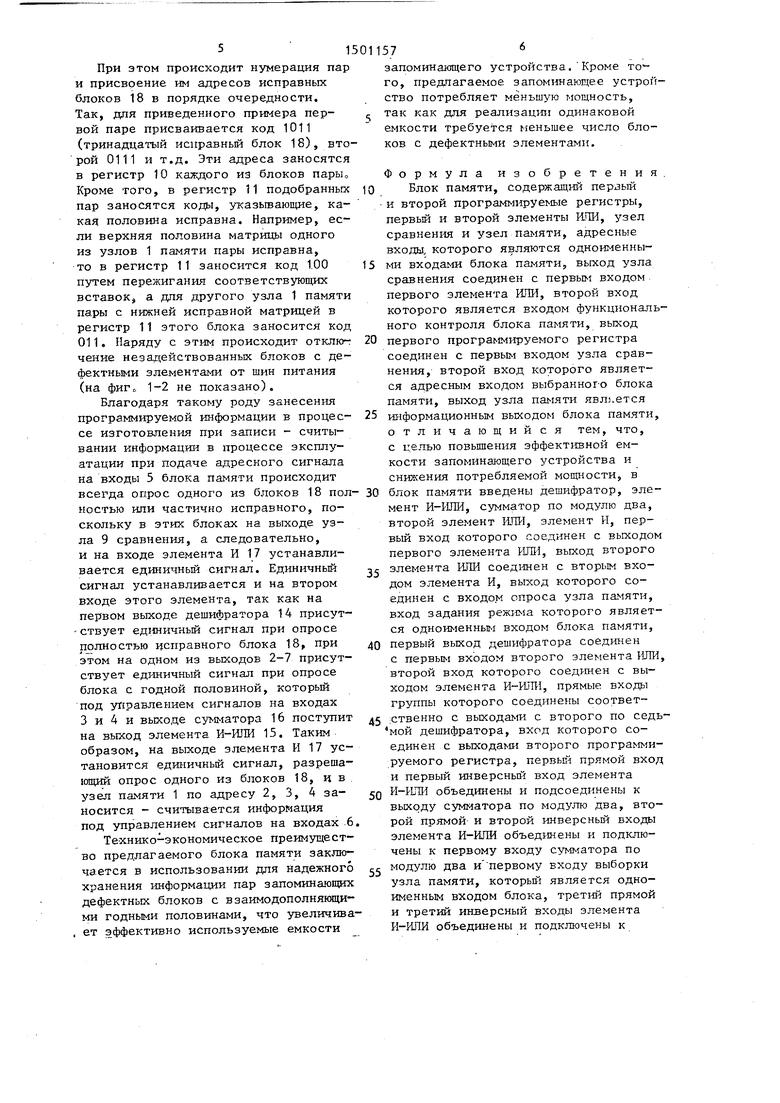

На фиг, 2 изображено соединение блоков памяти 18 в единое запоминающее, устройство.

Устройство работает следующим образоМо

При изготовлении до пережигания вставок в регистрах 10 и 11 происходит вначале функциональньй контроль исправности каждого из блоков 18 путем подачк на вход 7 соответствующего блока единичного сигнала и сигналов на входы 2, 3, 4и6, При этом, поскольку второй программируемый регистр 11 не запрограммирован, то на его выходах присутствуют нулевые сигналы, а на первом выходе дешифратора 14 единичный сигнал. Следовательно, на выходах первого и второго элементов ШШ 12, 13 на выходе элемента И 17. установится единичный сигнал. Благодаря этому на выходе 8 блока памяти считывается сигнал с выхода соответствующего узла 1 памяти. В это время остальные все блоки 18 не опрашиваются (закрыты), так как на выходе элемента 17 этих блоков присутствует нулевой сигнал, который удерживает узлы 1 памяти в закрытом состоянии,

В зависимости от исправности опрашиваемых блоков 18 программируемые регистры 10 и 11 блоков 18 заносится информация следующим образом.

Вначале поочередно проверяется исправность всех блоков 18, Блоки 18 называют исправными, если в соответствующих узлах 1 памяти не содержйтся дефектных элементов или они заменены внутренним резервом узла памяти. При исправности соответствующего блока 18 в регистр 10 заносится код адреса этого блока (в порядке очередности следования исправных блоков), Например, если необходимо собрать запоминающее устройство из 16-ти блоков 18, то адресные входы 5 состоят из четырех линий. Тогда при определении первого исправного блока 18 ему присваивается код 1000 и пережигаются соответствующие вставки в регистре 10, настраивающие блок 18 на этот код. При определении следующего исправного блока 18 в регистр 10 этого блока заносится уже код 0100 и т,д. При этом регистры 11 этих блоков не программируются, т.е. находятся в исходном нулевом состоянии.

Пусть например в запоминающем устройстве исправных блоков 18 оказалось двенадцать, т,е, последнему из исправных блоков 18 присвоен номер 0011, который хранится в регистре 10 этого блока.

5

0

5

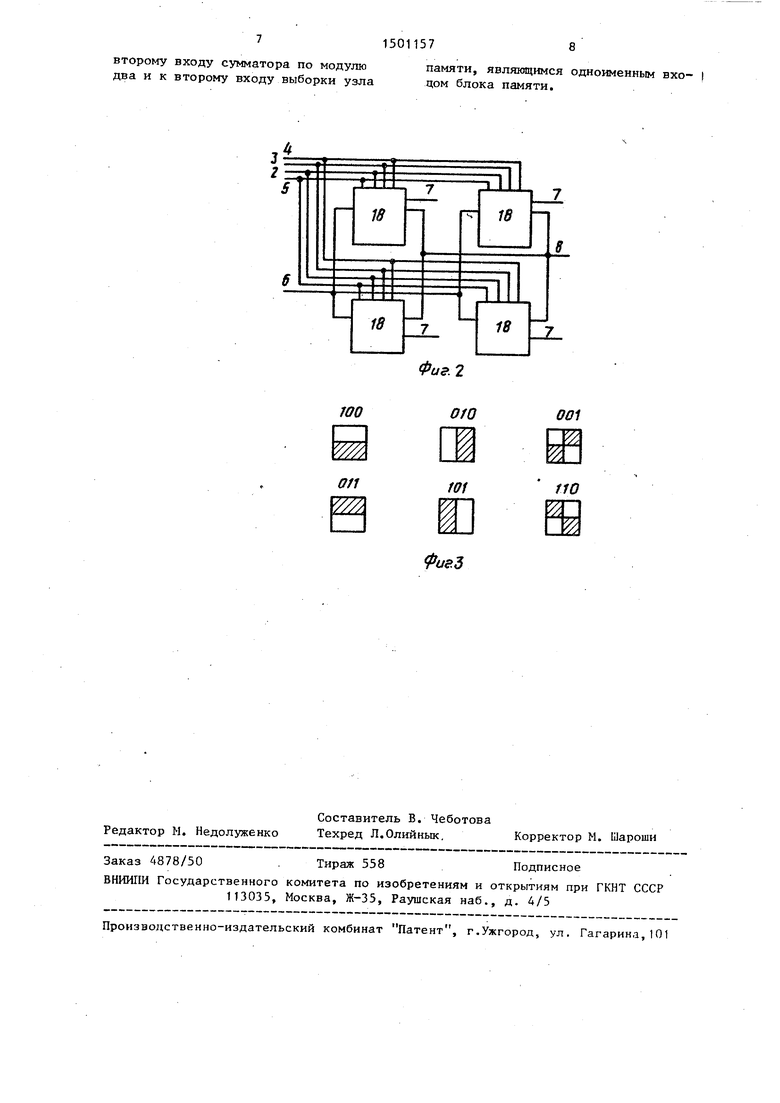

Одновременно с проверкой исправности блоков 18 в память контролирующей установки (на фиг, 1-3 не показана), осуществляющей функциональньй контроль, заносятся адреса де- фектньк блоков 18, у которых половина матрицы исправна, и, кроме того, заносится код, указывающий, какая из половин исправна (фиг, 3) Далее установка определяет пары дефектных блоков, у которых годные половины дополняют друг друга до полностью годного блока. Б соответствии с фиг. 3 таких пар может быть три, Таких блоков достаточно много, поскольку дефекты, как правило, группируются ,

5 При этом происходит нумерация пар и присвоение им адресов исправных блоков 18 в порядке очередности. Так, дпя приведенного примера первой паре присваивается код 1011 (тринадцатый исправньй блок 18), второй 0111 и т.д. Эти адреса заносятся в регистр 10 каждого из блоков парыо Кроме того, в регистр 11 подобранных пар заносятся коды, указывающие, какая половина исправна. Например, если верхняя половина матрицы одного из узлов 1 памяти пары исправна, то в регистр 11 заносится код 1.00 путем пережигания соответствующих вставок, а дпя другого узла 1 памяти пары с нижней исправной матрицей в регистр 11 этого блока заносится код 011. Наряду с этим происходит отклю-г чение незадействованных блоков с де- фектньми элементами от шин питания (на фиГе, 1-2 не показано).

Благодаря такому роду занесения программируемой информации в процес- се изготовления при записи - считывании информации в процессе эксплуатации при подаче адресного сигнала на входы 5 блока памяти происходит всегда опрос одного из блоков 18 пол ностью или частично исправного, поскольку в этих блоках на выходе узла 9 сравнения, а следовательно, и на входе элемента И 17 устанавливается единичньй сигнал. Единичный сигнал устанавливается и на втором входе этого элемента, так как на первом выходе дешифратора 14 присут- -ствует единичный сигнал при опросе полностью исправного блока 18, при этом на одном из выходов 2-7 присутствует единичный сигнал при опросе блока с годной половиной, который под управлением сигналов на входах 3 и 4 и выходе сумматора 16 поступит на выход элемента И-ИЛИ 15. Таким образом, на выходе элемента И 17 установится единичный сигнал, разреша- 1СЩИЙ опрос одного из блоков 18, ив узел памяти 1 по адресу 2, 3, 4 за- носится - считывается информация под управлением сигналов на входах .6 Те-хнико-экономическое преимущество предлагаемого блока памяти заключается в использовании для надежного хранения информахщи пар запоминающих дефектных блоков с взаимодополняющими годными половинами, что увеличивает эффективно используемые емкости

0

5 0 д 0

5

1576

запоминающего устройства, Кроме го, предлагаемое запоминающее устройство потребляет меньшую мощность, так как для реализации одинаковой емкости требуется меньшее число блоков с дефектными элементами.

Формула изобретения. Блок памяти, содержащий первый

и второй программируемые регистры, первый и второй элементы ИПИ, узел сравнения и узел памяти, адресные входы, которого являются одноименными входами блока памяти, выход узла сравнения соединен с первым входом первого элемента ИЛИ, второй вход которого является входом функционального контроля блока памяти, выход первого программируемого регистра соединен с первым входом узла сравнения, второй вход которого является адресным входом выбранног-о блока памяти, выход узла памяти информационным выходом блока памяти, отличающийся тем, что, с целью повьш1ения эффективной емкости запоминающего устройства и потребляемой мощности, в блок памяти введены дешифратор, элемент И-ЩМ, сумматор по модулю два, второй элемент ИПИ, элемент И, первый вход которого соединен с выходом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с вторым входом элемента И, выход которого соединен с входом опроса узла памяти, вход задания реж1ма которого является одноименны-j входом блока памяти, первый выход дешифратора соединен с первым входом второго элемента ИЛИ, второй вход которого соед1.шен с выходом элемента И-РШИ, прямые входы группы которого соединены соответ- :ственно с выходами с второго по седь мой дешифратора, вход которого соединен с выходами второго программируемого регистра, первьы прямой вход и первый инверсный вход элемента И-РШИ объединены и подсоединены к выходу сумматора по модулю два, второй прямой и второй инверсный входы элемента И-ИЛИ объединены и подключены к первому входу сумматора по модулю два и первому входу выборки узла памяти, который является одноименным входом блока, третий прямой и третий инверсный входы элемента И-ИЛИ объединены и подключены к

второму входу сумматора по модулю два и к второму входу выборки узла

памяти, являющимся одноименным вхо- цом блока памяти.

| Запоминающее устройство с коррекцией информации | 1981 |

|

SU957273A1 |

| Запоминающее устройство | 1983 |

|

SU1107177A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-08-15—Публикация

1988-02-29—Подача