315

Изобретение относится к вычислительной технике и может быть использовано для управления регенерацией информации в динамической памяти.

Цель изобретения - повышение быстродействия устройства.

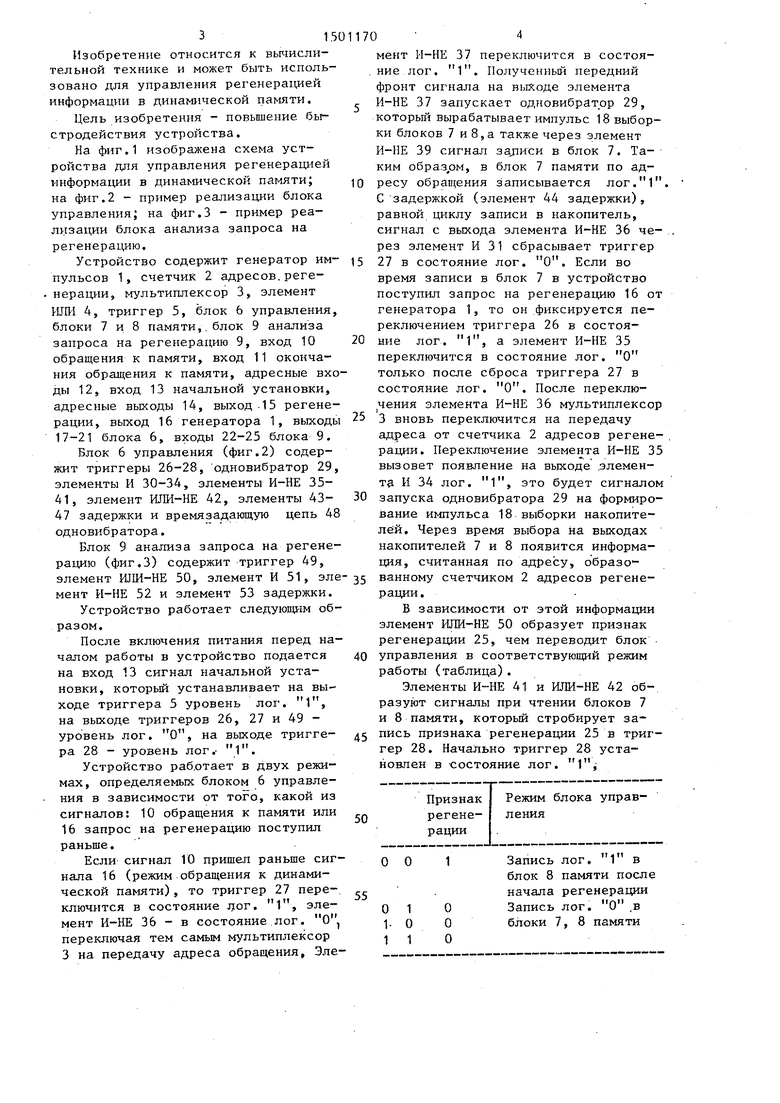

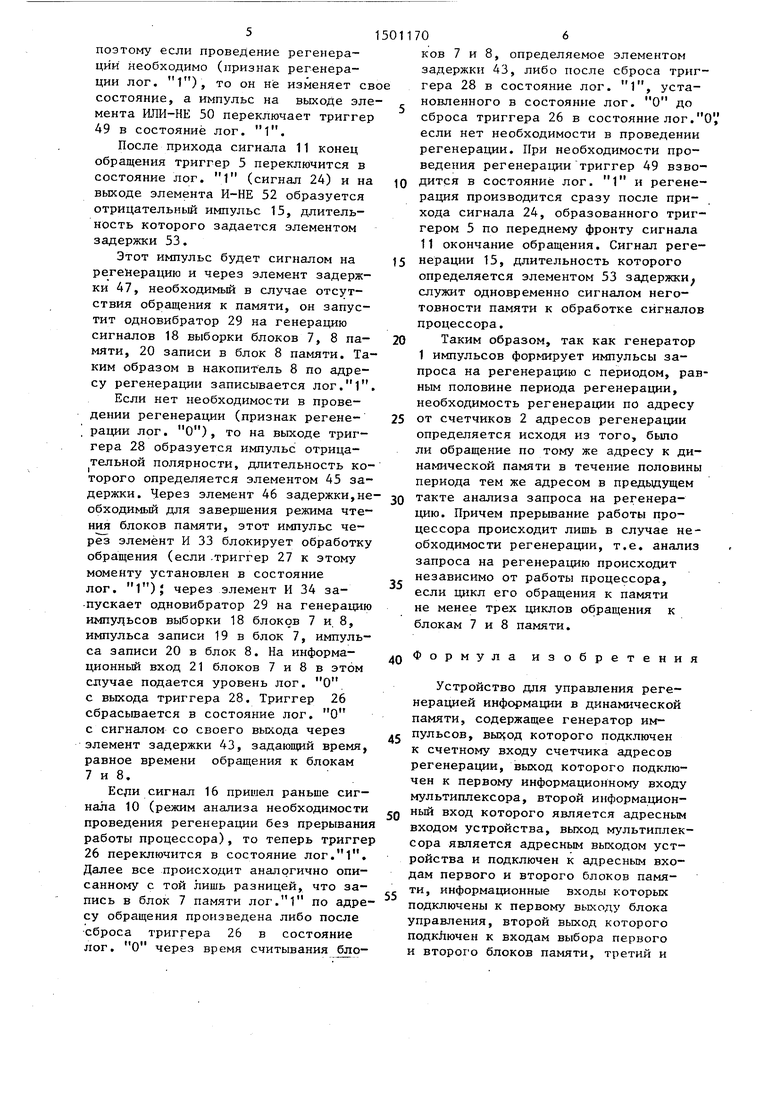

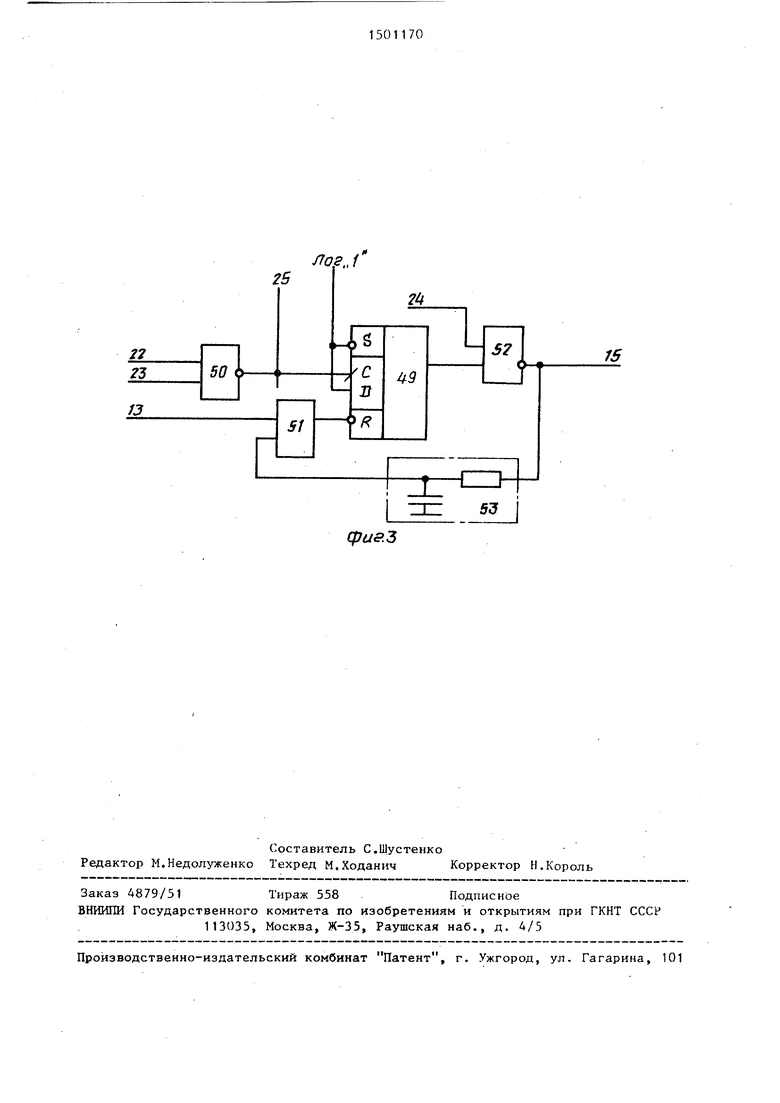

На фиг,1 изображена схема устройства для управления регенерацией информации в динa шчecкoй памяти; на фиг.2 - пример реализации блока управления; на фиг.З - пример реализации блока анализа запроса на регенерацию.

Устройство содержит генератор импульсов 1, счетчик 2 адресов.регенерации, мультиплексор 3, элемент ШШ 4, триггер 5, блок 6 управления, блоки 7 и 8 памяти,, блок 9 анализа запроса на регенерацию 9, вход 10 обращения к памяти, вход 11 окончания обращения к памяти, адресные входы 12, вход 13 начальной установки, адресные выходы 14, выход-15 регенерации, выход 16 генератора 1, выходы 17-21 блока 6, входы 22-25 блока 9. Блок 6 управления (фиг.2) содержит триггеры 26-28, одновибратор 29, элементы И 30-34, элементы И-НЕ 35- 41, элемент ШШ-НЕ 42, элементы 43- 47 задержки и времязадающую цепь 48 одновибратора.

Блок 9 анализа запроса на регенерацию (фиг.З) содержит триггер 49, элемент ШШ-НЕ 50, элемент И 51, элемент И-НЕ 52 и элемент 53 задержки.

Устройство работает следуюпщм образом.

После включения питания перед началом работы в устройство подается на вход 13 сигнал начальной установки, которьй устанавливает на выходе триггера 5 уровень лог. 1, на выходе триггеров 26, 27 и 49 - уровень лог, О, на выходе триггера 28 - уровень лог.- 1.

Устройство работает в двух режимах, определяемых блоком 6 управления в зависимости от того, какой из сигналов: 10 обращения к памяти или 16 запрос на регенерацию поступил раньше,

Если сигнал 10 пришел раньше сигнала 16 (режим обращения к динамической памяти), то триггер 27 переключится в состояние лог. 1, элемент И-НЕ 36 - в состояние лог,

О

переключая тем самым мультиплексор 3 на передачу адреса обращения, Эле4

мент И-НЕ 37 переключится в состоя- ние лог, 1, Полученный передний фронт сигнала на выходе элемента

И-НЕ 37 запускает одновибратор 29, которьй вырабатывает импульс 18 выборки блоков 7 и 8, а также через элемент И-НЕ 39 сигнал залчиси в блок 7. Таким образцом, в блок 7 памяти по адресу обращения записывается лог.1. С задержкой (элемент 44 задержки), равной циклу записи в накопитель, сигнал с выхода элемента И-НЕ 36 через элемент И 31 сбрасывает триггер

27 в состояние лог. О. Если во время записи в блок 7 в устройство поступил запрос на регенерацию 16 от генератора 1, то он фиксируется переключением триггера 26 в состояние лог, 1, а элемент И-НЕ 35 переключится в состояние лог, О только после сброса триггера 27 в состояние лог, О, После переключения элемента И-НЕ 36 мультиплексор

3 вновь переключится на передачу

адреса от счетчика 2 адресов регенерации. Переключение элемента И-НЕ 35 вызовет появление на вькоде .элемента И 34 лог, 1, это будет сигналом

запуска одновибратора 29 на формирование импульса 18 выборки накопителей. Через время выбора на выходах накопителей 7 и 8 появится информация, считанная по адресу, образованному счетчиком 2 адресов регенерации ,

В зависимости от этой информации элемент ИЛИ-НЕ 50 образует признак регенерации 25, чем переводит блок

управления в соответствующий режим работы (таблица),

Элементы И-НЕ 41 и ИЛИ-НЕ 42 образуют сигналы при чтении блоков 7 и В памяти, который стробирует запись признака регенерации 25 в триггер 28. Начально триггер 28 установлен в -состояние лог,

5

0 О

01 1- О

11

О О О

Запись лог, 1 в блок 8 памяти после начала регенерации Запись лог. О .в блоки 7, 8 памяти

поэтому если проведение регенерации необходимо (признак регенерации лог. 1), то он не изменяет свое

состояние, а импульс на выходе элемента ИЛИ-НЕ 50 переключает триггер 49 в состояние лог. 1.

После прихода сигнала 11 конец обращения триггер 5 переключится в состояние лог. 1 (сигнал 24) и на выходе элемента И-НЕ 52 образуется отрицательный импульс 15, длительность которого задается элементом задержки 53.

Этот импульс будет сигналом на регенерацию и через элемент задержки 47, необходимый в случае отсутствия обращения к памяти, он запустит одновибратор 29 на генерацию сигналов 18 выборки блоков 7, 8 па- мяти, 20 записи в блок 8 памяти. Таким образом в накопитель 8 по адресу регенерации записывается лог. Ч

Если нет необходимости в проведении регенерации (признак регене- рации лог. О), то на выходе триггера 28 образуется импульс отрица- тельной полярности, длительность которого определяется элементом 45 задержки. Через элемент 46 задержки,не обходимьш для завершения режима чтения блоков памяти, этот импульс через элемент И 33 блокирует обработку обращения (если .триггер 27 к этому моменту установлен в состояние лог. 1)5 через элемент И 34 за- пускает одновибратор 29 на генерацию импудьсов выборки 18 блоков 7 и 8, импульса записи 19 в блок 7, импульса записи 20 в блок 8. На информа- ционный вход 21 блоков 7 и 8 в этом случае подается уровень лог. О с выхода триггера 28. Триггер 26 сбрасьшается в состояние лог. О с сигналом со своего выхода через элемент задержки 43, задающий время, равное времени обращения к блокам 7 и 8.

сигнал 16 пришел раньше сигнала 10 (режим анализа необходимости проведения регенерации без прерывани работы процессора), то теперь тригге 26 переключится в состояние лог. М. Далее все происходит аналогично описанному с той лишь разницей, что запись в блок 7 памяти лог. М по адресу обращения произведена либо после сброса триггера 26 в состояние лог. О через время считывания бло

ое

о

15011706

ков 7 и 8, определяемое элементом задержки 43, либо после сброса триггера 28 в состояние лог. 1, установленного в состояние лог. О до сброса триггера 26 в состояние лог. если нет необходимости в проведении регенерации. При необходимости проведения регенерации триггер 49 взвоо

5 0

5 Q ..

-

5

5

дится в состояние лог. 1 и регенерация производится сразу после прихода сигнала 24, образованного триггером 5 по переднему фронту сигнала 11 окончание обращения. Сигнал регенерации 15, длительность которого определяется элементом 53 задержки; служит одновременно сигналом неготовности памяти к обработке сигналов процессора.

Таким образом, так как генератор 1 импульсов формирует импульсы запроса на регенерацию с периодом, равным половине периода регенерации, необходимость регенерации по адресу от счетчиков 2 адресов регенерации определяется исходя из того, было ли обращение по тому же адресу к динамической памяти в течение половины периода тем же адресом в предыдущем такте анализа запроса на регенерацию. Причем прерьшание работы процессора происходит лишь в случае необходимости регенерации, т.е. анализ запроса на регенерацию происходит независимо от работы процессора, если цикл его обращения к памяти не менее трех циклов обращения к блокам 7 и 8 памяти.

Формула изобретения

Устройство для управления регенерацией информации в динамической памяти, содержащее генератор импульсов, которого подключен к счетному входу счетчика адресов регенерации, выход которого подключен к первому информационному входу мультиплексора, второй информационный вход которого является адресным входом устройства, выход мультиплексора является адресным выходом устройства и подключен к адресным входам первого и второго блоков памяти, информационные входы которых подключены к первому выходу блока управления, второй выход которого подключен к входам выбора первого и второго блоков памяти, третий и

четвертый выходы блока управления подключены к входам записи соответственно первого и второго блоков памяти, пятый выход блока управления к управляющему входу мультиплексора, вход синхронизадаи блока управления - к выходу генератора импульсов, вход признака обращения к памяти и вход начальной установки блока управления являются соответственно одноименными входами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит блок анализа запроса регенера ции, триггер и элемент ИЛИ, первьй вход которого является входом конца обращения устройства, второй вход элемента ИЛИ подключен к входу при™

знака обращения к памяти блока уп равления, выход элемента ИЛИ - к входу сброса триггера, вход установки которого подключен к входу начальной установки блока управления и к первому входу блока анализа запроса регенерации, первьй выход которого является выходом требования регенерации устройства и подключен к входу регенерации блока управления, вход признака регенерации которого подключен к второму выходу блока анализа запроса регенерации, второй и третий входы которого подключены к информационным выходам соответственно первого и второго блоков памяти, четвертьй вход блока анализа запроса регенерации подключен к выходу триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для счета количества изображений объекта | 1987 |

|

SU1494021A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ МАГИСТРАЛЕЙ | 1990 |

|

RU2017210C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Устройство для выделения фигур на изображении | 1984 |

|

SU1287203A1 |

| Устройство для анализа частоты использования блоков информации в вычислительных комплексах | 1990 |

|

SU1793442A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1985 |

|

SU1374280A1 |

Изобретение относится к вычислительной технике и может быть использовано для управления регенерацией информации в динамической памяти. Целью изобретения является повышение быстродействия устройства. Устройство содержит генератор 1 импульсов, счетчик 2 адресов регенерации, мультиплексор 3, элемент ИЛИ 4, триггер 5, блок 6 управления, блоки 7 и 8 памяти,блок 9 анализа запроса регенерации. Анализ необходимости проведения регенерации информации в устройстве происходит во время обработки обращения к памяти без прерывания работы процессора. Генератор 1 формирует импульсы запроса регенерации с периодом, равным половине периода регенерации. Необходимость регенерации по текущему адресу (счетчик 2) определяется отсутствием обращения по этому адресу в течение половины периода распределенной регенерации и регистрации строки с тем же адресом в предыдущем такте анализа запроса регенерации. Прерывание работы процессора происходит лишь в случае необходимости регенерации памяти. 3 ил.

S.-«J

1В

Лог, f

сриг.З

| Патент США № 3737879, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1985 |

|

SU1374280A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-08-15—Публикация

1987-11-13—Подача