третий элементы И, элемент ИЛИ, первый и второй инверторы, причем третий вход первого элемента И соединен с вторым входом второго элемента И, первым входом третьего триггера и является первым входом блока управления, первый и второй входы первого элемента И и первый вход элемента ИЛИ являются соответственно третьим, вторым и четвертым входами блока yir- равления, первый вход второго элемента И соединен с первым входом третьего элемента И и является пятым входом блока управления, выход первого инвертора подключен к первому и второму входам первого триггера, выход третьего элемента И подключен к третьим входам первого и второго триггеров, четвертые входы которых соединены с выходом первого элемента

И, первый и второй входы второго триггера подключены к инверсному вьгходу первого триггера, прямой и инверсный выходы второго триггера соединены соответственно с вторым входом элемента ИЛИ и вторым входом третьего триггера, инверсный выход которого подключен к второму входу третьего элемента И, выход элемента ИЛИ подключен к входу второго инвертора, вход первого инвертора соединен с шиной нулевого потенциала, выход второго элемента И подключен к третьему входу третьего триггера, выходы второго инвертора, элемента К1Ш, прямой выход первого триггера, выход второго элемента И являются соответственно первым, вторым, третьим четвертым и пятым выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1987 |

|

SU1501170A1 |

| Динамическое запоминающее устройство с восстановлением информации | 1989 |

|

SU1689990A1 |

| Динамическое запоминающее устройство и формирователь синхросигналов для него | 1980 |

|

SU936030A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1088066A1 |

| Устройство для регенерации динамической памяти | 1980 |

|

SU943845A1 |

| Блок управления для запоминающего устройства | 1977 |

|

SU723679A1 |

| Динамическое запоминающее устройство | 1987 |

|

SU1474739A1 |

| Устройство для управления оперативной динамической памятью | 1987 |

|

SU1481850A1 |

1

Изобретение относится к вычислительной технике и может быть использовано для управления регенерацией информация в динамической памяти.

Целью изобретения является сокращение времени регенерации за счет исключения избыточных циклов принудительной регенерации.

На фиг.1 изображено устройство для управления регенерацией информации в динамической памяти; на фиг.2 - блок управления; на фиг. 3 - первый формирователь импульсов.

Устройство содержит блок 1 управления, генератор 2 импульсов, первый формирователь 3 импульсов, счетчик 4 адреса, мультиплексор 5, первый 6 и второй 7 накопители, элемент ИЛИ-НЕ 8, элемент И9, триггер 10, второй формирователь 11 импульсов, элемент И-НЕ 12, вход 13 синхронизации, вход 14 начальной установки, входы 15 - 18 синхронизации, адресные входы 19, адресные выходы 20, выход 21 регенерации и выход 22 синхронизации.

Блок 1 управления по входу 23 подключен к выходу генератора 2 импульсов, а, выходы 24-28 соединены с соответсТвующими входами выборки накопителей 6 и 7. Формирователь 3 формирует сигнал 29 Пуск разрешения работы блока 1 управления и имеет вход 30 сброса запроса регенерации.

Блок 1 управления (фиг.2) содержит шину 31 нулевого потенциала устройства, элементы И 32-34, триггеры 35-37, элемент ШШ 38, инверторы 39 и 40. Формирователь 3 (фиг.З) содержит элемент И 41, формирователь 42 импульсов, элемент И-НЕ 43, инвертор 44, триггеры 45-47.

Устройство работает в двух режимах, определяемых формирователем 3 в зависимости от того, какой из сигналов 17 Синхронизация задатчика от процессора (СХЗ) или 23 (от генератора 2) поступил раньше.

Если сигнал 17 пришел раньше сигнала 23 (режим обращения к динамической памяти), то D-триггер 47 остает ся в состоянии 1 и сигнал 17 СХЗ 5 через элемент 4I поступает на С-вход D-триггера 15, который при наличии сигнала 16 Выбор ОЗУ, переключает D-триггер 45 в состояние Г , что запрещает работу блока 1 управления, так как сигнал .29 Пуск становится

0

0

логическим О,

3

При окончании цикла обращения и динамической памяти на вход ЕНтригге ра 45 поступает импульсный сигнал 18 (логический О), которьй устанавливает D-триггер 45 в состояние О, что разрешает работу блока 1 управления. При этом-D-триггер 46 устанавливается в 1 и на выходе блока 3 появляется сигнал 22 Синхронизация исполнителя (СХИ), свидетельствующий об окончании цикла взаимодей- ствия динамической памяти с процессором. Сигнал 22 СХИ сбрасывается при снятии процессором сигнала 17 СХЗ.

Если сигнал 23 запроса на регенерацию пришел раньше сигнала 17 СХЗ, то триггер 47 устанавливается в состояние О, что запрещает прохождение сигнала 17 СХЗ через элемент 41 и разрешает работу блока 1 управления. При этом, если анализ запроса на регенерацию привел к pere нерации, то сигнал 30 на время ре- генерации становится равным логическому о, т.е. D-триггер 47 переключается в 1 и разрешает прохождение сигнала 17 СХУ только после

того, как сигнал 30 станет снова 1 Если анализ запроса на регенерацию не привел к регенерации, сигнал 30 остается в состоянии логической l. D-триггер 47 переключается в 1 через время анализа запроса регенерации, определяемого RS-цепочкой, и разрешает прохождение сигнала 17 СХЗ. Этот режим работы называется режимом анализа запроса на регенерацию.

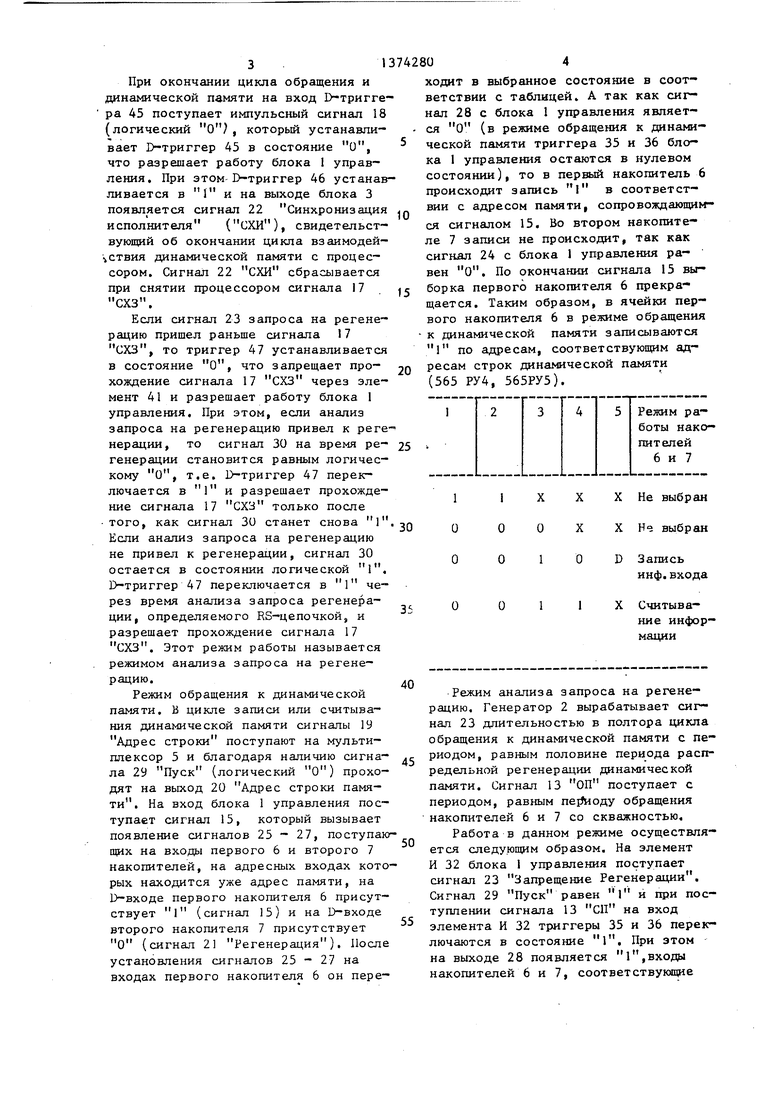

Режим обращения к динамической памяти. В цикле записи или считывания динамической памяти сигналы 1У Адрес строки поступают на мультиплексор 5 и благодаря наличию сигнала 29 Пуск (логический О) проходят на выход 20 Адрес строки памяти. На вход блока 1 управления поступает сигнал 15, который вызывает появление сигналов 25 - 27, поступаю ш;их на входы первого 6 и второго 7 накопителей, на адресных входах которых находится уже адрес памяти, на D-входе первого накопителя 6 присутствует 1 (сигнал 15) и на 1 -входе второго накопителя 7 присутствует О (сигнал 21 Регенерация). После установления сигналов 25 - 27 на входах первого накопителя 6 он пере0

5

5

0

ходит в выбранное состояние в соответствии с таблицей. А так как сигнал 28 с блока 1 управления является о (в режиме обращения к динамической памяти триггера 35 и 36 блока 1 управления остаются в нулевом состоянии), то в первый накопитель 6 происходит запись I в соответствии с адресом памяти, сопровождающимся сигналом 15. Во втором накопителе 7 записи не происходит, так как сигнал 24 с блока 1 управления равен о. По окончании сигнала 15 выборка первого накопителя 6 прекращается. Таким образом, в ячейки первого накопителя 6 в режиме обращения к динамической памяти записываются 1 по адресам, соответствующим адресам строк динамической памяти (565 РУ4, 565РУ5).

1

О О

i

О

X

D

Не выбран Не выбран

Запись инф.входа

Считывание информации

Режим анализа запроса на регенерацию. Генератор 2 вырабатывает сигнал 23 длительностью в полтора цикла обращения к динамической памяти с периодом, равным половине периода расп- редельной регенерации динамической памяти. Сигнал 13 ОП поступает с периодом, равным периоду обращения накопителей 6 и 7 со скважностью.

Работа в данном режиме осуществляется следующим образом. На элемент И 32 блока 1 управления поступает сигнал 23 Запрещение Регенерации. Сигнал 29 Пуск равен 1 и при поступлении сигнала 13 СП на вход элемента И 32 триггеры 35 и 36 переключаются в состояние l. При этом на выходе 28 появляется 1,входы накопителей 6 и 7, соответствукяпре

выходам 25 - 27, активизируются аналогично режиму обращения при поступлении сигнала 15, только из-за сигнала 28 в соответствии с таблицей накопители 6 и 7 переходят в состояние считывания. При этом адрес анализа регенерации через мультиплексор 5 под управлением сигнала 29 Пуск подается со счетчика 4 адреса. Если по адресу регенерации хотя бы в одном из накопителей находится 1, то на

выходе элемента ИЛИ-НЕ 8 в режиме считывания ничего не изменится и триггер 10 останется в состоянии логического о. Следующий импульс 13 ОП переключает триггер 36 в состояние О и на выходе 28 блока 1 управления появляется О, что вызывает

10

15

копителей, то на выходе элемента 8 появляется 1, которая переключает триггер 10 в состояние логической l, что вызывает появление на вых де 21 сигнала Регенерация длител ностью, определяемой RC-цепочкой, которому Происходит регенеращия ст ки динамической памяти, определяем текущим состоянием счетчика 4. Следующий импульс 13 ОП переключает триггер 35 в состояние О и на выходе 28 блока 1 управления появляе ся О, что вызывает режим записи (см. таблицу) в накопители 6 и 7, так как триггер Зь не переключается и выходы 25-27 сохраняют состояние предыдущего такта поступления сигнала 13 ОП. При этом в первый

режим записи (см.таблицу) в накопите-20 накопитель 6 по-адресу регенерации

записывается О, так как сигнал 1 отсутствует, а во второй накопитель 7 записывается 1, так как на выхо де триггера 10 появилась 1 (сигна 21 Регенерация стал активным).Тре тий импульсный сигнал 13 ОП перек лючает триггеры 35 и 36 соответстве но в 1 и О, а так как инверсны выход триггера 36 связан с С-входом триггера 37, то на инверсном выходе триггера 37 появляется О, который обнуляет триггеры 35 и 36, что запр щает обращение к первому 6 и втором 7 накопителям. Сигнал обнуления дер жится до окончания сигнала 23 Запр щение Регенерации, поэтому последующие импульсные сигналы 13 ОП н вызовут переключения триггеров 35 и 36. Схема переходит в режим обращения к динамической памяти, если в течение двух тактов ОП на устройство прищли сигналы 16 Выбор ОЗУ и 17 СХЗ, а также закончилось дей ствие сигнала 21 Регенерация.

ли 6 и 7, так как триггер 36 не переключается и выходы 25 - 27 срхра- няют состояние предыдущего такта поступления сигнала 13 ОП. При этом в первый накопитель 6 по адресу регенерации записывается О, так как сигнал 15 отсутствует, во второй накопитель 7 записывается также О, так как на выходе триггера 10 сохраняется О, Третий импульсный сигнал 13 он переключает триггеры 35 и 36 соответственно в 1 и О, а так как инверсный выход триггера 36 связан с С-входом триггера 37, то на инверсном выходе триггера 37 появляется о, который обнуляет триггеры 35 и 36, что запрещает обращение к первому 6 и второму 7 накопителям. Сигнал обнуления держится до око-нча- ния сигнала 23 Запрет Регенерации, поэтому последующие импульсные сигналы ОП не вызовут переключения триггеров 35 и 36. Если в этом случае на устройство в течение двух тактов ОП поступили сигналы 16 Выбор ОЗУ и 17 СХЗ, то схема переходит в режим обращения к динамической памяти.

Если же при поступлении первого сигнала 13 ОП в режиме анализа запроса на регенерацию по адресу регенерации, поступившему на первый 6 и второй 7 накопители со счетчика 4 адреса, не происходит считывание 1 ни из первого 6, ни из второго 7 на-

5

копителей, то на выходе элемента 8 появляется 1, которая переключает триггер 10 в состояние логической l, что вызывает появление на выхр- де 21 сигнала Регенерация длительностью, определяемой RC-цепочкой, по которому Происходит регенеращия стро ки динамической памяти, определяемой текущим состоянием счетчика 4. Следующий импульс 13 ОП переключает триггер 35 в состояние О и на выходе 28 блока 1 управления появляется О, что вызывает режим записи (см. таблицу) в накопители 6 и 7, так как триггер Зь не переключается и выходы 25-27 сохраняют состояние предыдущего такта поступления сигнала 13 ОП. При этом в первый

0 накопитель 6 по-адресу регенерации

5

0

5

0

5

0

записывается О, так как сигнал 15 отсутствует, а во второй накопитель 7 записывается 1, так как на выхо де триггера 10 появилась 1 (сигнал 21 Регенерация стал активным).Третий импульсный сигнал 13 ОП переключает триггеры 35 и 36 соответствен- но в 1 и О, а так как инверсный выход триггера 36 связан с С-входом триггера 37, то на инверсном выходе триггера 37 появляется О, который обнуляет триггеры 35 и 36, что запрещает обращение к первому 6 и второму 7 накопителям. Сигнал обнуления держится до окончания сигнала 23 Запрещение Регенерации, поэтому последующие импульсные сигналы 13 ОП не вызовут переключения триггеров 35 и 36. Схема переходит в режим обращения к динамической памяти, если в течение двух тактов ОП на устройство прищли сигналы 16 Выбор ОЗУ и 17 СХЗ, а также закончилось действие сигнала 21 Регенерация.

Таким образом, необходимость регенерации или отсутствие таковой по текущему адресу регенерации динамической памяти, поступающему со счетчика 4, определяется исходя из того, было ли обращение по тому же адресу к динамической памяти в течение половины периода распределенной регенерации или имелась ли регенерация строки с тем же адресом в предыдущем такте анализа запроса на регенерацию.

(рае. 2

| Устройство для управления регенерацией информации в блоках динамической памяти | 1978 |

|

SU792290A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Исследование и разработка модульного полупроводникового оперативного устройства большой информационной емкости повышенной надежности | |||

| - Отчет МЭИ | |||

| Инв | |||

| № 6709598, 1978, с | |||

| Аппарат для испытания прессованных хлебопекарных дрожжей | 1921 |

|

SU117A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-15—Публикация

1985-03-18—Подача